AD9559双路PLL四通道输入多服务线路卡自适应时钟转换器技术手册

描述

概述

AD9559是一款低环路带宽时钟倍频器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。AD9559产生的输出时钟可以与多达四路外部输入参考时钟同步。DPLL可以降低与外部参考时钟相关的输入时间抖动或相位噪声。借助数字控制环路和保持电路,即使所有参考输入都失效,AD9559也能持续产生低抖动输出时钟。

数据表:*附件:AD9559双路PLL四通道输入多服务线路卡自适应时钟转换器技.pdf

应用

- 网络同步,包括同步以太网和OTN映射/解映射

- 清除基准时钟抖动

- 最高达到OC-192的SONET/SDH时钟,包括FEC

- Stratum 3保持、抖动清除及相位瞬态控制

- 无线基站控制器

- 有线基础设施

- 数据通信

特性

- 在保持模式下稳定性支持GR-1244 Stratum 3

- 支持平稳的参考切换,几乎不会干扰输出相位

- 支持Telcordia GR-253抖动产生、转换和容差,适用于SONET/SDH至OC-192系统

- 支持ITU-T G.8262同步以太网从时钟

- 支持ITU-T G.823、G.824、G.825和G.8261

- 自动/手动保持和参考切换

- 自适应时钟可动态调整反馈分频器,用于OTN映射/解映射应用

- 双通道数字PLL架构,带四个基准输入电压(单端或差分)

- 4x2交叉点允许任意基准输入驱动任意PLL

- 输入参考频率范围:2 kHz至1250 MHz

- 参考验证和频率监控(2 ppm)

- 欲了解更多特性,请参考数据手册

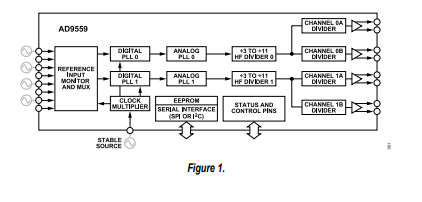

框图

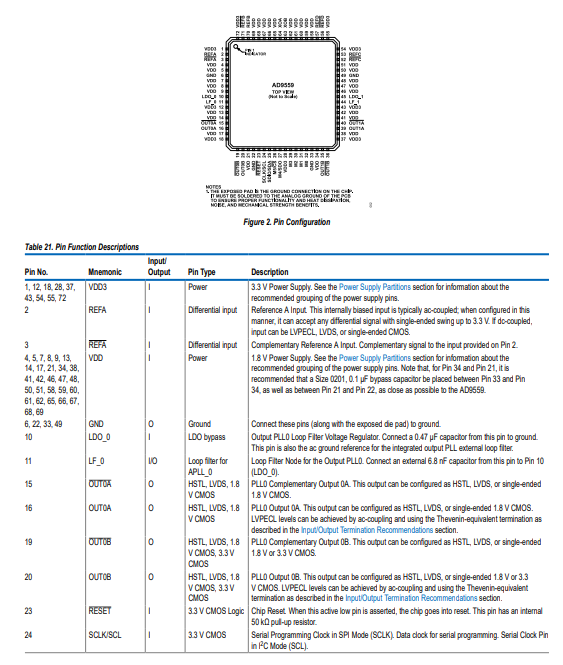

引脚配置描述

典型性能特征

操作理论

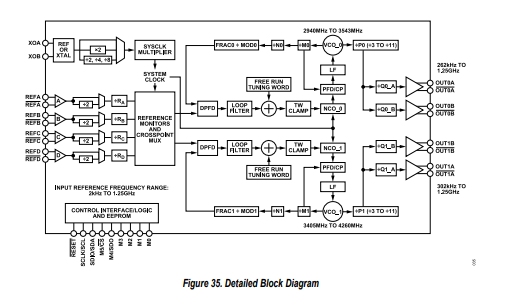

AD9559提供的时钟输出与所选(活动)参考的相位和频率直接相关,但其抖动特性由系统时钟控制,而系统时钟可通过数控振荡器(DCO)以及模拟锁相环(APLL)进行控制。

可以将AD9559看作是在一个封装内集成了两个AD9557,由一个4:2交叉开关控制参考输入。AD9559支持多达125种参考输入和输入频率,范围从2kHz到250MHz。该产品包含两个数字锁相环(DPLL)。每个DPLL都有一个可编程数字低通滤波器,可大幅降低传输到活动输出端的抖动,并且这两个DPLL可以完全独立运行。AD9559支持手动和自动切换。虽然在掉电期间,AD9559会继续将输出保持为高电平,前提是系统时钟存在。保持输出频率是转换到参考开关前输出频率历史的一个时间平均值。如果活动参考降级或完全失效,该器件会激活手动和自动参考切换功能;在DPLL锁定时,允许用户动态更改时钟分频比。

AD9559包括一个系统时钟乘法器、两个DPLL和两个APLL。系统时钟首先进入DPLL,在这里进行抖动消除,并且大部分频率转换都在此完成。每个DPLL都有一个30位数控振荡器(DCO),可产生175MHz至200MHz范围内的信号。

DCO输出进入APLL,APLL将信号倍频至2.9GHz到4.2GHz的范围。然后,该信号进入时钟分配部分,时钟分配部分带有3分频至11分频的整数通道分频器(1分频至1024分频)。

XOA和XOB输入为系统时钟提供输入。这些位将10MHz至60MHz范围内的参考时钟映射到10MHz至50MHz的晶体连接,横跨XOA和XOB输入。系统时钟为频率仲裁器、DPLL和内部切换逻辑提供时钟。

AD9559上的每个APLL都有两个差分输出驱动器。四个输出驱动器中的每一个都有一个专用的10位可编程后置分频器。每个差分驱动器都可以配置为单端差分输出或双单端CMOS输出。时钟分配部分的工作频率高达1250MHz。

在差分模式下,输出驱动器采用1.8V电源供电,以实现高性能,同时功耗最低。

有两种不同的模式:LVDS模式和1.8V HSTL模式。电压摆幅与LVPECL兼容。如果需要LVPECL信号电平,设计人员可以交流耦合AD9559输出,并在目标端使用戴维南等效端接来驱动LVPECL输入。

在单端模式下,每个差分输出驱动器可以作为两个单端CMOS输出运行。OUTA、OUTB和OUT1A、OUT1B支持仅1.8V CMOS操作,而OUT0A、OUT0B支持1.8V或3.3V CMOS操作。

参考输入物理连接

四对引脚(REFA、REFA_REFD、REFB)为参考时钟接收器提供访问通道。为适应上升沿和下降沿较慢的输入信号,差分和单端输入接收器均具有滞后特性。滞后特性还可确保未连接或悬空的输入不会导致接收器振荡。

在配置为差分模式运行时,输入接收器可适应交流耦合或直流耦合输入。2.5V和3.3V LVPECL等效的接收器在内部进行直流耦合。可处理交流耦合操作,但内部无50Ω或100Ω端接。

配置为单端操作时,输入接收器呈现47kΩ(典型值)的下拉负载。用户可编程阈值摆幅电压范围为3种,用于每个单端接收器。有关设置,请参见寄存器0x0300至寄存器0x037A。

-

AD9554:高性能多服务线路卡自适应时钟转换器2026-03-23 148

-

AD9554-1四路PLL、四通道输入、四通道输出多服务线路卡自适应时钟转换器技术手册2025-04-10 1069

-

EVAD9559 AD9559 评估板2021-06-08 671

-

AD9559:双PLL、四输入、多服务线路卡自适应时钟转换器产品手册2021-05-26 697

-

AD9542:四输入、五输出、双DPLL同步器和自适应时钟转换器产品手册2021-05-08 866

-

AD9558:带帧同步数据表的四输入多业务线卡自适应时钟转换器2021-04-30 690

-

AD9557:双路输入多服务线路卡自适应时钟转换器2021-03-21 658

-

低环路带宽时钟倍频器AD9559/PCBZ2019-02-28 2337

-

多业务线卡自适应时钟转换器评估板AD9554/PCBZ2019-02-22 1799

-

AD9559 双路PLL四通道输入多服务线路卡自适应时钟转换器2019-02-15 712

-

双锁相环四输入多行卡自适应时钟转换器ad9559数据表2017-10-19 829

-

ADI推出完全可编程的抖动衰减双路时钟转换器IC--AD95592012-08-03 5187

全部0条评论

快来发表一下你的评论吧 !