AD9577带双路PLL、扩频和余量微调功能的时钟发生器技术手册

描述

概述

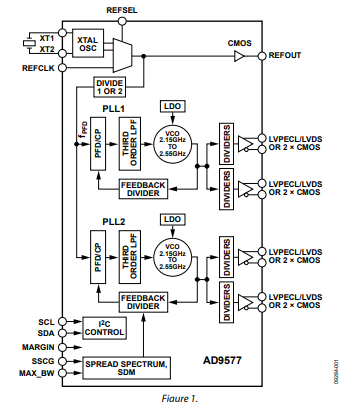

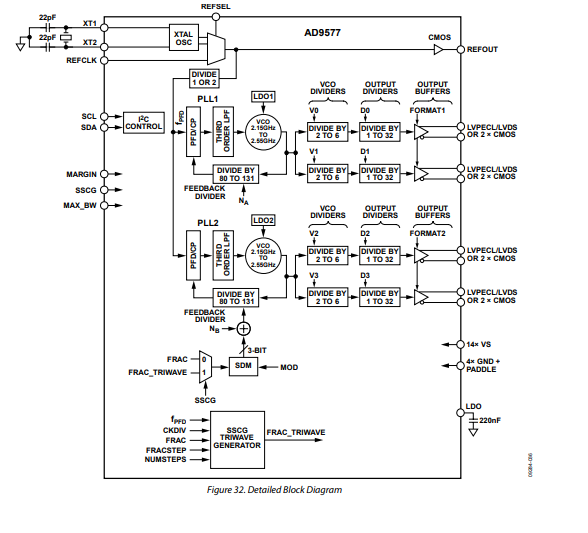

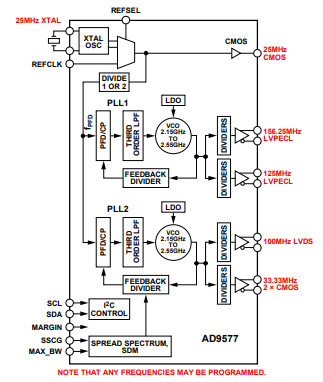

AD9577既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系列,确保实现较高的网络性能。PLL具有I^2^C 可编程输出频率和格式。小数N分频PLL可支持扩频时钟功能,降低EMI辐射的峰值功率。两个PLL均可支持频率余量微调功能。

数据表:*附件:AD9577带双路PLL、扩频和余量微调功能的时钟发生器技术手册.pdf

第一个整数N分频PLL部分(PLL1)由一个鉴频鉴相器(PFD)、一个电荷泵(CP)、一个低噪声电压控制振荡器(VCO)、一个可编程反馈分频器和两个独立可编程输出分频器组成。通过将外部晶振或基准时钟连接至REFCLK引脚,可将最高达637.5 MHz的频率同步至输入基准。针对所需输出速率,每个输出分频器和反馈分频器的比率可以是工厂设定或I^2^C 编程设定。

第二个小数N分频PLL(PLL2)内置一个可编程模块,可合成基准频率小数倍的VCO频率。针对所需输出速率(最高达637.5 MHz),每个输出分频器和反馈分频器的比率可以通过工厂编程设定。这个小数N分频PLL还可在整数N分频模式下工作以充分降低抖动。

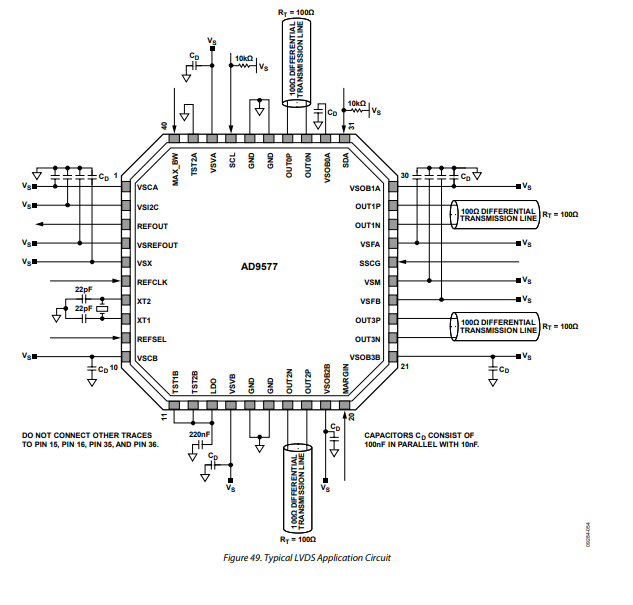

最多四个差分输出时钟信号可配置成LVPECL或LVDS信号传输格式。每个输出对也可配置用于最多八个CMOS输出。支持这类格式的组合。无需外部环路滤波器元件,从而节约了宝贵的设计时间和电路板空间。AD9577提供40引脚6 mm × 6 mm LFCSP封装,采用3.3 V单电源供电,工作温度范围为-40℃至+85°C。

应用

- 低抖动、低相位噪声多路输出时钟发生器,支持多种数据通信应用,包括以太网、光纤、SONET、SDH、PCI-e、SATA、PTN、OTN、ADC/DAC和数字视频。

- 扩频时钟

特性

- 完全集成双路PLL/VCO内核

- 1个整数N分频和1个小数N分频PLL

- 连续频率范围:11.2 MHz至200 MHz

-- 提供200 MHz至637.5 MHz的大多数频率 - PLL1相位抖动

(12 kHz至20 MHz):

460 fs rms(典型值) - PLL2相位抖动(12 kHz至20 MHz)

- 整数N分频模式:470 fs rms(典型值)

- 小数N分频模式:660 fs rms(典型值)

- 输入晶体或基准时钟频率

- 扩频向下扩频 [0, −0.5]%

- 2引脚控制的频率分布图余量微调

- 集成环路滤波器

- 欲了解更多特性,请参考数据手册

框图

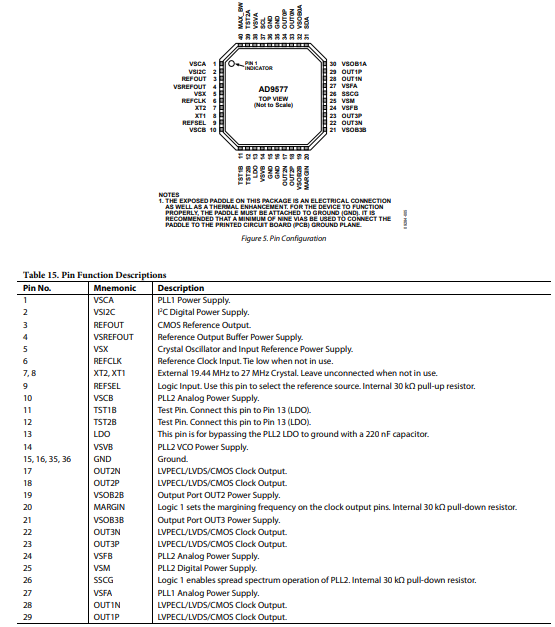

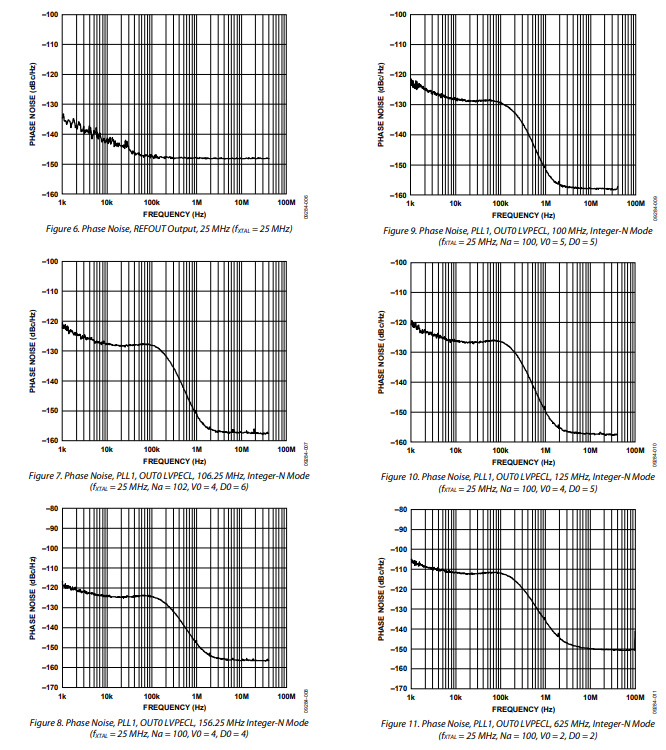

引脚配置描述

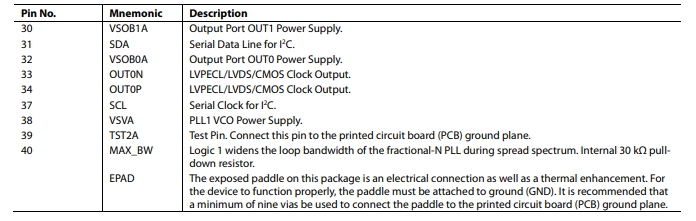

典型性能特征

详细框图

示例应用程序

典型应用电路

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟发生器AD9577资料分享2021-04-06 1456

-

基于FPGA 的新的DDS+PLL时钟发生器2009-12-14 513

-

评估低抖动PLL时钟发生器的电源噪声抑制性能2009-09-18 1851

-

MAX3625B 抖动仅为0.36ps的PLL时钟发生器2010-03-01 1607

-

10GHz扩频时钟发生器的设计2017-01-07 653

-

双锁相环扩频和冗余时钟发生器ad9577数据表2017-10-19 1040

-

AD9577 带双路PLL、扩频和余量微调功能的时钟发生器2019-02-22 393

-

HMC1031:0.1 MHz至500 MHz时钟发生器,带整数N PLL数据表2021-04-23 782

-

AD9577:带双锁相环、扩频和余量的时钟发生器数据表2021-04-29 889

-

时钟发生器AD9516-0技术手册2022-01-25 898

-

评估低抖动PLL时钟发生器的电源噪声抑制2023-04-11 2412

-

时钟发生器由哪些部分组成?锁相环pll的特点是什么?2023-10-13 2184

-

信路达 时钟发生器/PLL频率合成器 XL555数据手册2022-08-19 755

-

PLL1705/PLL1706双通道PLL多时钟发生器数据表2024-08-22 299

-

AD9575双路输出网络时钟发生器技术手册2025-04-10 880

全部0条评论

快来发表一下你的评论吧 !