AD9523-1低抖动时钟发生器,提供14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出技术手册

描述

概述

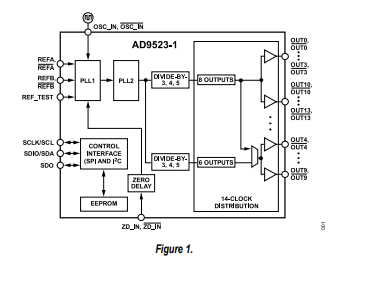

AD9523-1提供低功耗、多路输出时钟分配功能,具有低抖动性能,还配有片内PLL、VCO和两个VCO分频器。片内VCO的调谐频率范围为2.94 GHz至3.1 GHz。

AD9523-1旨在满足长期演进(LTE)和多载波GSM基站设计的时钟要求。它依靠外部VCXO清除参考抖动,以满足严格的低相位噪声要求,从而获得可接受的数据转换器信噪比(SNR)性能。

输入接收器、振荡器和零延迟接收器支持单端和差分两种操作。当连接到恢复的系统参考时钟和VCXO时,器件产生1 MHz至1 GHz范围内的14路低噪声输出,以及一路来自输入PLL (PLL1)的专用缓冲输出。一路时钟输出相对于另一路时钟输出的频率和相位可通过分频器相位选择功能改变,该功能用作无抖动的时序粗调,其调整增量相当于VCO输出信号的半个周期。

通过串行接口可以对封装内EEPROM进行编程,以存储用于上电和芯片复位的用户定义寄存器设置。

数据表:*附件:AD9523-1低抖动时钟发生器,提供14路LVPECL LVDS HSTL输出或29路LVCMOS输出技术手册.pdf

应用

- LTE 和多载波GSM基站

- 无线和宽带基础设施

- 医疗仪器

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 低抖动、低相位噪声时钟分配

- SONET、10Ge、10G FC和其它10 Gbps协议的时钟产生和转换

- 前向纠错(G.710)

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

特性

- 输出频率范围:<1 MHz至1 GHz

- 启动频率精度:<±100 ppm(由VCXO参考精度决定)

- 零延迟操作

输入至输出边沿时序:<150 ps - 两个VCO分频器

- 14 路输出:可配置为LVPECL、LVDS、HSTL和LVCMOS

- 14 个具有零抖动可调延迟的专用输出分频器

- 可调延迟:63个分辨率步进,步长等于VCO输出分频器的½周期

- 输出间偏斜:<50 ps

- 针对奇数分频器设置提供占空比校正

- 上电时所有输出自动同步

- 绝对输出抖动:<150 fs(122.88 MHz时) 积分范围:12 kHz至20 MHz

- 欲了解更多特性,请参考数据手册

框图

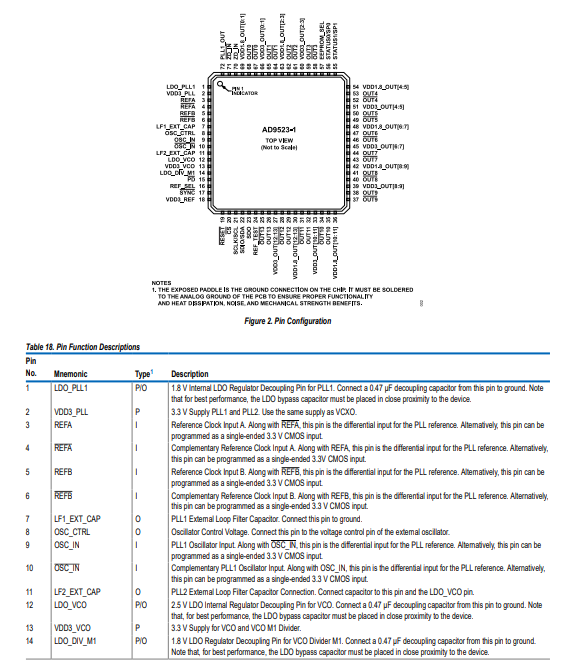

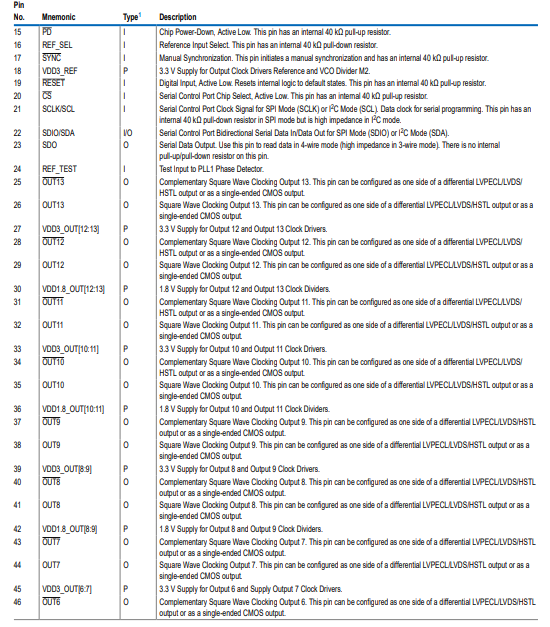

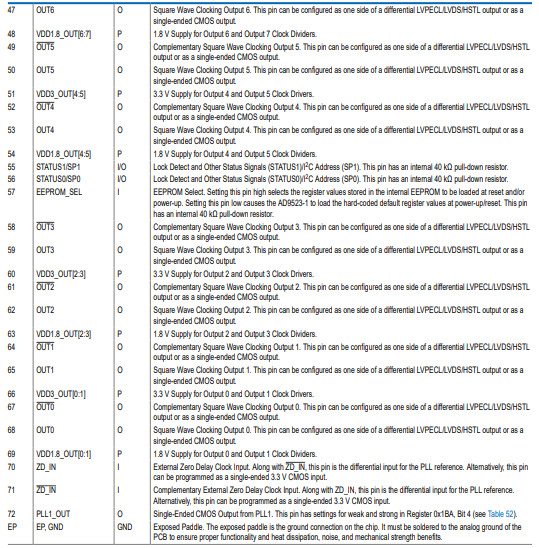

引脚配置描述

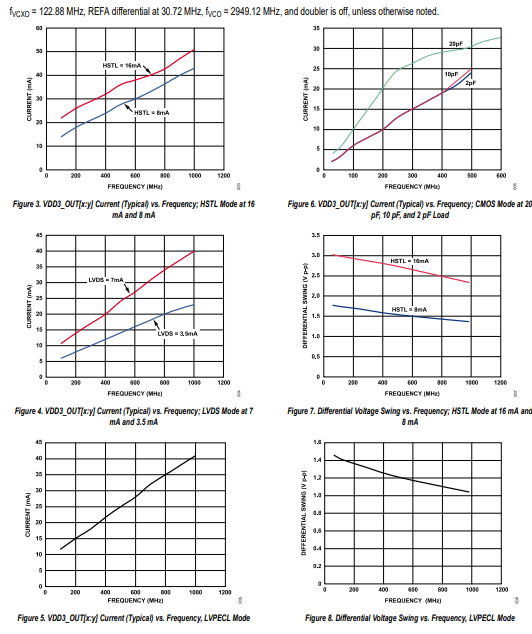

典型性能特征

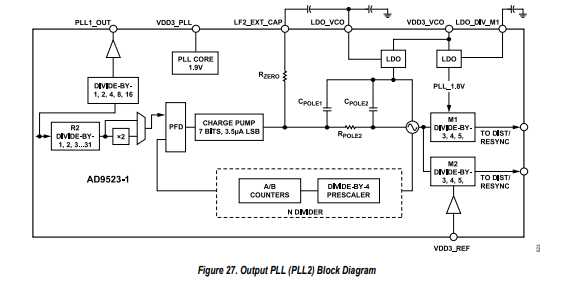

输出锁相环(称为PLL2)由可选的输入参考倍频器、参考分频器、鉴频鉴相器(PFD)、部分集成模拟环路滤波器(见图27)、集成压控振荡器(VCO)和反馈分频器组成。VCO产生3.0GHz的标称频率,输出分频器可实现分频比为3、4和5。

输出PLL的PFD驱动一个电荷泵,该电荷泵可增加、减少或保持存储在环路滤波器电容器(包括内部和外部)中的电荷量,从而产生一个电压,该电压设置VCO的频率。在反馈环路中,PLL的输出反馈到VCO控制电压,以一种使PFD输入信号实现相位锁定的方式变化。

PLL2的增益与电荷泵提供的电流成正比。选择环路带宽是为了降低来自PLL源的噪声贡献,这些噪声可能会降低相位噪声要求。

输出PLL有一个VCO,其多个频段覆盖2.94GHz到3.1GHz的范围。不过,实际工作频率在一定程度上取决于出现在环路滤波器电容器上的控制电压。控制电压使VCO输出频率在所选频段内线性变化。

这种频率可变能力允许输出PLL将输出信号与施加到PFD的参考信号同步。通常,器件会自动选择合适的频段作为其校准的一部分,通过寄存器0x0F3进行调用。

-

AD9523 - 1:低抖动时钟发生器的全面解析2026-03-23 456

-

CDCM61004:高性能、低抖动时钟发生器的设计与应用2026-02-09 261

-

LMK03806 具有 14 个输出的超低抖动时钟发生器技术手册2025-09-16 955

-

AD9523 14路输出、低抖动时钟发生器技术手册2025-04-10 1210

-

CDCM61004四路输出、集成VCO、低抖动时钟发生器数据表2024-08-22 721

-

AD9528:具有14个LVDS/HSTL输出的JESD204B时钟发生器数据表2021-05-13 1085

-

AD9523-1:低抖动时钟发生器,14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出 数据手册2021-03-21 764

-

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO2021-03-19 743

-

AD9523时钟发生器的性能特点及应用分析2019-07-04 5386

-

用于评估AD9523-1时钟发生器的评估板AD9523-1/PCBZ2019-02-22 1709

-

AD9523-1 低抖动时钟发生器,提供14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出2019-02-15 435

-

AD9523-1 低抖动时钟发生器2011-04-11 1443

-

MAX3624 低抖动、精密时钟发生器,提供四路输出2009-09-18 999

-

MAX3625A 低抖动、精密时钟发生器,提供三路输出(应用2009-08-13 1200

全部0条评论

快来发表一下你的评论吧 !