AD9550整数N分频时钟转换器,适合有线通信应用技术手册

描述

概述

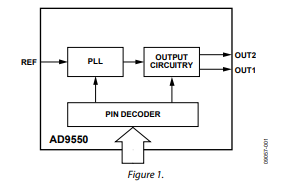

AD9550是一款基于锁相环(PLL)的时钟转换器,针对有线通信和基站应用的需求而设计。它采用整数N分频PLL来满足相关的频率转换要求。REF输入端支持单端输入参考信号。

AD9550的引脚可编程,提供从15个可能的输入频率转换到51个可能的输出频率对(OUT1和OUT2)的标准输入/输出频率转换矩阵。

虽然AD9550严格按照CMOS工艺制造,但其输出与LVPECL、LVDS或单端CMOS逻辑电平兼容。

AD9550的工作温度范围为−40°C至+85°C工业温度范围。

数据表:*附件:AD9550整数N分频时钟转换器,适合有线通信应用技术手册.pdf

应用

- 高频VCXO、OCXO和SAW谐振器的高性价比替代产品

- 灵活的频率转换支持以太网、T1/E1、SONET/SDH、GPON、xDSL等有线应用

- 无线基础设施

- 测试与测量(包括手持式设备)

特性

- 将预设标准输入频率转换为标准输出频率

- 输入频率范围:8 kHz至200 MHz

- 输出频率最高可达810 MHz LVPECL和LVDS (200 MHz CMOS)

- 预设引脚可编程频率转换比

- 片内VCO

- 单端CMOS参考输入

- 2路输出时钟(可独立编程为LVDS、LVPECL或CMOS)

- 3.3 V单电源供电

- 极低功耗:<450 mW(多数条件下)

- 小型封装:5 mm × 5 mm

- 超过Telcordia GR-253-CORE的抖动产生、转换和容差要求

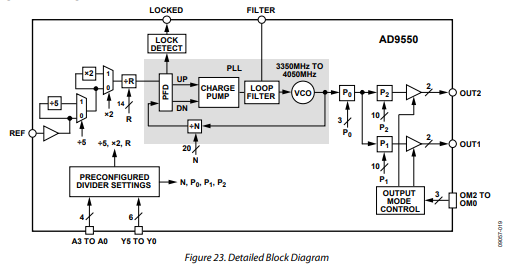

框图

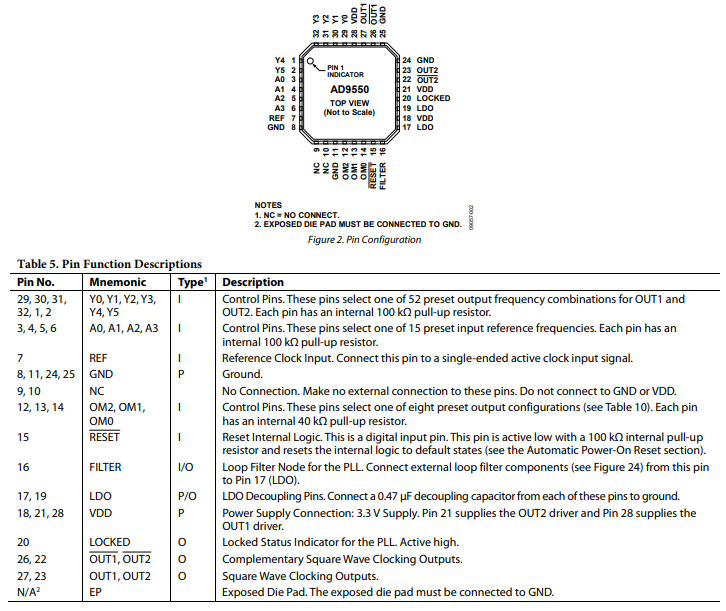

引脚配置描述

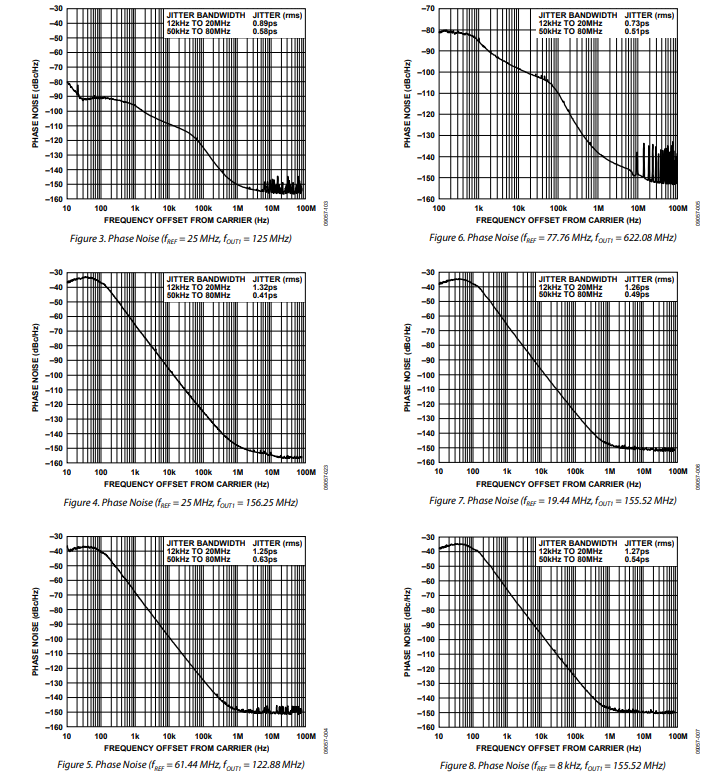

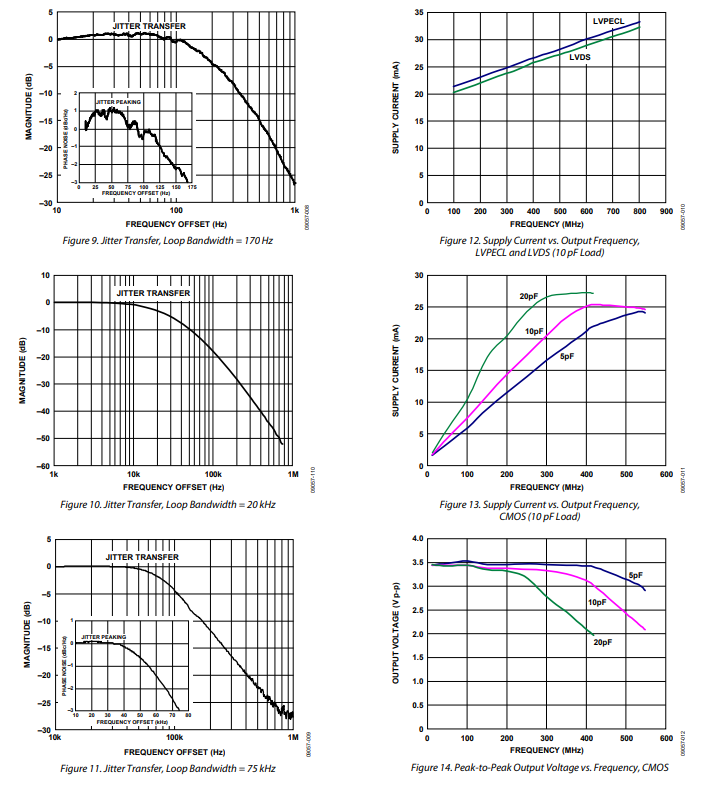

典型性能特征

说明

AD9550接受一个输入参考时钟REF。输入时钟路径包括一个可选的5分频预分频器、一个可选的2倍频乘法器,以及一个14位可编程除法器(R)。输出是R除法器输出到锁相环(PLL)的驱动信号。

PLL根据VCO反馈分频器(N)的值,将R除法器的输出转换为VCO工作范围内(3.35GHz至4.05GHz)的频率。VCO预分频器(P_{o})将VCO输出频率按整数因子5至11进行降低,从而得到305MHz至810MHz范围内的中间频率。10位的**P_{n}和P_{o}除法器可进一步降低P_{o}**输出频率,以分别在OUT1和OUT2产生最终的输出时钟频率。

因此,从参考输入到输出的频率转换比取决于5分频预分频器的选择、2倍频乘法器、三个R除法器的值、N除法器以及P_{n}、**P_{o}和P_{reconfig}**的值。这些参数通过Ax和Yx引脚的预配置设置自动设定(见“预设频率”部分)。

预设频率

频率选择引脚(A3至A0和Y5至Y0)允许用户根据引脚逻辑状态(见图23),通过硬件设置器件的预设输入和输出频率。引脚接地或连接到逻辑0或逻辑1,分别进行解码。

A3至A0引脚允许用户从表6中所示的15个输入参考频率中选择一个。器件根据引脚应用的逻辑电平,设置合适的5分频预分频器、2倍频乘法器以及R除法器(R)的值。

5分频预分频器和2倍频乘法器使PLL输入频率为16kHz或403kHz。有两个例外情况。第一种情况是A3至A0 = 1101,此时PLL输入频率为155.52/59MHz;第二种情况是A3至A0 = 1110,此时PLL输入频率根据Y5至Y0引脚的值,为1.5625MHz或4.86MHz。

Y5至Y0引脚允许用户从表7中所示的52个输出频率组合(f_{out1}和f_{out2})中选择一个。器件根据应用到Yx引脚的逻辑电平,设置合适的**P_{n}和P_{o}**设置值。不过请注意,选择101101至110010需要A3至A0 = 1101,选择110011需要A3至A0 = 1110。

PLL反馈分频器的值(N)以及电荷泵电流(CP)的控制设置取决于表8中所示的Ax和Yx引脚设置的组合。

-

AD9550:有线通信领域的高性能时钟转换器2026-04-20 50

-

有线通信技术和无线通信技术在电能质量在线监测装置中的应用场景有何不同?2025-10-23 1387

-

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc2025-05-22 129

-

AD9553灵活的时钟转换器,适合GPON、基站、SONET/SDH、T1/E1和以太网应用技术手册2025-04-10 1218

-

锁相环整数分频和小数分频的区别是什么?2024-01-31 5717

-

有线通信和无线通信的区别及优缺点2023-05-09 17698

-

常见的无线通信技术和有线通信技术2022-11-30 3552

-

UG-203:AD9550评估板用户指南2021-03-19 576

-

整数N分频软件2021-03-18 655

-

RF数模转换器在通信领域有什么应用?2019-08-14 3488

-

AD9550 整数N分频时钟转换器,适合有线通信应用2019-02-15 452

-

ad9550用于有线通信的整数N时钟转换器2017-10-19 660

全部0条评论

快来发表一下你的评论吧 !