ADN4670可编程低压1:10 LVDS时钟驱动器技术手册

描述

概述

ADN4670是一款低压差分信号(LVDS)时钟驱动器,可以将一路差分时钟输入信号扩展为十路差分时钟输出。这款器件可以通过简单的串行接口进行编程,以便选择两路时钟输入之一(CLK0/CLK0 或CLK1/CLK1) ,以及使能或禁用(三态)任何一路差分输出(Q0/Q0至Q9/Q9) 。ADN4670设计用于50 Ω传输线路环境。

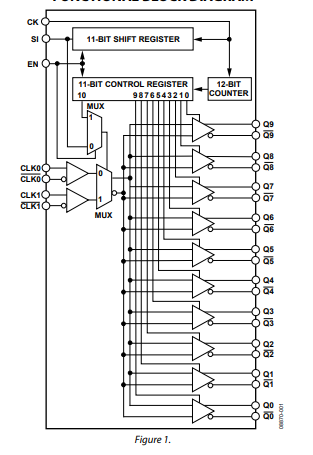

当使能输入EN为高电平时,可以通过将11个数据位输入移位寄存器中来实现对器件的编程。前10位决定哪些输出使能(0 = 禁用,1 = 使能),第11位选择时钟输入(0 = CLK0,1 = CLK1)。第12个时钟脉冲将数据从移位寄存器传输到控制寄存器。

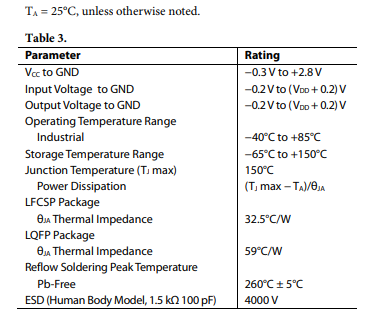

ADN4670的额定温度范围为工业温度范围,提供32引脚LFCSP封装。

数据表:*附件:ADN4670可编程低压 LVDS时钟驱动器技术手册.pdf

框图

引脚配置描述

绝对最大额定值

应用

- 时钟分配网络

特性

- 低输出偏斜:<30 ps(典型值)

- 从1路差分时钟输入提供10路LVDS时钟输出

- 可编程:可以选择两路差分时钟输入之一(CLK0或CLK1),以及使能或禁用各路差分时钟输出

- 信号速率最高达1.1 GHz(典型值)

- 电源电压范围:2.375 V至2.625 V

- 差分输入阈值:±100 mV

- 轨到轨输入共模范围

- 掉电期间I/O引脚具有故障安全特性: V

DD= 0 V - 提供32引脚LFCSP封装

- 工业温度范围:−40℃至+85℃

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

探索MAX9310:高性能1:5时钟驱动器的设计与应用2026-03-26 156

-

解析ADN4670:可编程低电压1:10 LVDS时钟驱动器2026-03-23 343

-

CDCLVD110A可编程低压1:10 LVDS时钟驱动器详解2026-02-10 404

-

深入解析CDCLVP111-SEP:低电压1:10 LVPECL时钟驱动器2026-02-06 355

-

CDCLVD110A 1:10 LVDS时钟驱动器技术文档总结2025-09-19 1056

-

CDCLVD110A可编程低压1:10 LVDS时钟驱动器数据表2024-08-21 406

-

ADN4670:可编程低压1:10 LVDS时钟驱动器2021-05-09 1006

-

AD246:时钟驱动器数据表2021-04-14 1156

-

ADN4650和ADN4651与ADN46521双通道LVDS隔离器的数据手册免费下载2020-11-24 2751

-

ADN4670 可编程低压1:10 LVDS时钟驱动器2019-02-22 424

-

LVDS隔离器adn4650_adn4651_adn4652中文数据手册2017-11-03 3211

-

可编程低电压1:10 LVDS时钟驱动器adn4670数据表2017-10-20 1020

-

可编程低电压1:10 LVDS时钟驱动器ADN46702010-08-14 2976

全部0条评论

快来发表一下你的评论吧 !