AD9572光纤通道/以太网时钟发生器IC,PLL内核,分频器,7路时钟输出技术手册

描述

概述

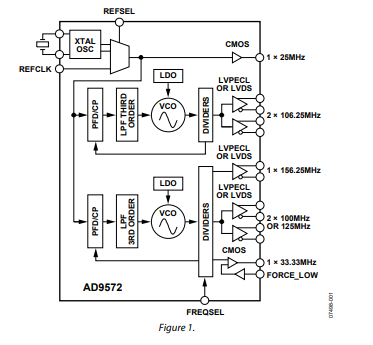

AD9572是一款多输出时钟发生器,具有两个片内PLL内核,针对包括以太网接口的光纤通道线路卡应用进行了优化。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现网络的较高性能。这款器件也适合相位噪声和抖动要求严格的其它应用。

数据表:*附件:AD9572光纤通道 以太网时钟发生器IC,PLL内核,分频器,7路时钟输出技.pdf

PLL部分由低噪声鉴频鉴相器(PFD)、精密电荷泵(CP)、低相位噪声压控振荡器(VCO)、预编程的反馈分频器和输出分频器组成。通过将一个外部晶振或参考时钟连接到REFCLK引脚,可以将最高156.25 MHz的频率锁定至输入参考。每个输出分频比和反馈分频比针对所要求的输出速率进行预编程。

第二个PLL也用作整数N分频频率合成器,并驱动两个LVPECL或LVDS输出缓冲器以支持106.25 MHz频率。无需外部环路滤波器,从而节省宝贵的设计时间和电路板空间。

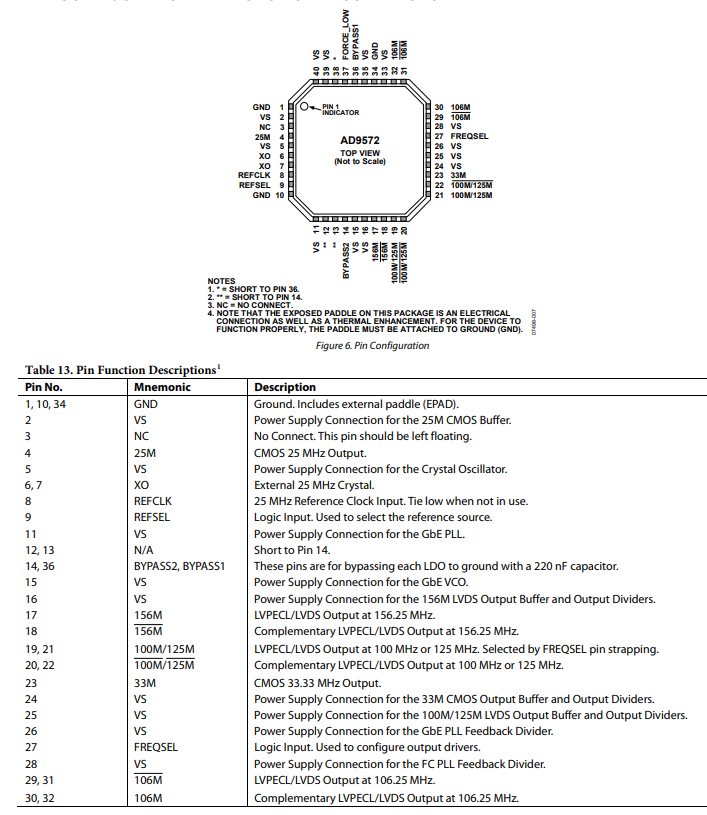

AD9572提供40引脚6 mm × 6 mm、LFCSP封装,可以采用3.3 V单电源供电。温度范围为−40°C至+85°C。

应用

- 光纤通道线路卡、交换机和路由器

- 支持千兆以太网/PCIe

- 低抖动、低相位噪声时钟产生

特性

- 完全集成的双VCO/PLL内核

均方根抖动:167 fs(0.637 MHz至10 MHz,

106.25 MHz)

均方根抖动:178 fs(1.875 MHz至20 MHz,

156.25 MHz) - 均方根抖动:418 fs(12 kHz至20 MHz,

125 MHz输入晶振或25 MHz时钟频率) - 针对106.25 MHz、156.25 MHz、33.33 MHz、100 MHz、125 MHz提供预设分频比

- 可选择LVPECL或LVDS输出格式

- 集成环路滤波器

- 参考时钟输出副本

- 通过绑定引脚配置速率

- 节省空间的6 mm × 6 mm、40引脚LFCSP封装

- 功耗:0.71 W(LVDS工作方式)

- 功耗:1.07 W(LVPECL工作方式)

- 3.3 V 工作电压

框图

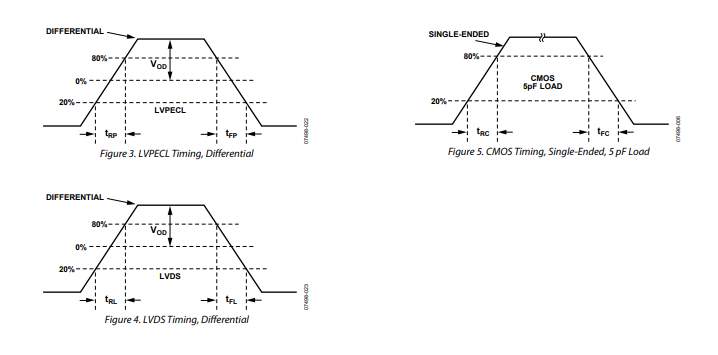

时序图

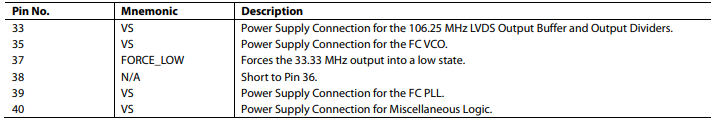

引脚配置描述

操作理论

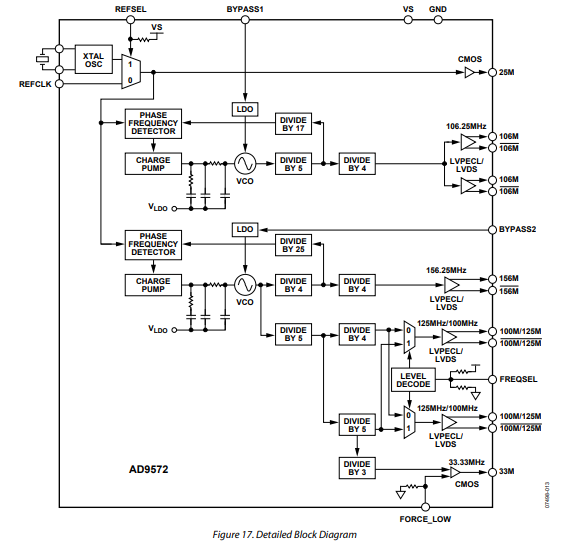

图17展示了AD9572的框图。该芯片集成了双PLL核心,这些核心经配置可生成网络应用所需的特定时钟频率,无需任何用户编程。这基于亚德诺半导体成熟的合成器技术,以卓越的相位噪声性能著称。AD9572集成度高,包含环路滤波器、电源噪声抑制调节器,以及所有必要的分频器和多种输出缓冲器格式,还带有一个晶体振荡器。用户只需提供一个25MHz参考时钟或外部晶体,即可实现完整的线路卡时钟解决方案,无需任何处理器干预。此外,还提供一个25MHz参考时钟源。

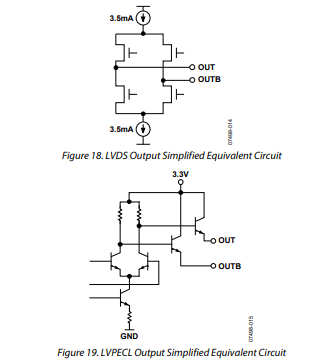

LVDS和LVPECL输出的简化等效电路分别如图18和图19所示。 )

)

差分输出在出厂时已编程为LVPECL或LVDS格式,可根据需求选择任一模式。

CMOS驱动器相比差分输出往往会产生更多噪声,因此,33.33MHz输出引脚(引脚21和引脚22)与差分输出引脚的距离会影响抖动性能。基于此,当FREQSEL = 0时(即差分输出产生125MHz频率时),33MHz引脚可通过置位引脚37上的FORCE_LOW_OUT(见表16)强制为低电平。内部下拉电阻使33.33MHz输出在引脚未连接时也能正常工作。

-

AD9572:高性能光纤通道/以太网时钟发生器IC的深度解析2026-03-23 185

-

LMK03806 具有 14 个输出的超低抖动时钟发生器技术手册2025-09-16 1005

-

AD9573 PCI-Express时钟发生器IC,PLL内核,分频器,两路输出技术手册2025-04-11 1188

-

AD9574以太网 千兆以太网时钟发生器技术手册2025-04-10 1365

-

低抖动高精度时钟发生器MAX3625B相关资料分享2021-05-18 1223

-

AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表2021-05-08 954

-

AD9571:以太网时钟发生器,10个时钟输出2021-04-16 975

-

AD9510:1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出2021-03-21 1000

-

AD9571ACPZPEC时钟发生器销售2019-07-09 1789

-

AD9572 光纤通道/以太网时钟发生器IC,PLL内核,分频器,7路时钟输出2019-02-15 917

-

光纤通道/以太网时钟发生器IC 7时钟输出ad9572数据表2017-10-19 996

-

MAX3679A高性能四路输出时钟发生器(Maxim)2010-04-14 1218

-

Maxim推出高性能、三路输出时钟发生器MAX3625B2009-12-14 1312

全部0条评论

快来发表一下你的评论吧 !