ADCLK948 2路可选输入、8路LVPECL输出、SiGe时钟扇出缓冲器技术手册

描述

概述

ADCLK948是一款超快时钟扇出缓冲器,采用ADI公司专有的XFCB3硅-锗(SiGe)双极性工艺制造,设计用于要求低抖动的高速应用。

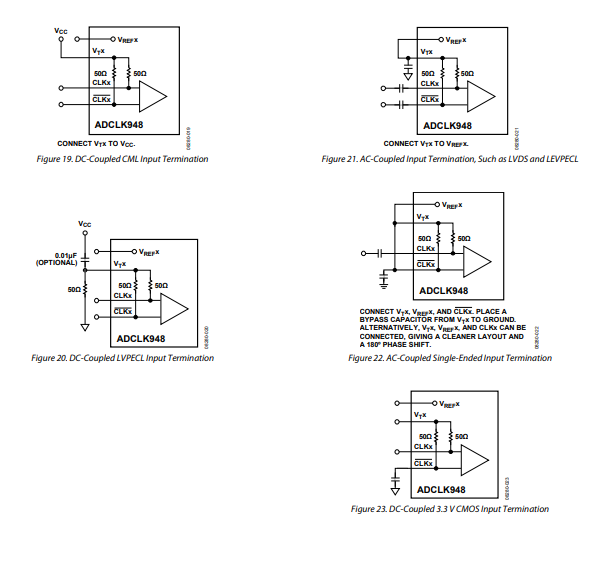

该器件具有两个差分输入,通过IN_SEL控制引脚进行选择。两个输入均配备中心抽头、差分、100 Ω片内端接电阻,接受直流耦合LVPECL、CML、3.3 V CMOS(单端)以及交流耦合1.8 V CMOS、LVDS和LVPECL输入。提供VREFx引脚用于偏置交流耦合输入。

数据表:*附件:ADCLK948 2路可选输入、8路LVPECL输出、SiGe时钟扇出缓.pdf

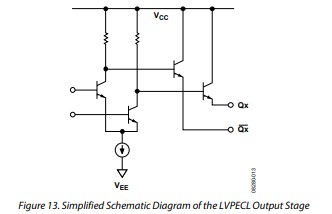

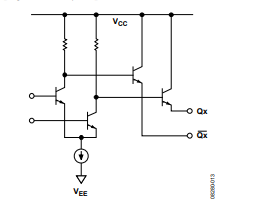

ADCLK948内置8个全摆幅射极耦合逻辑(ECL)输出驱动器。对于LVPECL(正ECL)工作模式, VCC 偏置至正电源, VEE 偏置至接地。对于ECL工作模式, VCC 偏置至接地, VEE 偏置至负电源。

输出级旨在从各端将800 mW直接驱动至端接于VCC -2V的50 Ω负载,从而获得1.6 V的总差分输出摆幅。

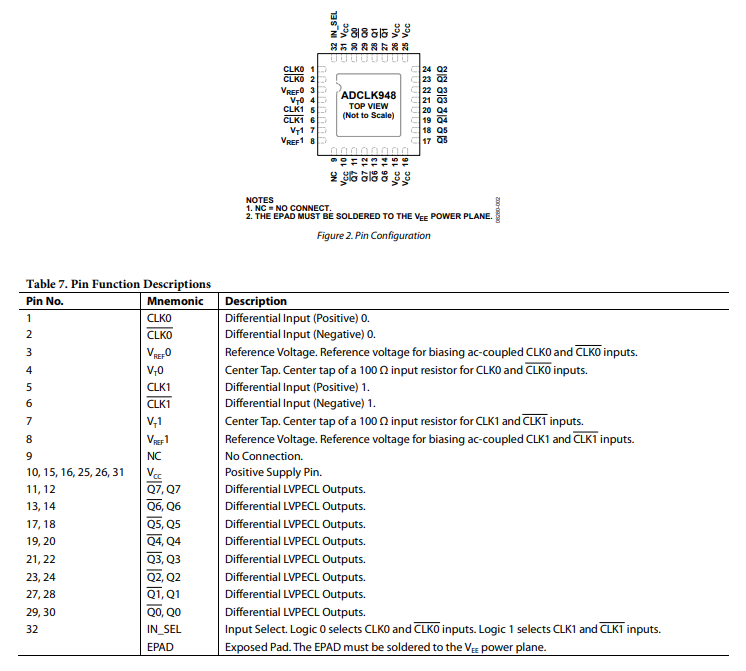

ADCLK948采用32引脚LFCSP封装,额定工作温度范围为−40°C至+85°C标准工业温度范围。

应用

- 低抖动时钟分配

- 时钟与数据信号恢复

- 电平转换

- 无线通信

- 有线通信

- 医疗和工业成像

- 自动测试设备(ATE)和高性能仪器仪表

特性 - 2个可选差分输入

- 工作频率:4.8 GHz

- 宽带随机抖动:75 fs rms

- 片内输入端接

- 电源:3.3 V

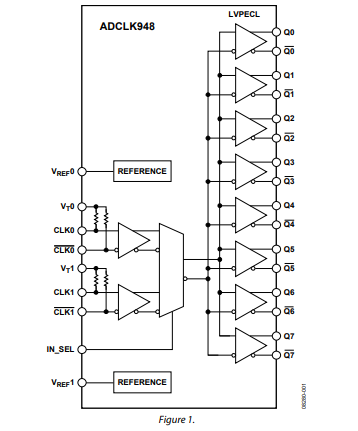

框图

引脚配置描述

典型性能特征

功能描述

时钟输入

ADCLK948 从两个输入中接收一个差分时钟输入,并将选定的时钟分配到所有八个LVPECL输出。规定的最大频率是输出电压摆幅为标准LVPECL摆幅50%时的点(见图4)。有关时钟输入的更多详细信息,请参见功能框图(图1)和“一般说明”部分。图19展示了23种不同的时钟输入端接方案。

输出抖动性能会因输入斜率低于4 V/ns而下降,如图12所示。ADCLK948经过专门设计,可在较宽的输入斜率范围内将额外的随机抖动降至最低。只要有可能,应使用快速肖特基二极管衰减器来降低过大输入信号的斜率,因为衰减器应采用低损耗电介质或具有良好高频特性的电缆。

时钟输出

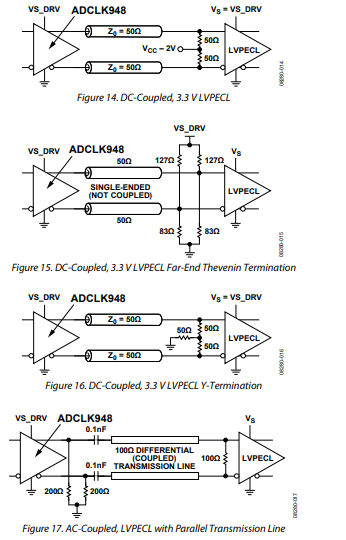

规定的性能要求使用合适的传输线终端。ADCLK948的LVPECL输出旨在直接驱动800 mV至50 Ω电缆,或驱动至以VCC - 2 V为参考端接50 Ω的微带线或带状线传输线,如图14所示。LVPECL输出级如图13所示。此输出级经过优化,可实现最佳的高速信号传输线匹配。如果高速信号布线长度超过一厘米,无论是微带线还是带状线技术,都需要适当的传输线端接,以确保正确的定时,并防止过度的输出振铃和与脉冲宽度相关的传播延迟色散。

戴维南等效端接使用电阻网络为LVPECL驱动器提供50 Ω直流端接,该直流电压低于VS_DRV。在此方案中,VS_DRV上的直流偏置点应等于接收缓冲器的Vₛ。尽管图15所示的电阻组合会产生VS_DRV - 2 V的直流偏置点,但实际的共模电压为VS_DRV - 1.3 V,因为有额外电流从ADCLK948 LVPECL驱动器的下拉电阻流出。

LVPECL Y端接是一种出色的端接方案,它使用变压器组件,同时提供奇模和偶模阻抗匹配。偶模阻抗匹配在高频下紧密耦合传输线时很重要。其主要缺点是,它在改变LVPECL驱动器射极跟随器的驱动强度方面灵活性有限。在驱动长走线时,这通常不是问题。

图14 - 图17描绘了各种直流耦合的LVPECL输出端接方案。接收缓冲器的Vₛ应与VS_DRV匹配。

输入端接选项

-

ADCLK948:高性能时钟扇出缓冲器的全面解析2026-03-23 158

-

ADCLK950 2路可选输入、10路LVPECL输出、SiGe时钟扇出缓冲器技术手册2025-04-11 1230

-

ADCLK944 2.5 V/3.3 V、4路LVPECL输出、SiGe时钟扇出缓冲器技术手册2025-04-10 1665

-

HACP1204QN型低抖动LVPECL时钟缓冲器2025-02-13 464

-

CN0294 利用低抖动LVPECL扇出缓冲器增加时钟源的输出数2021-06-05 1117

-

ADCLK954:两个可选输入、12个LVPECL输出、SiGe时钟扇出缓冲器数据表2021-04-25 1093

-

ADCLK950:两个可选输入、10个LVPECL输出、SiGe时钟扇出缓冲器数据表2021-04-19 938

-

ADCLK948 2路可选输入、8路LVPECL输出、SiGe时钟扇出缓冲器2019-02-22 695

-

采用ADCLK948时钟扇出缓冲器的评估板ADCLK948/PCBZ2019-02-21 1718

全部0条评论

快来发表一下你的评论吧 !