AD9573 PCI-Express时钟发生器IC,PLL内核,分频器,两路输出技术手册

描述

概述

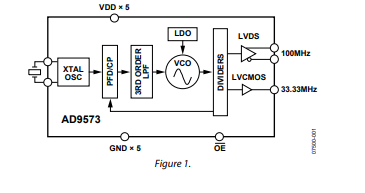

AD9573是一款高度集成的双路输出时钟发生器 , 包括一个针对PCI-e应用而优化的片内PLL内核 。 整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列 , 可实现线路卡的较高性能 。 这款器件也适合相位噪声和抖动要求严格的其它应用。

数据表:*附件:AD9573 PCI-Express时钟发生器IC,PLL内核,分频器,两路输出技术手册.pdf

PLL部分由低噪声鉴频鉴相器(PFD)、精密电荷泵、低相位噪声压控振荡器(VCO)、预编程的反馈分频器和输出分频器组成。

通过连接一个外部25 MHz晶振,可以将100 MHz和33.33 MHz输出频率锁定至输入参考。输出分频比和反馈分频比可针对所要求的输出速率进行预编程。无需外部环路滤波器,从而节省宝贵的设计时间和电路板空间。

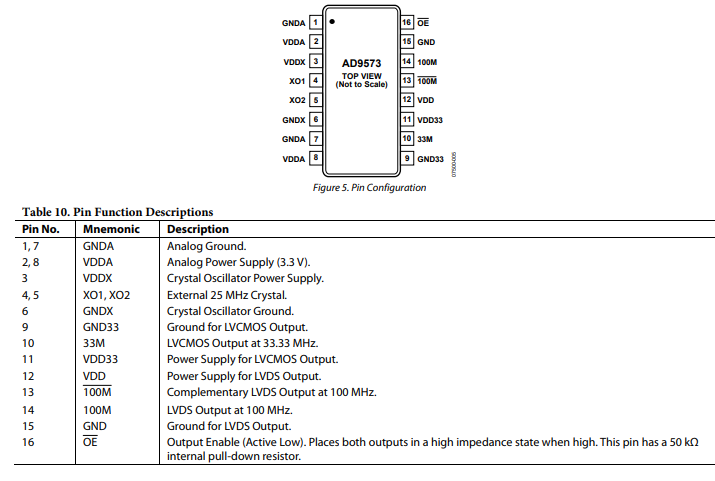

AD9573提供16引脚、4.4 mm × 5.0 mm TSSOP封装,可以采用3.3 V单电源供电。温度范围为−40°C至+85°C。

应用

- 线路卡、交换机和路由器

- CPU/PCIe 应用

- 低抖动、低相位噪声时钟产生

特性

- 完全集成的VCO/PLL内核

均方根抖动:0.54 ps(12 kHz至20 MHz)

输入晶振频率:25 MHz - 针对100 MHz、33.33 MHz提供预设分频比

- LVDS/LVCMOS 输出格式

- 集成环路滤波器

- 4.4 mm × 5.0 mm TSSOP封装,节省空间

- 功耗:0.235 W

- 3.3 V 工作电压

框图

引脚配置描述

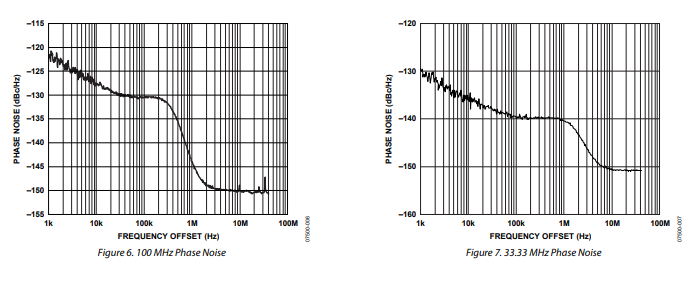

典型性能特征

操作理论

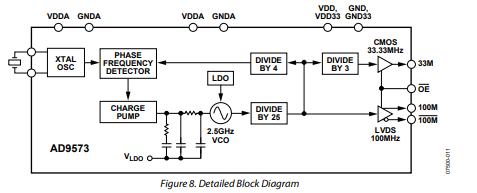

图8展示了AD9573的框图。该芯片具有一个锁相环(PLL)内核,经过配置可生成PCI - Express所需的特定时钟频率,无需用户进行任何编程。此PLL基于亚德诺半导体(Analog Devices)成熟的合成器技术,其卓越的相位噪声性能值得关注。AD9573集成度很高,包含环路滤波器、电源噪声抗扰度调节器、所有必要的分频器、输出缓冲器以及一个晶体振荡器。用户只需提供25 MHz的外部晶体,即可实现完整的PCIe时钟解决方案,无需处理器干预。

输出

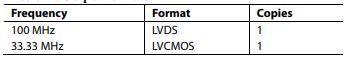

表11总结了可用的输出。

表11. 输出格式

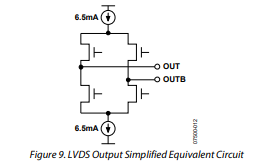

图9展示了LVDS输出的简化等效电路。100 MHz输出被描述为LVDS,是因为它采用了LVDS驱动器拓扑结构。不过,其电平为HCSL兼容,因此与标准LVDS不同。输出电流有所增加,以提供比标准LVDS更大的输出摆幅。

图9. LVDS输出简化等效电路

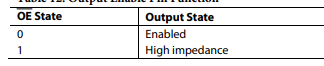

根据表12连接OE引脚,可将两个输出都置于高阻抗状态。该引脚有一个50 kΩ的下拉电阻。

表12. 输出使能引脚功能

鉴频鉴相器(PFD)和电荷泵

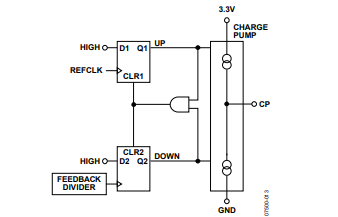

PFD接收来自参考时钟和反馈分频器的输入,产生一个与两者之间相位和频率差成比例的输出。图10展示了简化示意图。

图10. PFD简化示意图及时序(锁定状态)

电源

AD9573的VDD需要3.3 V ± 10%的电源。规格部分的表格给出了AD9573在该电源电压范围内的性能预期。相对于地,VDD或VDDA引脚上的绝对最大电压范围为(-0.3 V) - (+3.6 V),此范围绝不能被超出。

在PCB布局中应遵循良好的工程实践。电源走线和PCB接地层的电源应在PCB上用足够的电容(>10 μF)旁路。AD9573应使用足够的电容(0.1 μF)在所有电源引脚处尽可能靠近引脚进行去耦。

-

探索 ICS844201I - 45:PCI Express 时钟发生器的卓越之选2026-04-12 497

-

深入解析AD9573:PCI - Express时钟发生器IC的卓越之选2026-03-23 220

-

AD9577带双路PLL、扩频和余量微调功能的时钟发生器技术手册2025-04-10 1313

-

CDCM61002两路输出、集成VCO、低抖动时钟发生器数据表2024-08-22 968

-

时钟发生器由哪些部分组成?锁相环pll的特点是什么?2023-10-13 2634

-

低抖动高精度时钟发生器MAX3625B相关资料分享2021-05-18 1223

-

AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表2021-05-08 954

-

AD9510:1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出2021-03-21 1000

-

AD9571ACPZPEC时钟发生器销售2019-07-09 1789

-

AD9573 PCI-Express时钟发生器IC,PLL内核,分频器,两路输出2019-02-15 802

-

PCI时钟发生器IC锁相环分频器两个输出ad9573数据表2017-10-19 1109

-

MAX3679A高性能四路输出时钟发生器(Maxim)2010-04-14 1218

全部0条评论

快来发表一下你的评论吧 !