AD9548 4-8路输入的网络时钟发生器/同步器技术手册

描述

概述

AD9548可为包括同步光纤网络(SONET/SDH)在内的许多系统提供同步。它可以产生一个与高达四个差分或者八个单端外部输入基准之一同步的输出时钟。数字PLL能减少与外部基准有关的输入时间抖动或者相位噪声。即使当所有基准发生故障,AD9548仍能够利用数控环路和保持(holdover)电路连续产生有效的、干净的(低抖动)输出时钟。

数据表:*附件:AD9548 4-8路输入的网络时钟发生器-同步器技术手册.pdf

AD9548可工作于-40°C至+85°C的工业温度范围。

应用

- 网络同步

- 基准时钟抖动清除

- GPS 1 每秒脉冲数同步

- SONET/SDH时钟,直到OC-192,包括前向纠错(FEC)

- Stratum 2保持(holdover),抖动清除,及相位瞬变控制

- Stratum 3/3E 基准时钟

- 无线基站,控制器

- 有线基础设施

- 数据通信

特性

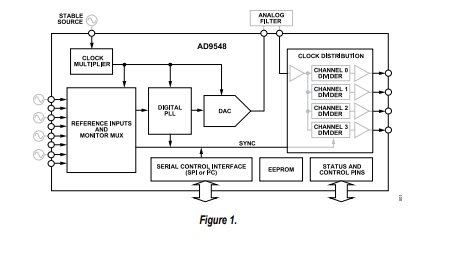

框图

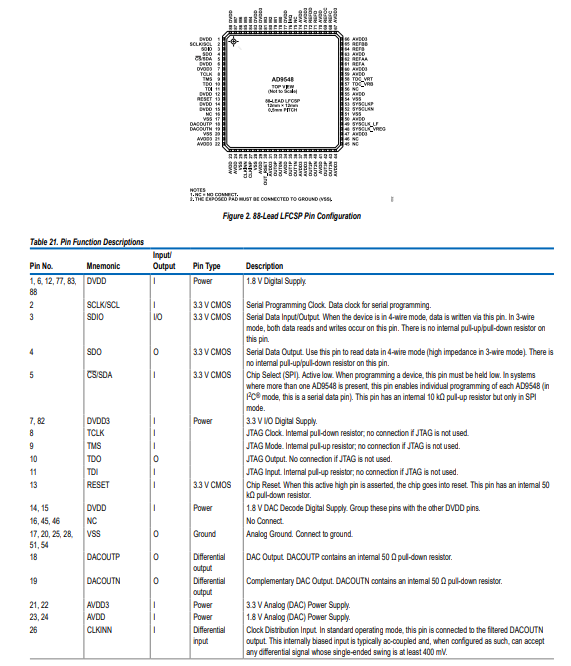

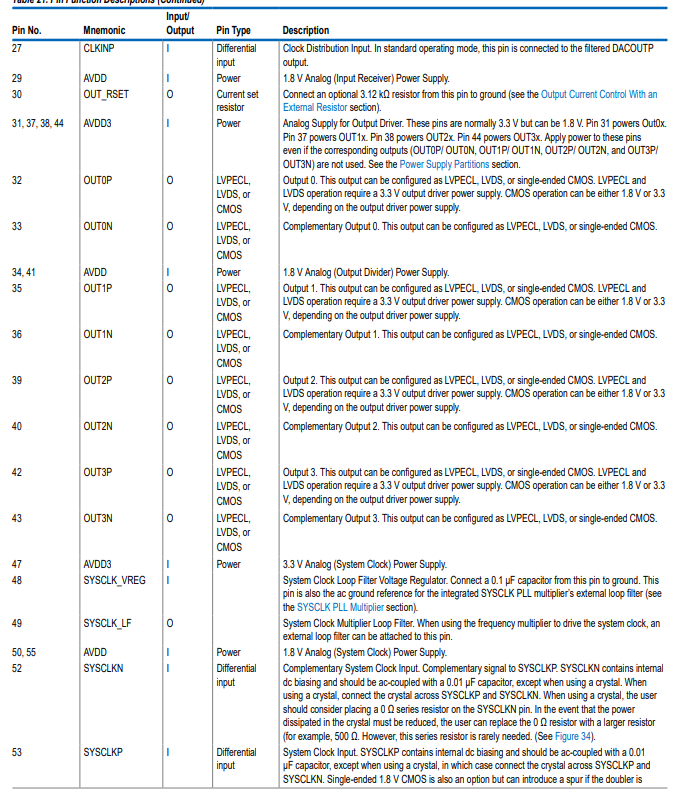

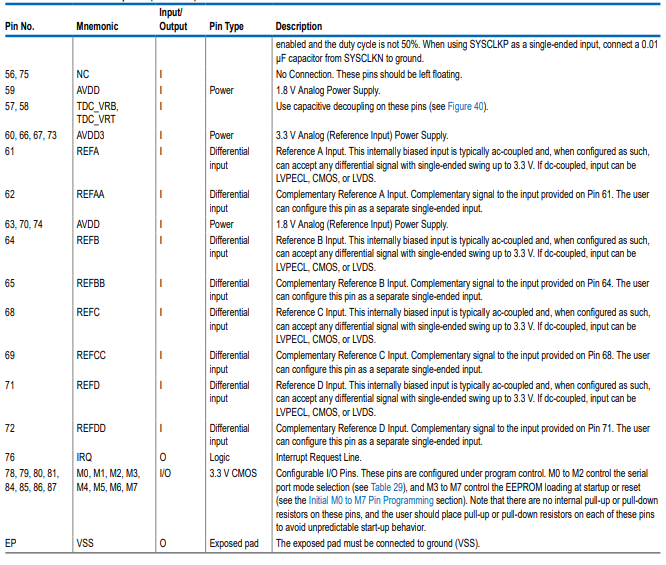

引脚配置描述

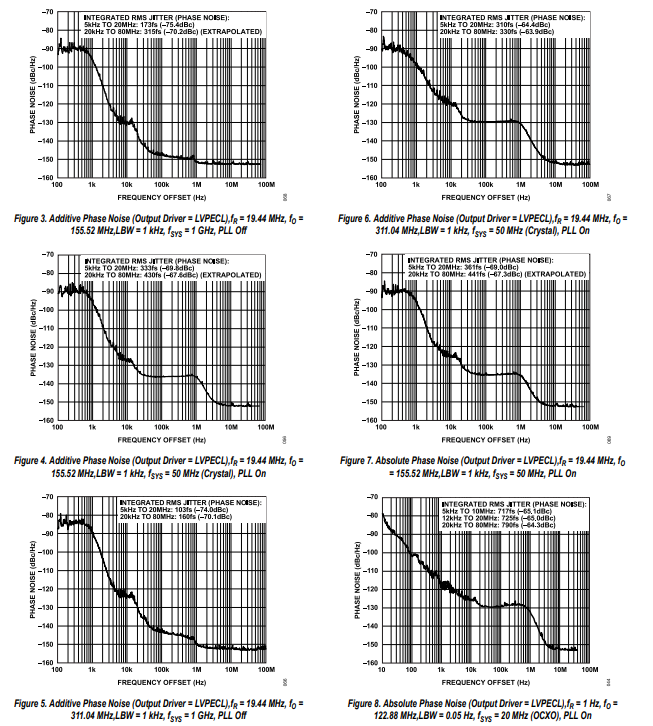

典型性能特征

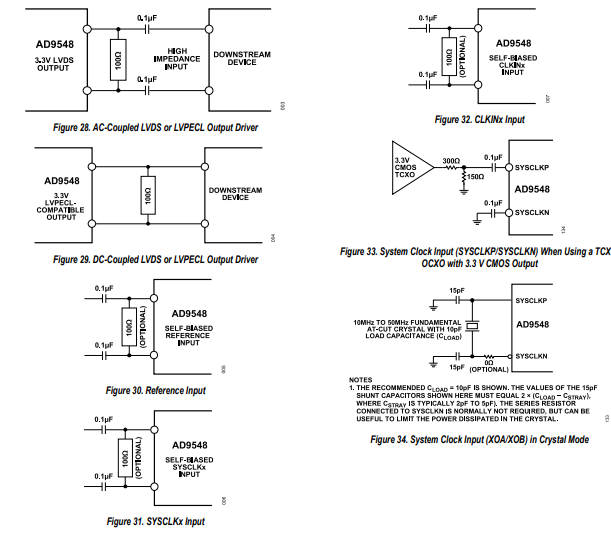

输入/输出端接建议

操作理论

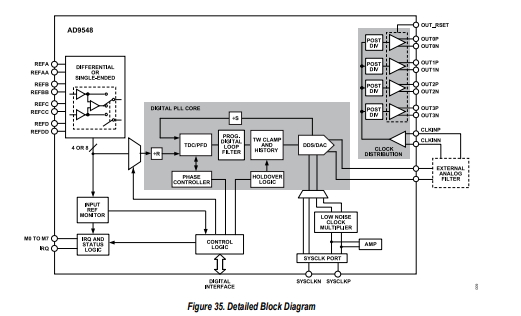

AD9548提供的时钟输出在相位和频率上与所选(有效)参考时钟直接相关,主要由系统时钟控制。AD9548支持多达八个参考输入通道以及广泛的参考频率。该产品的核心是一个数字锁相环(DPLL)。DPLL具有可编程数字环路滤波器,可大幅降低抖动传输,从有源参考时钟到输出。AD9548支持多种手动和自动切换模式。在保持模式下,只要数模转换器(DAC)采样时钟存在,AD9548就会持续提供输出。保持模式输出频率是保持模式前输出频率历史记录的时间平均值。

该器件提供手动和自动参考切换功能,如果有源参考失效或出现故障,它可以切换到备用参考。直接数字合成器(DDS)和集成DAC构成一个数字控制振荡器(DCO)。DCO输出是一个正弦信号(最大450 MHz),其频率由有源参考频率以及可编程参考预分频器(R)和反馈分频器(S)确定。虽然图35中未明确显示,但D - 除法器包含一个整数和分数组件,类似于分数N型合成器。

SYSCLKx输入为DAC提供采样时钟,它可以是直接应用的高频源,也可以是低频源,通过集成的PLL倍频器提供所需频率。低频选项还允许使用连接在SYSCLKx输入两端的晶体谐振器。

DAC输出直接在芯片上进行滤波,去除采样杂散。一旦输入信号转换为单端信号,内部滤波器就会将滤波后的正弦信号转换为时钟信号(方波),其上升沿和下降沿都非常快。

时钟分配部分为四个输出驱动器提供信号。每个驱动器可配置为单端差分LVPECL/LVDS输出或双单端CMOS输出。此外,四个输出中的每一个都有一个专用的30位可编程正/负分频器。这使得时钟分配部分在高达725 MHz的频率下都能使用。它可以使用带通重建滤波器(例如SAW滤波器)从DAC输出频谱中提取图像,从而允许输出频率超过DAC输出典型的450 MHz限制。

参考时钟输入

四对引脚为参考时钟接收器提供接入。每对引脚可配置为单个差分接收器或两个独立的单端接收器,以适应输入信号以及缓慢上升和下降沿的情况。差分和单端输入接收器都采用迟滞方式,迟滞可确保输入不会因浮动输入而导致接收器出现自发振荡。

配置为差分工作模式时,输入接收器可适应交流或直流耦合输入信号。接收器内部直流偏置,以处理交流耦合操作。

配置为单端工作模式时,输入接收器具有典型值为45 kΩ的下拉负载。每个单端接收器都有三个用户可编程阈值电压范围。

-

ADI AD9547网络时钟发生与同步方案2010-02-14 1444

-

AN-1064了解AD9548的输入基准监控器2012-02-03 1281

-

四/八进制输入网络时钟发生器/同步器AD9548数据表2017-10-19 1058

-

AD9548 4/8路输入的网络时钟发生器/同步器2019-02-22 1024

-

AD9548评估板的基本性能介绍2019-07-15 3543

-

AD9548芯片的性能特点及应用2019-06-10 7191

-

AD9525: 8路LVPECL输出低抖动时钟发生器2021-03-21 860

-

AD9548:四/八路输入网络时钟发生器/同步器数据表2021-04-16 920

-

AD9547:双/四输入网络时钟发生器/同步器数据表2021-04-30 885

-

时钟发生器AD9516-0技术手册2022-01-25 999

-

毫微微时钟网络同步器、抖动衰减器和时钟发生器RC32112A 数据表2024-01-31 482

-

AD9547双路/四路输入网络时钟发生器/同步器技术手册2025-04-11 1062

-

LMK5B33414EVM网络时钟发生器评估模块技术解析2025-09-08 1060

-

AD9548:网络时钟生成与同步的卓越解决方案2026-04-13 155

-

AD9549:高性能网络时钟发生器/同步器的深度解析2026-04-14 67

全部0条评论

快来发表一下你的评论吧 !