AD9516-5 14路输出时钟发生器技术手册

描述

概述

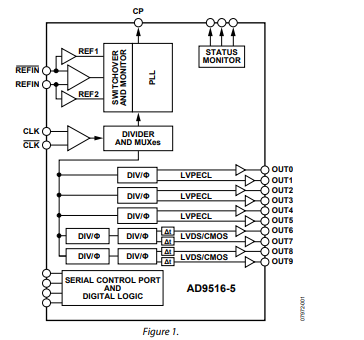

AD9516-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO/VCXO使用。

AD9516-5具有出色的低抖动和相位噪声特性,可极大地提升数据转换器的性能,并且也适合其它相位噪声和抖动要求严苛的应用。

数据表:*附件:AD9516-5 14路输出时钟发生器技术手册.pdf

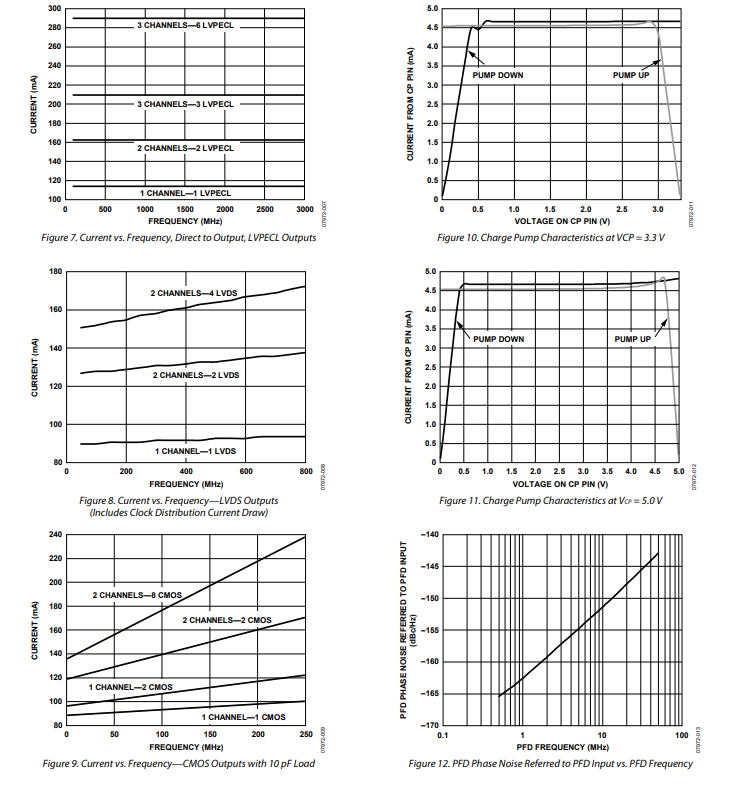

AD9516-5具有六路LVPECL输出(分为三组)和四路LVDS输出(分为两组)。可以将任何一路LVDS输出重新配置为两路CMOS输出。LVPECL输出的工作频率达1.6 GHz,LVDS输出的工作频率达800 MHz,CMOS输出的工作频率达250 MHz。

每对输出均有分频器,其分频比和粗调延迟(或相位)均可以设置。LVPECL输出的分频范围为1至32。LVDS/CMOS输出的分频范围最高可达1024。

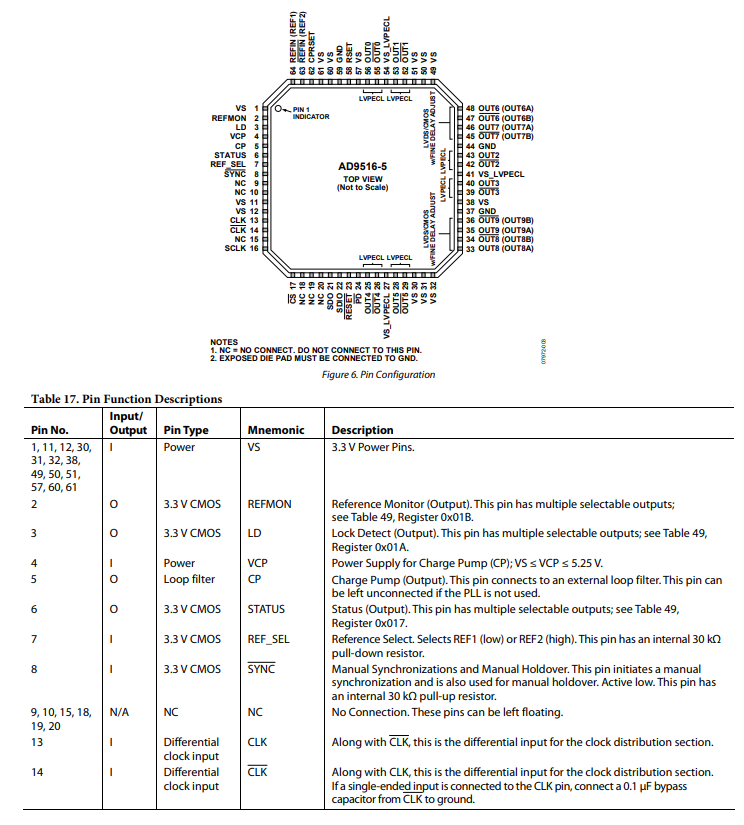

AD9516-5提供64引脚LFCSP封装,可以采用3.3 V单电源供电采用外部VCO时,需要更宽的电压范围, 可通过将电荷泵电源(VCP)与5.5 V电压相连来实现。独立的LVPECL电源可以为2.375 V至3.6 V。

AD9516-5的额定工作温度范围为−40°C至+85°C标准工业温度范围。

应用

- 低抖动、低相位噪声时钟分配

- 10/40/100 Gb/s网络线路卡,包括SONET、同步以太网、OTU2/3/4

- 前向纠错(G.710)

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

特性

- 四路800 MHz LVDS输出,分为2组

每组共用2个级联的1至32分频器和粗调相位延迟

加性输出抖动:275 fs均方根值

可以精调每路LVDS输出的延迟(Δt)

可以将每路LVDS输出重新配置为两路250MHz CMOS输出 - 六路1.6 GHz LVPECL输出,分为3组

每组共用1至32分频器和粗调相位延迟

加性输出抖动:225 fs均方根值

通道间偏斜成对输出小于10 ps - 欲了解更多特性,请参考数据手册

框图

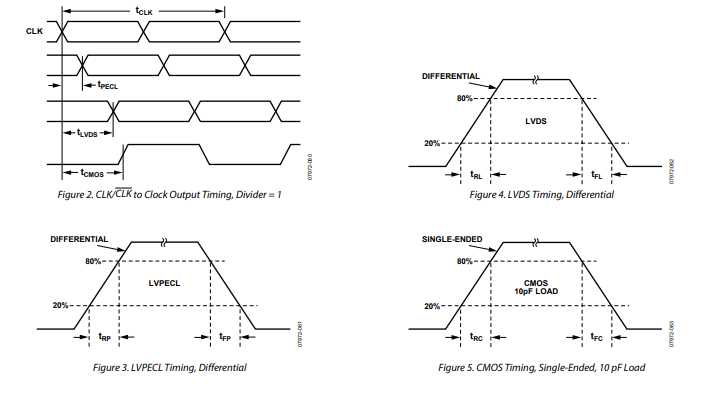

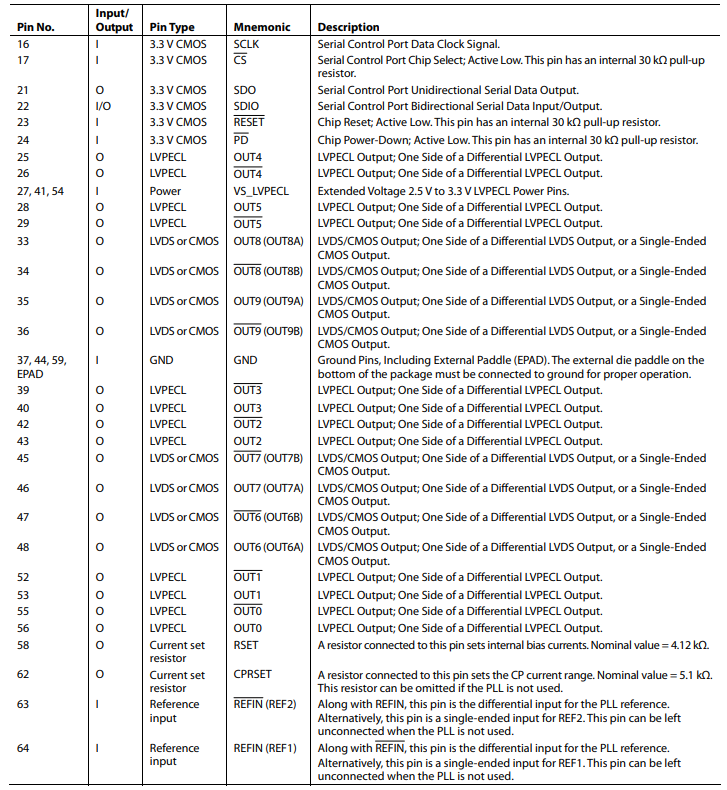

时序图

引脚配置描述

典型性能特征

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AD9516 - 5 14 输出时钟发生器:高精度时钟解决方案2026-03-22 647

-

时钟发生器AD9516-0技术手册2022-01-25 1058

-

AD9516-3:14输出时钟发生器,集成2.0 GHz压控振荡器数据表2021-05-25 1012

-

AD9516-0:14-集成2.8 GHz压控振荡器数据表的输出时钟发生器2021-05-24 812

-

AD9516-2:14-集成2.2 GHz压控振荡器数据表的输出时钟发生器2021-04-28 723

-

AD9516-5:14-输出时钟发生器数据表2021-04-27 891

-

AD9516-1:14-集成2.5 GHz压控振荡器数据表的输出时钟发生器2021-04-18 735

-

AD9516-4:14-集成1.6 GHz压控振荡器数据表的输出时钟发生器2021-04-17 814

-

AD9523-1:低抖动时钟发生器,14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出 数据手册2021-03-21 785

-

AD9523时钟发生器的性能特点及应用分析2019-07-04 5440

-

AD9516-5 14路输出时钟发生器2019-02-22 949

全部0条评论

快来发表一下你的评论吧 !