AD9522-3 12路LVDS/24路CMOS输出时钟发生器,集成2 GHz VCO技术手册

描述

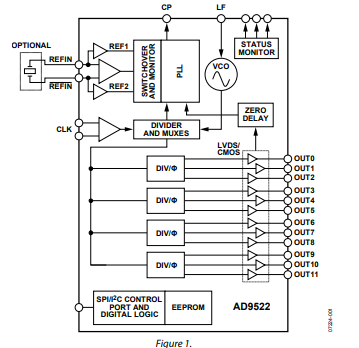

概述

AD9522-3提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.72 GHz至2.25 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

数据表:*附件:AD9522-3 12路LVDS 24路CMOS输出时钟发生器,集成2 GHz VCO技术手册.pdf

AD9522串行接口支持SPI和I2C®端口。封装内EEPROM可以通过串行接口进行编程,存储用于上电和芯片复位的用户定义寄存器设置。

AD9522具有12路LVDS输出(分为四组)。任一路800 MHz LVDS输出均可重新配置为两路250 MHz CMOS输出。

每组输出均具有一个分频器,其分频比(从1至32)和相位(粗调延迟)均可以设置。

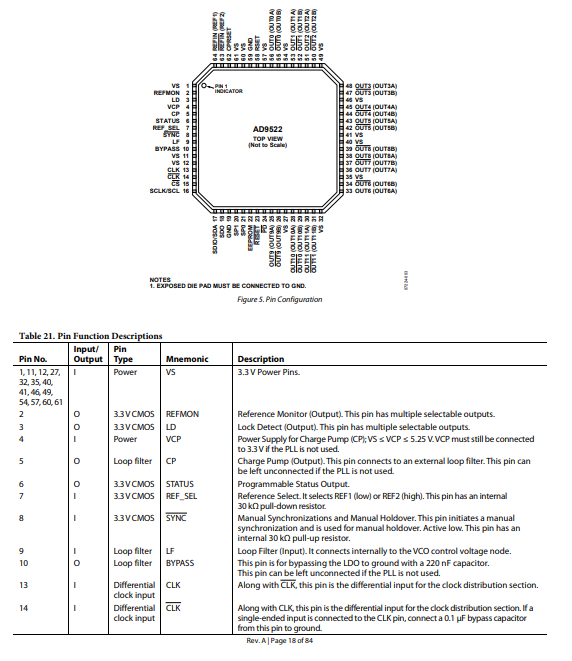

AD9522提供64引脚LFCSP封装,可以采用3.3 V单电源供电。外部VCO的工作电压最高可达5.5 V。

AD9522的额定工作温度范围为−40°C至+85°C标准工业温度范围。

AD9520-3是AD9522-3的等效产品,采用LVPECL/CMOS驱动器而非LVDS/CMOS驱动器。

^1^AD9522在本数据手册中泛指AD9522系列的所有器件。但是,使用AD9522-3时,它仅指AD9522系列的该特定器件。

应用

- 低抖动、低相位噪声时钟分配

- SONET、10Ge、10G FC和其它10 Gbps协议的时钟产生和转换

- 前向纠错(G.710)

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

- 宽带基础设施

特性

- 低相位噪声、锁相环(PLL)

- 片内VCO的调谐频率范围为1.72 GHz至2.25 GHz

- 支持最高2.4 GHz的外部3.3 V/5 V VCO/VCXO

- 1路差分或2路单端基准输入

- 支持最高250 MHz的CMOS、LVPECL或LVDS基准

- 基准输入接受16.62 MHz至33.3 MHz晶振

- 可选基准时钟倍频器

- 欲了解更多信息,请参考数据手册

框图

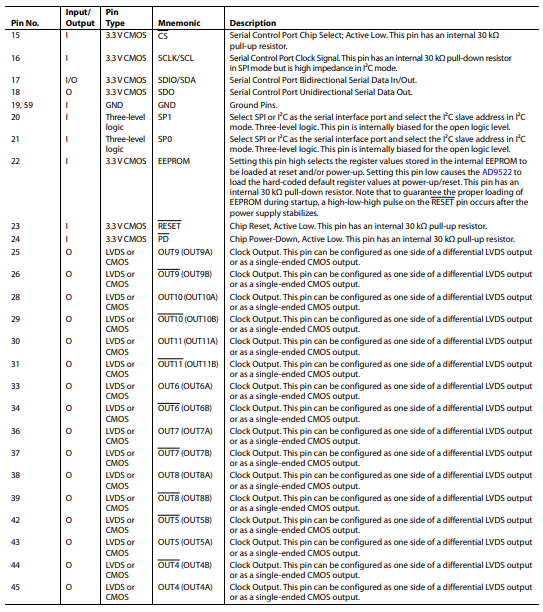

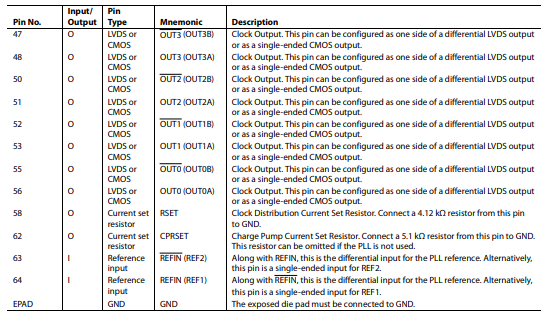

引脚配置描述

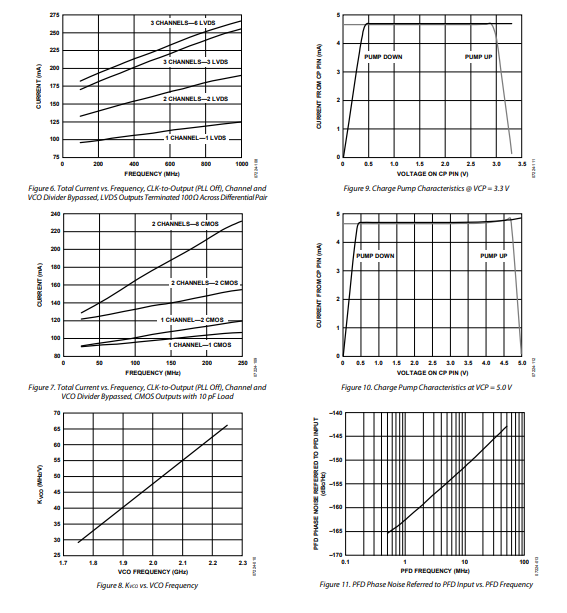

典型性能特征

工作原理

工作配置

AD9522可以通过多种方式进行配置。这些配置必须通过加载控制寄存器来设置(见表49至表60)。每个部分或功能必须通过设置相应寄存器中的适当位进行单独编程。配置完成后,用户可以将这些值存储在片上EEPROM中,以便器件在下次上电时无需用户干预即可实现所需配置。

模式0:内部VCO和时钟分配

使用内部VCO和PLL时,必须使用VCO分频器,以确保在大多数情况下,通道分频器的输入频率不超过其规定的最大频率。此模式的例外情况是VCO直通模式,此时VCO频率≤2000 MHz。通道分频器的最大输入频率为2000 MHz,条件是分频比为3 - 17或3 - 37。如果未按期望进行分频,通道分频器的最大输入频率为1600 MHz。

内部PLL使用外部环路滤波器来设置环路带宽。外部环路滤波器对环路稳定性也至关重要。内部PLL还使用外部环路滤波器来设置环路带宽。外部环路滤波器对环路稳定性同样至关重要。

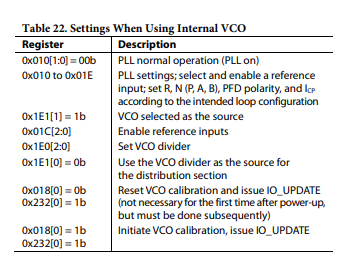

使用内部VCO时,必须校准VCO(寄存器0x018[0] = 1b),以确保最佳性能。有关内部VCO和时钟分配应用的寄存器设置,请参见表22。

-

AD9522-2:高性能时钟发生器的深度剖析2026-03-22 1053

-

AD9522-2 12路LVDS/24路CMOS输出时钟发生器技术手册2025-04-11 1382

-

AD9522-4:12集成1.6 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器2021-04-29 780

-

AD9522-3:12集成2 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器2021-04-28 803

-

AD9522-0:12集成2.8 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器2021-04-17 729

-

AD9520-3:12集成2 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器2021-04-16 879

-

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO2021-03-19 729

-

12路LVDS/24 CMOS输出时钟发生器AD9522-3/PCBZ2019-02-26 2301

-

集成2.2 GHz VCO12路LVDS/24 CMOS输出时钟发生器AD9522-2/PCBZ2019-02-22 2356

-

AD9522-3 12路LVDS/24路CMOS输出时钟发生器,集成2 GHz VCO2019-02-15 477

全部0条评论

快来发表一下你的评论吧 !