ADCLK914超快型SiGe开集HVDS时钟/数据缓冲器技术手册

描述

概述

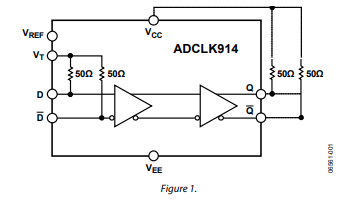

ADCLK914是一款采用ADI公司专利的互补双极性(XFCB-3)硅锗(SiGe)工艺技术制造的超快型时钟/数据缓冲器。ADCLK914具备高压差分信号(HVDS)输出,适合用于驱动ADI最新的高速数模转换器(DAC)。ADCLK914具备单个差分开集输出。

数据表:*附件:ADCLK914超快型SiGe开集HVDS时钟 数据缓冲器技术手册.pdf

ADCLK914缓冲器的工作频率高达7.5 GHz,其传播延迟为160 ps,仅增加110 fs的随机抖动(RJ)。

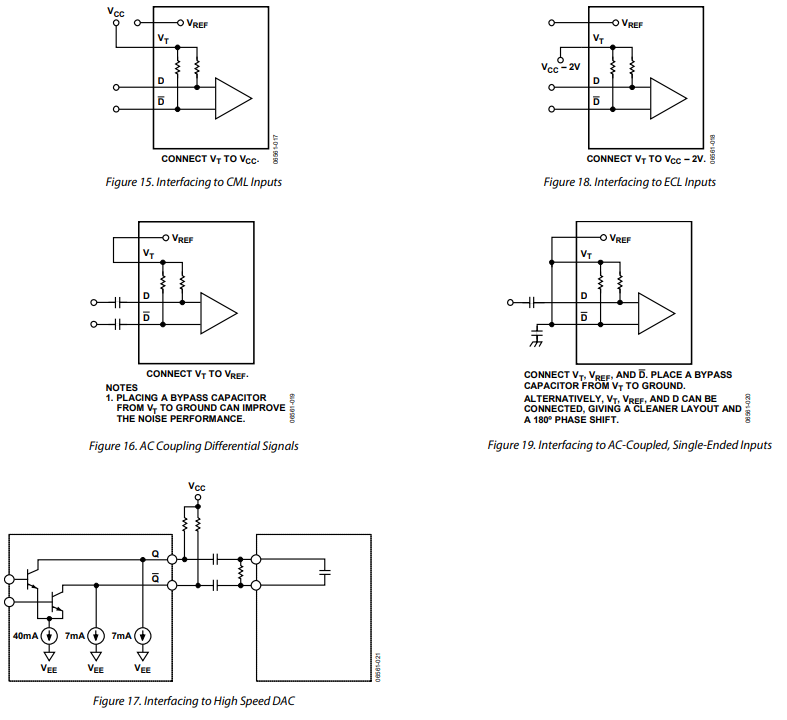

输入具有100 Ω中心抽头片内端接电阻,并接受LVPECL、CML、CMOS、LVTTL或LVDS(仅交流耦合)。VREF引脚可用来为交流耦合输入提供偏置。

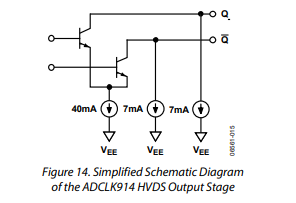

HVDS输出级可以直接将每端1.9 V驱动至端接于VCC的50 Ω传输线路中,从而获得3.8 V的总差分输出摆幅。

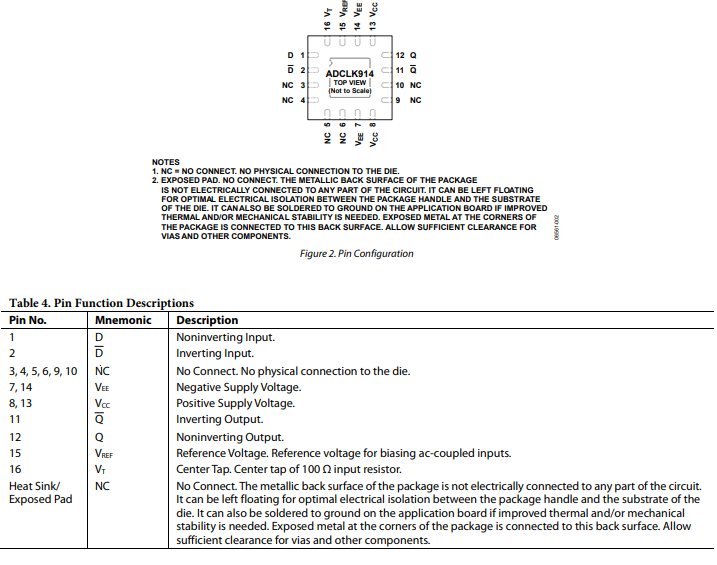

ADCLK914采用16引脚LFCSP封装。额定工作温度范围为扩展的工业温度范围−40°C至+125°C。

应用

- 时钟和数据信号恢复

- 高速转换器时钟

- 宽带通信

- 蜂窝基础设施

- 高速线路接收机

- ATE和高性能仪器仪表

- 电平转换

- 阈值检测

特性

- 7.5 GHz工作频率

- 160 ps传播延迟

- 100 ps输出上升时间/下降时间

- 110 fs随机抖动

- 片内输入端接电阻

- 扩展工业温度范围:

−40°C to +125°C - 3.3 V电源(VCC − V EE )

框图

引脚配置描述

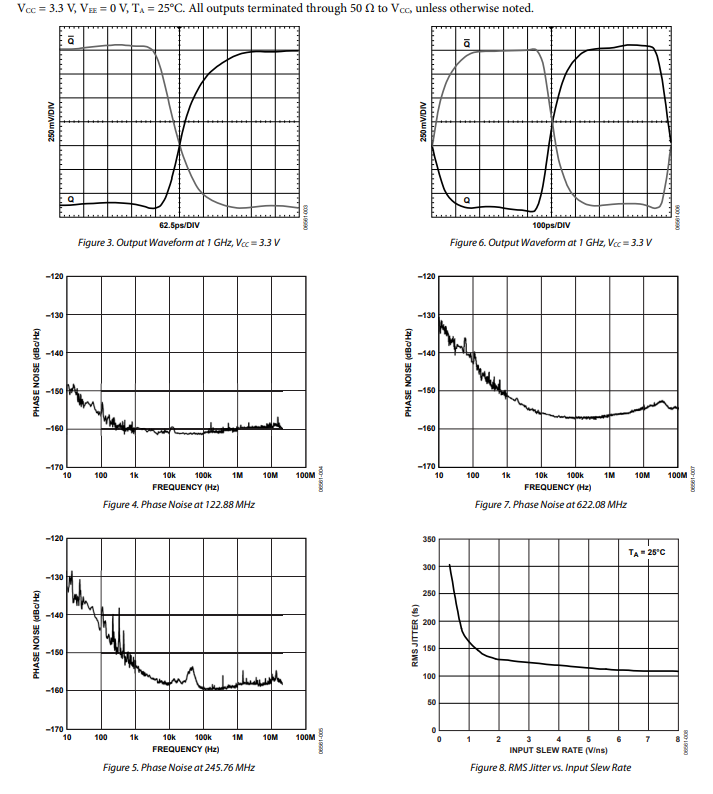

典型性能特征

应用信息

电源/接地布局和旁路

ADCLK914缓冲器专为高速应用而设计。因此,必须采用高速设计技术才能达到规定的性能。对于多层电路板的负电源(V_{EE})和正电源(V_{CC})层,使用低阻抗电源层至关重要。提供最低电感的开关电流返回路径可确保目标应用获得最佳性能。

充分旁路输入和输出电源也很重要。在接地层几英寸范围内放置一个1 μF电解旁路电容。此外,放置多个高质量的0.001 μF旁路电容,尽可能靠近每个**V_{CC}**电源引脚,并通过冗余过孔将电容连接到接地层。仔细选择高频旁路电容,以实现最低电感和等效串联电阻(ESR)。为提高高频旁路效率,尽量减少寄生布局电感。

大电流会在**V_{EE}和V_{CC}**引脚处产生显著的寄生电感。应严格避免器件被ADCLK914驱动时出现这种情况。

LVDS输出级

ADCLK914可提供与任何CMOS器件的双极接口。输出可直接连接到接收器件的输入,也可放置在靠近时钟分配树的位置,以实现单端CMOS和PECL电平。

互连线必须短且精心设计,因为单端端接设计在电压较低的双端端接传输技术方面余量较小。

与高速DAC接口

ADCLK914旨在驱动高幅度、低抖动时钟信号进入高速、多输入(MIPI)的DAC。ADCLK914应放置在尽可能靠近时钟输入的DAC位置,以便高斜率和高幅度时钟信号能够到达这些器件,且不会导致占空比失真。

优化高速性能

与任何高速电路一样,正确的设计和布局技术对于实现预期的特定性能至关重要。串扰、电容、电感、电感耦合以及其他寄生效应会导致信号完整性问题,进而严重影响输入和输出传输线的性能,还可能降低输出斜率。

输入和输出匹配对性能有显著影响。ADCLK914缓冲器提供内部50 Ω端接电阻,用于两个Buff D和D输出。通常,返回引脚连接到提供的参考引脚,或连接到与不同PECL一起使用时为V_{CC} - 2 V的汇点,或与标准或低摆幅PECL、CML、CMOS或LVTTL源一起使用时为**V_{CC}**的汇点,如图15所示。

注意,ADCLK914 **V_{CC}电源应持续监控,以避免因V_{CC}或V_{EE}**瞬间短路以及电容充电电流而造成损坏,因为这些情况会使电源无法充分供电。

仔细使用陶瓷电容旁路端接电位,以防止寄生电感对输入信号产生不必要的干扰。由于输入直接耦合到源,必须注意确保引脚处于指定的差分和共模范围内。

如果返回引脚浮空,器件将呈现100 Ω交叉端接,但此时信号源必须控制共模电压并提供输入偏置电流。

输入引脚之间设有静电放电(ESD)/钳位二极管,以防止输入晶体管产生过大偏移。ESD二极管并非针对最佳性能进行优化。如果需要钳位,建议使用合适的外部二极管。

随机抖动

ADCLK914缓冲器经过专门设计,可在较宽的输入斜率范围内将额外的随机抖动降至最低。只要有可能,应使用快速肖特基二极管衰减器来降低过大输入信号的斜率,因为衰减器应采用低损耗电介质或具有良好高频特性的电缆。

典型应用电路

-

高速电路的理想之选:ADCLK905/ADCLK907/ADCLK925 ECL时钟/数据缓冲器2026-03-22 575

-

ADCLK905超快型SiGe ECL时钟/数据缓冲器技术手册2025-04-14 1531

-

ADCLK950 2路可选输入、10路LVPECL输出、SiGe时钟扇出缓冲器技术手册2025-04-11 1229

-

ADCLK914 mu中的dll一直锁不定是怎么回事?2023-12-13 671

-

EVAR-ADCH914 ADCLK914评估板2021-06-08 731

-

ADCLK914:超高速、SiGe、开放采集器HVDS时钟/数据缓冲器数据表2021-05-26 1109

-

ADCLK954:两个可选输入、12个LVPECL输出、SiGe时钟扇出缓冲器数据表2021-04-25 1093

-

ADCLK946:六路LVPECL输出,SiGe时钟扇出缓冲器数据表2021-04-19 1405

-

ADCLK914输出功率过小2018-11-30 2305

-

超快SiGe集电极开路HVDS时钟/数据缓冲区adclk914数据表2017-10-20 1224

-

ADCLK914,pdf datasheet (HVDS C2009-09-15 876

全部0条评论

快来发表一下你的评论吧 !