Microchip通过设计内signoff DRC在成熟节点定制IC设计中实现显著的生产率提升

EDA/IC设计

描述

Microsemi Corporation (Microsemi) 是 Microchip Technology Inc. 的全资子公司,致力于为通信、国防和安防、航空航天和工业市场提供全面的半导体和系统解决方案组合。其产品包括高性能和抗辐射模拟 / 混合信号集成电路、FPGA、SoC 和 ASIC。此外,他们还设计电源管理产品、时序和同步设备、语音处理设备、射频 (RF) 解决方案、企业存储和通信解决方案、安防技术和可扩展的防篡改产品,以及以太网解决方案。设计面向多个行业和应用的产品,要求 Microsemi 设计人员在成熟的和领先的技术节点上开展工作。

设计和电子设计自动化 (EDA) 社区非常了解先进技术节点(20nm 及以下)设计规则检查 (DRC) 收敛的复杂性并提供了有效的支持。版图设计人员和 CAD 工程师利用多种工具,例如 Calibre RealTime 平台和 Calibre nmDRC Recon 早期设计 DRC 工具,来加速他们的 DRC 收敛过程,从而将其流片计划缩短数周之多。

然而,成熟节点设计仍旧需要相当的时间才能实现 DRC 收敛,这一点却少为人知。对于任何定制版图设计人员而言,将其时间用在优化设计以满足所需的功耗、性能和面积 (PPA) 指标上,才是最有利可图的。而花费在查找和修复 DRC 错误上的每一分钟都会占用进行设计 PPA 分析和优化的宝贵时间。即使是设计人员对小型单元、模块或大型单元的局部窗口运行 DRC,输出 GDSII 文件和启动批处理 DRC 运行的相关开销(包括等待计算场提供充足资源所需的时间)最终也会占用几分钟而不是几秒钟的时间。虽然在一次运行中,这些时间看起来并不多,但在设计流片周期中,这些小段时间累加起来动辄就在总周期时间内占用几周时间——而这些时间可以有更好的用途,即增强设计以提升盈利能力。

Microsemi DRC 流程

Microsemi 拥有强大的 Calibre nmDRC 批处理流程,而且该流程已针对其 signoff DRC 运行进行了优化。他们希望通过在设计流程的早期启用 signoff 质量的设计内 DRC 来进一步提高其 DRC 生产率。该流程的目标是让设计人员有时间和有能力快速对可能的修改执行更多假设分析,以便修复设计期间的 DRC 错误,支持设计人员实施可为其设计提供最佳优化的修复,同时确保修复内容仍旧不含任何 DRC 错误。

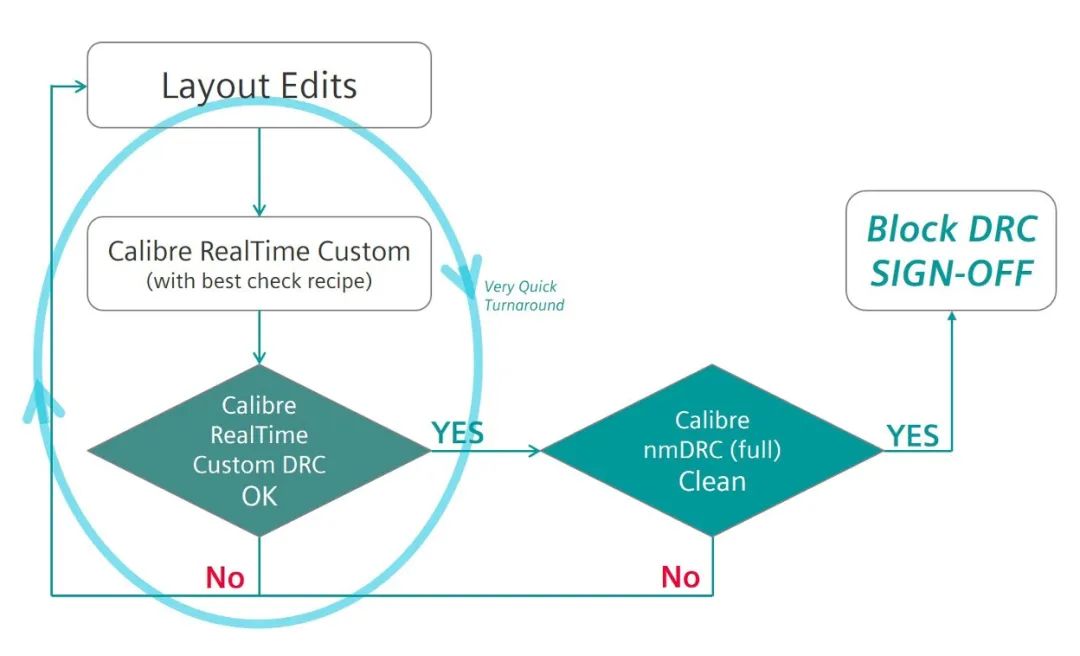

利用 Calibre RealTime Custom 界面可在定制和模拟 / 混合信号 (AMS) 设计流程期间实现 signoff 质量的设计内 Calibre DRC,提供有关设计规则违规的即时反馈和可制造性设计 (DFM) 合规建议,从而提高总体设计速度和结果质量。当集成到定制 / AMS IC 设计和版图系统时, Calibre RealTime Custom 界面可直接调用 Calibre 分析引擎,运行经过晶圆代工厂认证的 Calibre 规则集。这些 Calibre 引擎在所编辑的形状附近进行快速的递增式检查,对设计规则违规以及潜在的系统变化易感性(通过推荐的规则合规性来衡量)提供即时反馈。借助这些在版图设计期间随时可用的信息,设计人员无需进行大量耗时费力的设计验证迭代就能快速分析并优化设计的 PPA 指标,并充分相信修复内容不含任何 DRC 错误(图1)。

▲ 图1. Calibre RealTime Custom 平台通过将 sign-off 质量的 Calibre DRC 纳入定制 / AMS 设计创建过程,彻底颠覆了传统的版图验证仿真循环。

Calibre RealTime Custom 界面还使设计人员能够选择适用于当前设计阶段的定制检查集(检查集合)(图2)。设计人员可凭借此选项,优先执行系统化的 DRC 调试,直接加快 DRC 收敛速度。

▲ 图2. Microsemi 的 Calibre RealTime Custom 设计内 DRC 流程。

结果

金属层和过孔层的局部编辑

Microsemi 设计人员在其定制设计流程中,对 28nm 设计中的 Metal1、VIA1 和 Metal2 层进行了工程变更单 (ECO) 编辑。设计的 GDSII 大小为 0.5 GB,包含数以百万计的几何形状。转出成整个 GDSII 并运行批处理 DRC,以便在 Metal1、VIA1 和 Metal2 层执行 ECO 更改,这一过程不仅耗时而且乏味。相反,Microsemi 设计人员使用 Calibre RealTime Custom 界面在进行了 ECO 更改的局部设计窗口中执行实时 DRC 检查。使用 Calibre RealTime Custom 设计内 DRC 还消除了运行中间批处理 DRC 的需求。

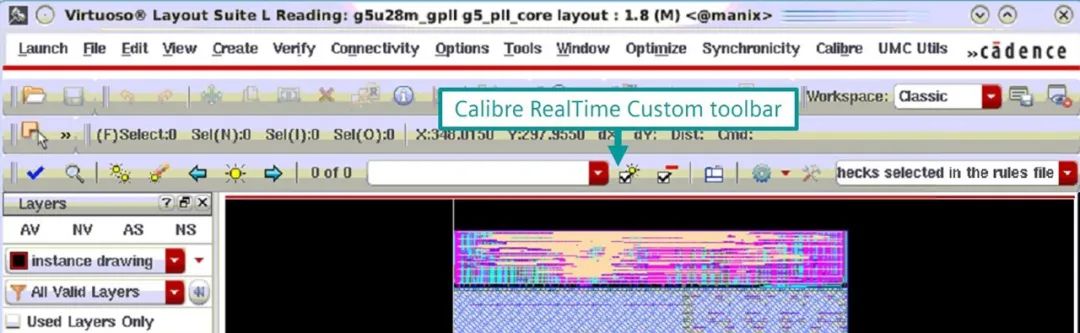

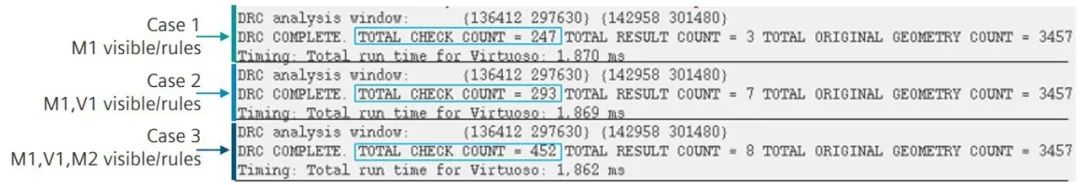

此外,Microsemi 设计人员还利用 Calibre RealTime Custom 工具强大的内置检查集合大幅减少了执行的 DRC 检查数量,这不仅加快了 DRC 运行速度,而且减少了生成的相关 DRC 结果,从而让 DRC 调试也变得更加轻松和快速。设计人员在他们的设计环境中使用集成的 Calibre RealTime Custom 工具栏(图3)来选择内置的可见层检查集合,打开 Metal1、Via1 和 Metal2 层的可见性,以及关闭所有其他层。使用可见层检查集合,无需任何特殊设置便可立即将检查数量从超过 5,500 次减少到仅 250 次。

▲ 图3. 集成的 Calibre RealTime Custom 工具栏简化了调用和选项的选择。

Microsemi 设计人员还可以使用工具栏选项来切换 Metal1、Via1 和 Metal2 层的各种组合的可见性,并放大到进行过编辑并且已准备好运行设计内 DRC 的局部区域。查看三层组合的结果显示,每种情况的 Calibre RealTime Custom DRC 运行时间均不到 2 秒(图 4)。相比之下,在同一设计区域运行批处理 DRC 作业所用的运行时间从 2 分钟(单次检查)到 16 分钟不等。

图 5 显示了针对图 4 所示三种情况运行单次迭代时, Calibre RealTime Custom 和批处理 DRC 的结果比较。在设计周期的过程中,设计人员通常会运行多个批处理 DRC 迭代。对于 Microsemi 而言,通过使用 Calibre RealTime Custom 设计内 DRC(可以重新转用于其他验证任务)和消除运行中间批处理 DRC 的需求,所节省的时间使得估计的总体生产率提高了 2-4 倍,从而将其成熟节点设计的流片计划缩减了数周之多。

▲ 图4. 选定层组合的 Calibre RealTime Custom 运行时间和结果。

▲ 表1. 28nm 设计的 Calibre RealTime Custom 和批处理 DRC 运行时间比较。

虽然乍看之下,批处理运行所花费的时间显然要比设计内检查更长,但深入挖掘后可以发现一些令人意外的数据。如图 5 所示,编写 GDSII 所需的时间(转出时间)和 Calibre 运行时间都只用了几秒钟。这些短暂的时间都在意料之中,因为设计人员是对设计的局部窗口转出版图和运行 Calibre。但是,批处理 DRC 总计运行时间却在 2 到 16 分钟之间。每次启动运行时编译 Calibre 28nm DRC 规则文件需要 15-30 秒,但大部分剩余时间基本都花费在排队等待计算平台提供机器来执行运行上。日益紧张的流片计划加上这一周转时间 (TAT) 的增加,严重制约了设计人员可用于尝试和实施最佳 DRC 修复的时间。

Calibre RealTime Custom 界面的执行速度很快,因为它不仅是在启动设计环境的同一台机器上运行,而且还直接针对内存中的 OpenAccess(OA) 设计数据运行,同时不需要将 GDSII 写入到磁盘。此外,每个设计工具会话仅编译一次 Calibre DRC 规则集,并且设计人员可利用检查集合,仅仅运行与其当前设计需求相关的检查。通过消除等待资源的时间,设计人员可获得更多的时间来执行假设分析,以及实施可优化设计 PPA 的修复。

▲ 图5. 对批处理 Calibre DRC 运行时间进行的分析表明,花费在等待可用 CPU 上的时间占总运行时间的一大部分。

流片

在流片阶段,设计人员最终几乎总是在特定区域或针对特定模块执行关键的物理验证 (PV) 和调试。例如,他们可能需要快速修复最后时刻发现的 DRC 错误,查看 DRC / DFM 结果的计数和准确性,查看用于检查设计可制造性 / 良率的其他规则的结果,或者比较由特定检查指定的不同值以确定修复 DRC 错误的最佳方法。

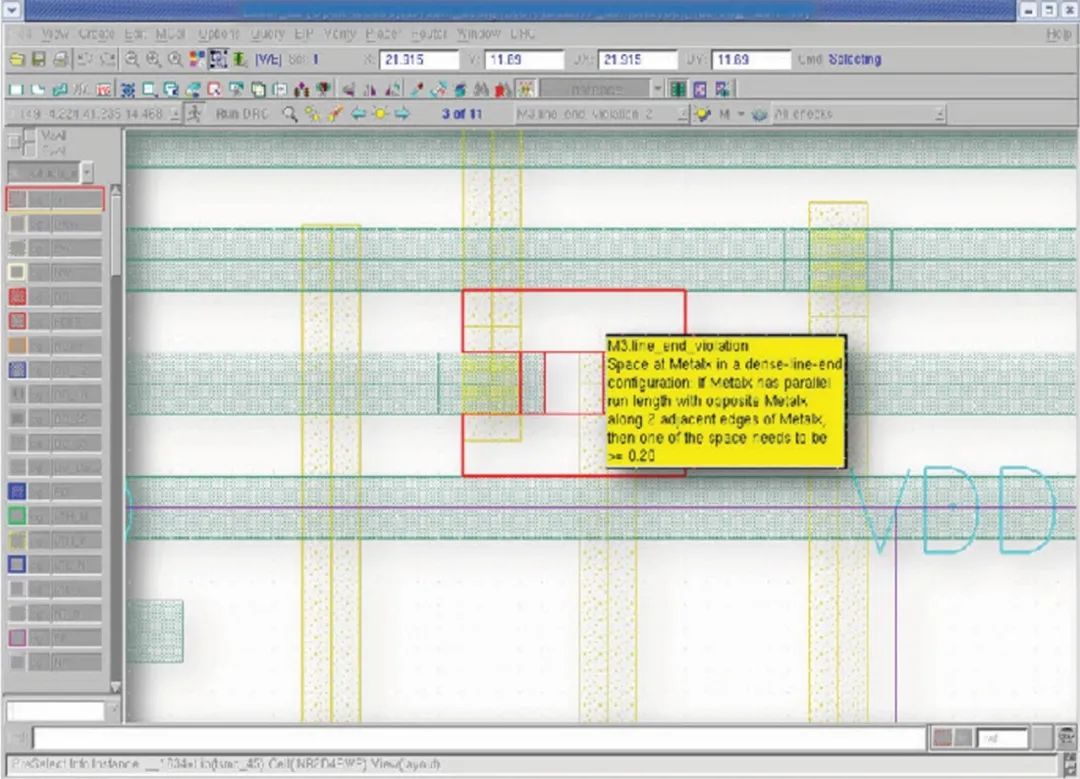

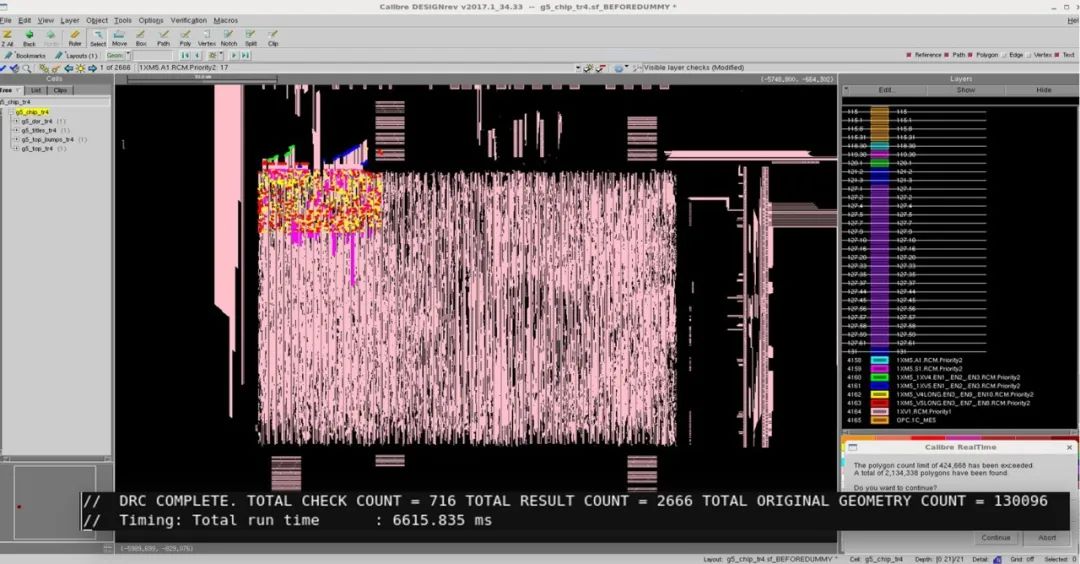

Microsemi 首先使用 Calibre DESIGNrev 版图查看器的快速加载和渲染功能来加载整个设计。然后,设计人员使用 Calibre DESIGNrev 编辑功能对 DRC 错误应用修复,并使用 Calibre RealTime Custom 的设计内 DRC 来获得有关这些修复的实时 DRC 反馈(图 6)。这种快速反馈不仅确认了这些修复不含任何 DRC 错误,还为设计人员提供了必要时执行多次修复的时间,以通过迭代方式获得最佳解决方案。

▲ 图6. 在流片阶段,在 Calibre DESIGNrev 查看器中使用 Calibre RealTime Custom 设计内 DRC 进行物理验证审查。

Microsemi 率先使用成熟和先进的工艺节点设计创新型芯片,并应用于各行各业的多种用途。在成熟节点的定制设计实现中,版图设计人员仍需要将大量宝贵的时间花费在修复 DRC 错误上——但是,如果可以将这些时间花费在确保其设计达到 PPA 目标,将可以获得更好的效益。分析表明,批处理 DRC 周期中花费的大部分时间不过是在队列中等待所需的计算资源来完成批处理 DRC 运行。通过在定制版图编辑和查看环境中使用 Calibre RealTime Custom 界面提供的 signoff 质量的实时 DRC 反馈来取代中间批处理 DRC 运行,Microsemi 设计人员能够大幅减少运行 DRC 和验证修复所需的时间。

Microsemi 不仅将其总体 DRC 生产率提高了 2-4 倍,同时还通过实施优化设计 PPA 的 DRC 修复,提高了其版图设计的质量。通过加快设计的 DRC 收敛速度并将流片时间缩短数周,Microsemi 得以实现率先上市的目标并从中获益,与此同时,还提高了他们提供经过 PPA 优化的设计的能力,而这有助于确保他们的产品达到甚至超越市场预期。

-

将MCL算法应用于无线传感网络节点定位技术2018-11-16 1649

-

阻碍PCB设计流程的生产率2019-10-14 16549

-

Fusion Design Platform™已实现重大7nm工艺里程碑2020-10-22 2380

-

数字IC后端设计介绍,写给哪些想转IC后端的人!2020-12-29 4386

-

人工智能通过创造新就业岗位和改善当前岗位现状来大幅提升生产率2019-01-17 2685

-

PADS VX版如何提高全流程的设计生产率2019-05-20 3948

-

PADS为射频和微波设计提高生产率2019-05-15 3619

-

MOSIS在领先的FinFET工艺设计中为DRC和LVS signoff部署IC Validator2019-07-30 4935

-

无线传感器网络节点定位是什么2019-10-16 8098

-

使用PCB公差提高生产率2020-09-29 3350

-

无线传感器网络节点定位算法研究与实现2021-05-24 1171

-

使用Infinity和InfinityXT探针提高生产率2022-07-15 1845

-

DRC分析和修复经验分享2023-11-02 5130

全部0条评论

快来发表一下你的评论吧 !