AD9517-4 12路输出时钟发生器,集成1.6GHz VCO技术手册

描述

概述

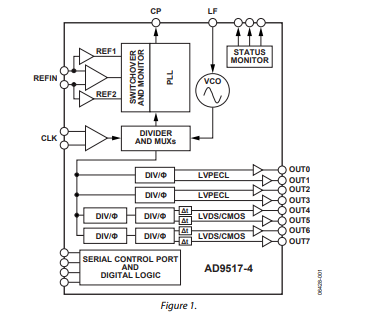

AD9517-4提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.45 GHz至1.80 GHz。也可以使用高达2.4 GHz的外部VCO/VCXO。

数据表:*附件:AD9517-4 12路输出时钟发生器,集成1.6GHz VCO技术手册.pdf

AD9517-4具有出色的低抖动和相位噪声特性,可极大地提升数据转换器的性能,并且也有利于其它相位噪声和抖动要求严苛的应用。

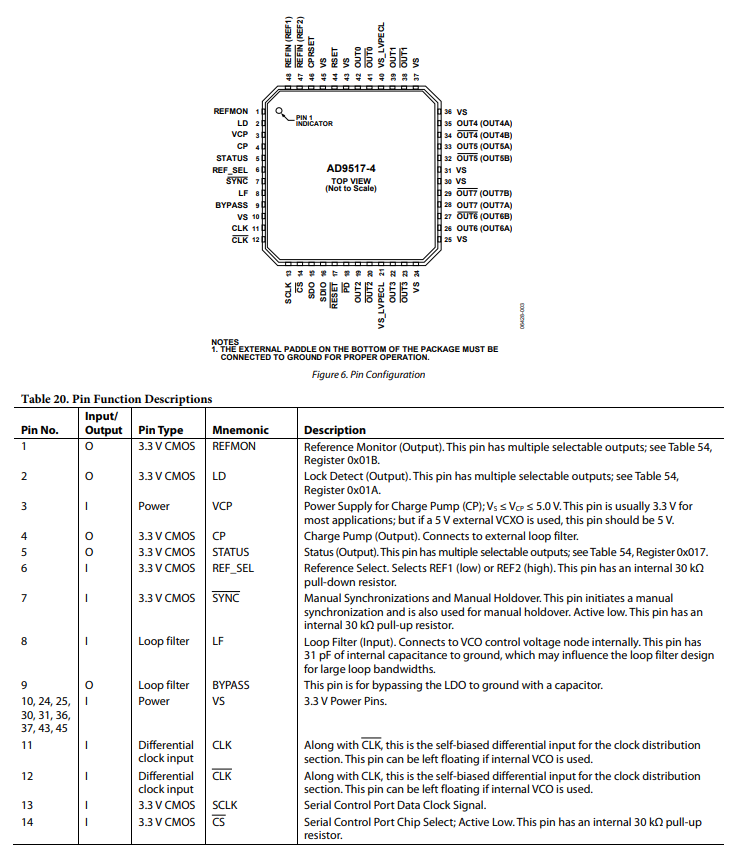

AD9517-4具有四路LVPECL输出(分为两对)和四路LVDS输出(分为两对)。可以将每路LVDS输出重新配置为两路CMOS输出。LVPECL输出的工作频率达1.6 GHz,LVDS输出的工作频率达800 MHz,CMOS输出的工作频率达250 MHz。

每对输出均有分频器,其分频比和粗调延迟(或相位)均可以设置。LVPECL输出的分频范围为1至32。LVDS/CMOS输出的分频范围最高可达1024。

AD9517-4提供48引脚LFCSP封装,可以采用3.3 V单电源供电。将电荷泵电源(VCP)与5V电压相连时,可以使用外部VCO,它需要更宽的电压范围。独立的LVPECL电源可以为2.5 V至3.3 V(标称值)。

AD9517-4的额定工作温度范围为−40°C至+85°C工业温度范围。

应用

- 低抖动、低相位噪声时钟分配

- 10/40/100 Gb/s网络线路卡,包括SONET、同步以太网、OTU2/3/4

- 前向纠错(G.710)

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

特性

- 低相位噪声、锁相环

片内VCO的调谐频率范围为1.45 GHz至1.80 GHz

可选外部VCO/VCXO,最高达2.4 GHz

1路差分或2路单端基准输入

参考监控功能

自动/手动基准电压源切换/保持模式

自动从保持状态恢复

支持最高250 MHz的LVPECL、LVDS或CMOS基准

可编程PFD路径延迟

可选数字或模拟时钟检测 - 两对1.6 GHz LVPECL输出

每对输出共用1至32分频器和粗调相位延迟

加性输出抖动:225 fS均方根值

通道间偏斜成对输出小于10 ps - 两对800 MHz LVDS时钟输出

每对输出共用两个级联的1至32分频器和粗调相位延迟

加性输出抖动:275S均方根值

可以精调每路LVDS输出的延迟(Δt) - 8路250 MHz CMOS输出(每路LVDS输出对应两路)

- 上电时所有输出自动同步

- 欲了解更多特性,请参考数据手册

框图

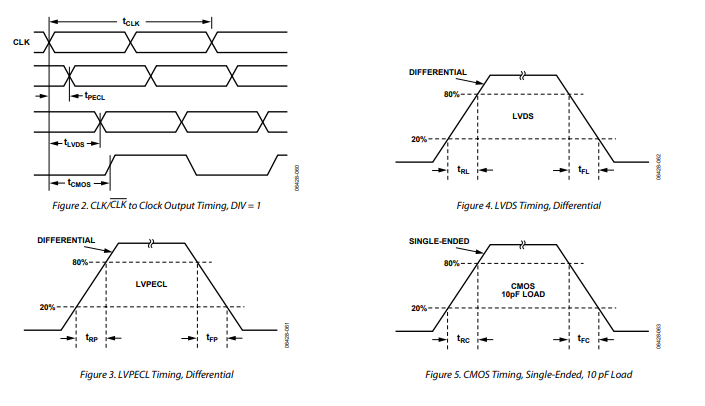

时序图

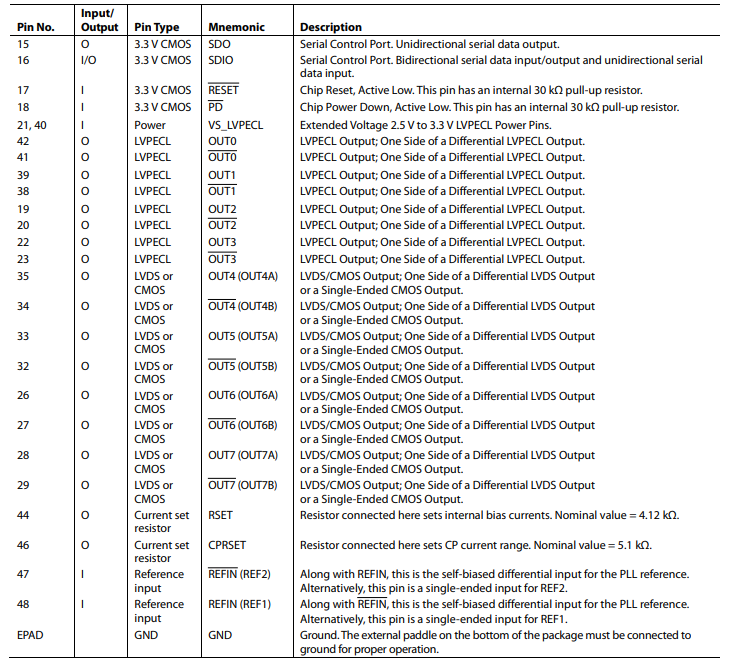

引脚配置描述

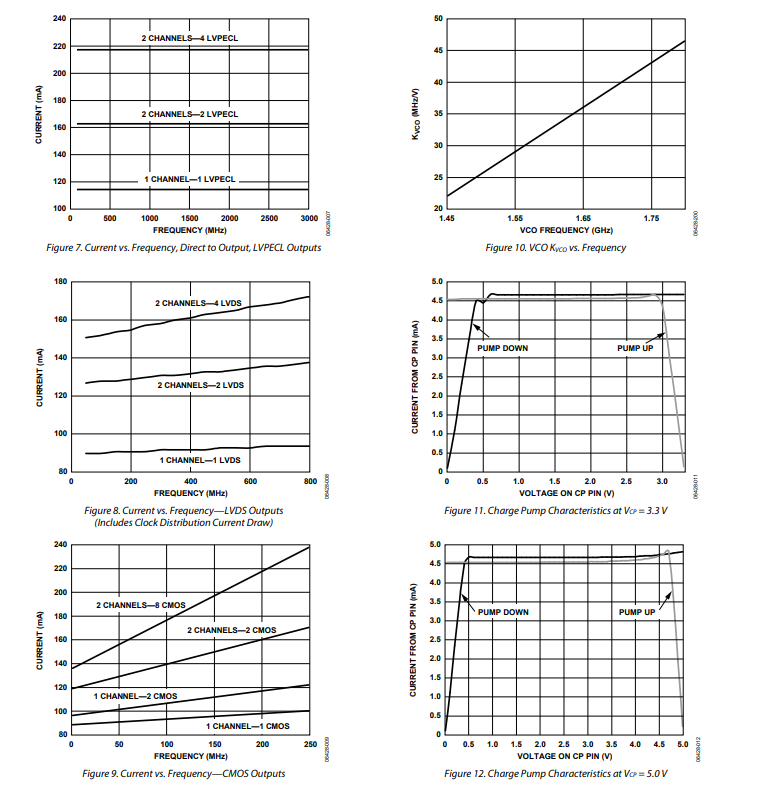

典型性能特征

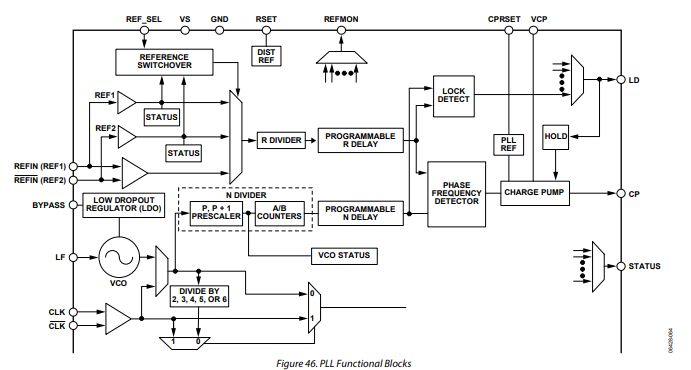

锁相环(PLL)

AD9517集成了片内锁相环(PLL)和片内压控振荡器(VCO)。PLL模块既可以与片内VCO配合使用,构建完整的锁相环路,也可以与外部VCO或压控晶体振荡器(VCXO)搭配。PLL需要一个外部环路滤波器,该滤波器通常由少量电容和电阻组成。环路滤波器的配置和组件对于确立工作PLL的环路带宽和稳定性至关重要。

AD9517的PLL在从输入参考频率生成时钟频率方面非常有用。这包括将参考频率转换为更高频率,以便进行后续的分频和分配。此外,PLL还可用于清理输入抖动,并抑制噪声参考信号的相位噪声。PLL的确切参数和锁定动态特性因应用而异。AD9517的PLL具有高度的灵活性和深度,能够在众多不同的应用和信号环境中发挥作用。

PLL的配置

AD9517允许对PLL进行灵活配置,以适应各种参考频率、鉴频鉴相器(PFD)比较频率、VCO频率(内部或外部VCO/VCXO)以及锁相环动态特性。这是通过多种设置实现的,包括R分频器、N分频器、PFD极性(仅适用于外部VCO/VCXO)、防反冲脉冲宽度、电荷泵电流、内部VCO或外部VCO/VCXO的选择,以及环路带宽。这些设置通过可编程寄存器进行管理(见表52和表54),同时也与外部环路滤波器的设计相关。

PLL的成功运行和良好性能在很大程度上取决于PLL设置的正确配置。外部环路滤波器的设计对于PLL的正常运行至关重要。深入了解PLL理论和设计有助于优化性能。ADIsimCLK™(V1.2或更高版本)是一款免费程序,可帮助进行AD9517的设计,探索其功能特性,并设计PLL环路滤波器,可在www.analog.com/clocks获取。

鉴频鉴相器(PFD)

PFD接收来自R计数器和N计数器的输入,并产生与二者之间相位和频率差成比例的输出。PFD包括一个可编程延迟元件,用于控制防反冲脉冲的宽度。该脉冲可确保PFD传输功能中不存在死区,并将参考杂散降至最低。防反冲脉冲宽度由寄存器0x017[1:0]设置。

需要注意的是,PFD存在允许的最大频率限制,这反过来又决定了正确的防反冲脉冲设置。防反冲脉冲设置在表2的鉴频鉴相器参数中有详细说明。

-

AD9517-0:高性能多输出时钟发生器的全面解析2026-03-22 819

-

集成2.2 GHz压控振荡器数据表的AD9517-2 12输出时钟发生器2021-06-17 913

-

AD9517-0 12输出时钟发生器,集成2.8 GHz压控振荡器数据表2021-06-16 957

-

AD9517-4:12输出时钟发生器,集成1.6 GHz压控振荡器数据表2021-04-30 820

-

集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出时钟发生器2021-04-29 854

-

AD9517-2:12输出时钟发生器,集成2.2 GHz压控振荡器数据表2021-04-13 873

-

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO2021-03-19 730

-

AD9520-3BCPZ时钟发生器2019-07-09 1048

-

AD9517-4 12路输出时钟发生器,集成1.6 GHz VCO2019-02-15 887

全部0条评论

快来发表一下你的评论吧 !