AD9518-0 6路输出时钟发生器,集成2.8GHz VCO技术手册

描述

概述

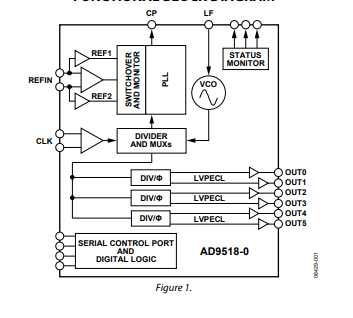

AD9518-0提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成PLL和VCO。片内VCO的调谐频率范围为2.55 GHz至2.95 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

数据表:*附件:AD9518-0 6路输出时钟发生器,集成2.8GHz VCO技术手册.pdf

AD9518-0强调低抖动和相位噪声以实现数据转换器的优质性能,同时能够满足其他应用所需的严格相位噪声和抖动要求。

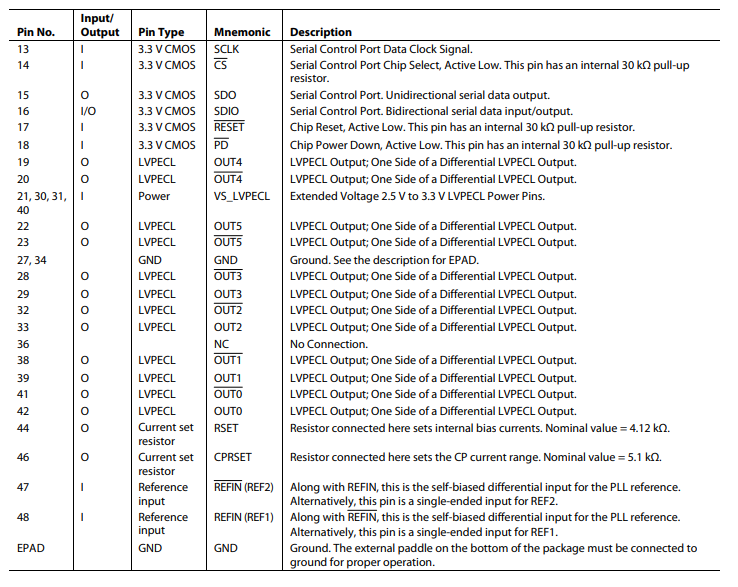

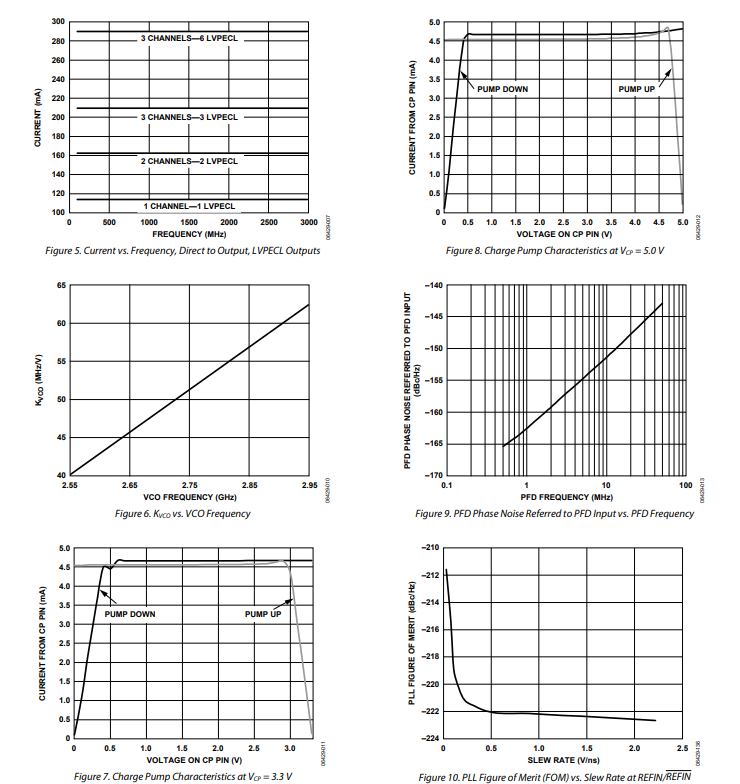

AD9518-0具有六路LVPECL输出(分为三组)。LVPECL输出的工作频率可达1.6 GHz。

对于需要额外输出、晶体参考输入、零延迟或EEPROM以便在启动时自动配置的应用,可使用[AD9520]和[AD9522]。

此外,[AD9516]和[AD9517]类似于[AD9518],但具有不同的输出组合。

每对输出均有分频器,其分频比和粗调延迟(或相位)均可以设置。LVPECL输出的分频范围为1至32。

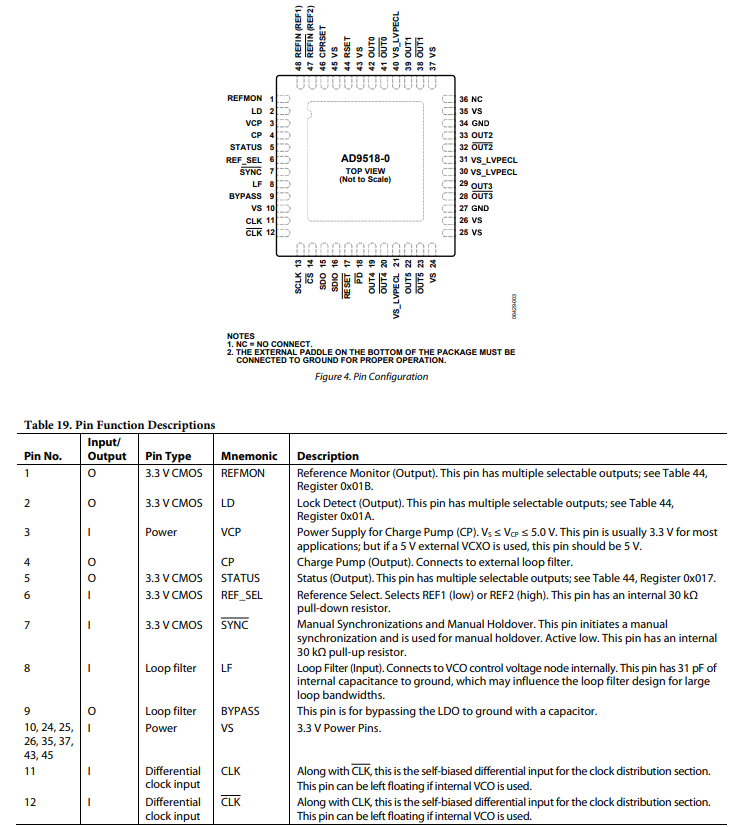

AD9518-0提供48引脚LFCSP封装,可以采用3.3 V单电源供电。将电荷泵电源(VCP)与5V电压相连时,可以使用外部VCO,它需要更宽的电压范围。独立的LVPECL电源可以为2.5 V至3.3 V(标称值)。

AD9518-0的额定工作温度范围为–40°C至+85°C工业温度范围。

应用

- 低抖动、低相位噪声时钟分配

- 10/40/100 Gb/s网络线路卡,包括SONET、同步以太网、OTU2/3/4

- 前向纠错(G.710)

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

特性

- 低相位噪声锁相环(PLL)

- 片内VCO的调谐频率范围为2.55 GHz至2.95 GHz

- 可选外部VCO/VCXO,最高达2.4 GHz

- 1路差分或2路单端参考输入

- 参考监控功能

- 自动恢复和手动基准电压源切换/保持模式

- 支持最高250 MHz的LVPECL、LVDS或CMOS基准

- 可编程PFD路径延迟

- 可选数字或模拟锁定检测

- 3对1.6 GHz LVPECL输出

- 每对输出共用1至32分频器和粗调相位延迟

- 加性输出抖动:225 fs均方根值

- 通道间偏斜成对输出小于10 ps

- 上电时所有输出自动同步

- 提供手动输出同步

- 采用48引脚LFCSP封装

框图

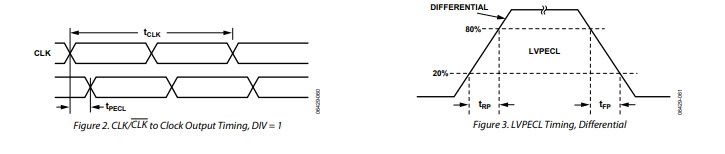

时序图

引脚配置描述

典型性能特征

操作理论

工作配置

AD9518 有多种配置方式。这些配置必须通过加载控制寄存器(见表 42 和表 43 至表 49)来设置,每个部分或功能必须通过在相应控制寄存器中设置合适的位来单独编程。

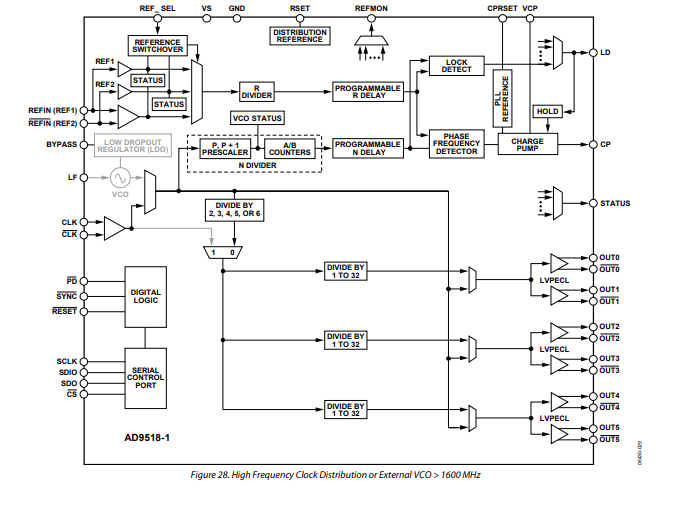

高频时钟分配——CLK 或外部 VCO > 1600 MHz

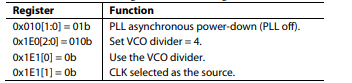

AD9518 上电默认配置下,PLL 处于断电状态(PLL 关闭),并且路由分配设置为 CLK/CLK 输入连接到通道分频器的分配输出,通过通道分频器可将输入信号分频至 2.4 GHz(见通道 3)。可以应用于通道分频器的最大频率为 1600 MHz,因此,在使用通道分频器进行较低频率输入之前,必须先对更高频率的输入进行降频处理,但在使用通道分频器之前,最小分频比为 2。

当 PLL 启用时,这种路由方式还允许使用外部 VCO 或 VCXO 的 PLL,其频率小于 2400 MHz。在此配置中,内部 VCO 未使用且处于断电状态。外部 VCO/VCXO 直接接入预分频器。

表 20 中显示的寄存器设置是这些寄存器在上电时或复位后的默认值。在电源启动或复位后,也可以有意将这些寄存器设置为这些值。

在对相应的寄存器值进行编程后,必须将寄存器 0x232 设置为 0x01 才能使这些值生效。

表 20. 部分 PLL 寄存器的默认设置

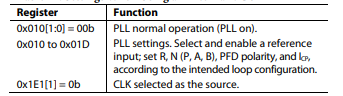

当使用带有外部 VCO 的内部 PLL 时,必须启用 PLL。

表 21. 使用外部 VCO 时的设置

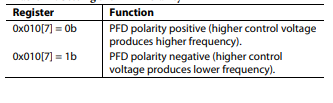

外部 VCO 需要一个必须连接在 CP 和 VCO 调谐引脚之间的外部环路滤波器。该环路滤波器决定了 PLL 的环路带宽和稳定性。确保为正在使用的 VCO 选择合适的 PFD 极性。

表 22. 设置 PFD 极性

-

AD9518-0:高性能6输出时钟发生器的深度剖析2026-03-22 1090

-

AD9517-0 12路输出时钟发生器,集成2.8GHz VCO技术手册2025-04-14 1321

-

集成2.0 GHz压控振荡器数据表的AD9518-3 6输出时钟发生器2021-06-17 885

-

AD9517-0 12输出时钟发生器,集成2.8 GHz压控振荡器数据表2021-06-16 1003

-

AD9518-3:6输出时钟发生器,集成2.0 GHz压控振荡器数据表2021-04-13 974

-

AD9518-1:6输出时钟发生器,集成2.5 GHz压控振荡器数据表2021-03-22 1008

-

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO2021-03-19 762

-

AD9518-0: 6-Output Clock Generator with Integrated 2.8 GHz VCO Data Sheet2021-01-28 777

-

AD9518-0 6路输出时钟发生器,集成2.8 GHz VCO2019-02-15 340

全部0条评论

快来发表一下你的评论吧 !