高速SSD存储系统中数据缓存控制器整体顶层设计

描述

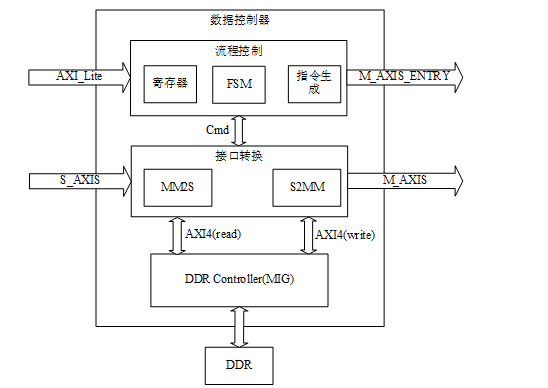

数据缓存控制器主要实现了对大量突发数据的缓存、AXI4接口与AXI4-Stream接口之间的转换和NVMe命令的生成等功能。数据缓存控制器的整体架构如图1所示。

图1数据缓存控制器整体架构

根据功能需求将数据缓存控制器划分为了3个模块:流程控制模块、接口转换模块和MIG模块。

(1)流程控制模块:流程控制模块主要实现三个功能,一是根据用户命令或输入的数据量大小来组装相应的NVMe提交命令,并发送至NVMe Host控制器;二是控制接口转换模块工作的开启与关闭;三是实现乒乓操作,来提高系统传输性能。

(2)接口转换模块:接口转换模块负责完成将DDR控制器的AXI4接口转换为与其他模块进行数据交互的AXI4-Stream接口。

(3)MIG模块:MIG 模块是Xilinx提供的DDR存储控制器,可以帮助用户快速的搭建工程,完成对DDR等外部存储器的控制。MIG IP核内部由用户接口、存储控制器和物理层模块三部分组成。同时MIG IP还支持AXI4接口,用户可以直接通过AXI4接口访问DDR存储器。

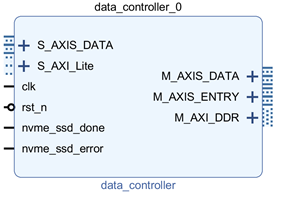

如图2所示,它为数据缓存控制器的顶层模块框图。

图2 数据缓存控制器的顶层模块框图

数据缓存控制器的外部接口信号主要包括与Microblaze处理器、NVMe Host控制器、以太网控制器、外部DDR存储器相连接的端口。其中AXI4_Lite接口用于配置数据缓存控制器的寄存器;M_AXIS_ENTRY接口用于向NVMe Host控制器发送NVMe命令;S_AXIS_DATA接口用于接收输入的数据流数据;M_AXIS_DATA接口用于输出的缓存数据;M_AXI_DDR用于读写DDR内缓存的数据;NVMe_Done信号用于指示命令执行成功;NVMe_Error信号用于指示命令执行错误。

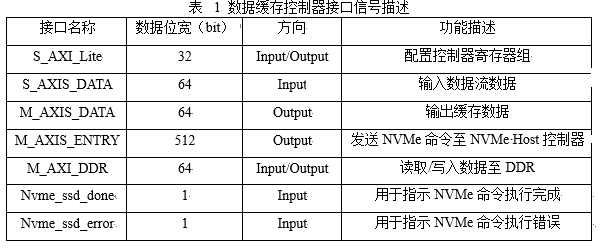

数据缓存控制器的顶层接口信号定义如表1所示。

对相关视频感兴趣者请看B站。搜用户名:专注与守望

审核编辑 黄宇

-

高速ssd存储系统中数据缓存控制器流程控制设计2025-04-14 978

-

基于SCSI协议处理器FAS466实现图像数据存储系统的设计2021-03-16 3662

-

常见的几种不同的高速数据采集存储系统介绍2019-07-04 3090

-

高速DDR SDRAM存储器控制器在嵌入式系统中的应用2019-07-02 5253

-

采用nvSRAM确保企业级SSD故障时电源可靠性2018-09-26 2708

-

基于FPGA并以Flash为存储介质的高速图像数据存储系统设计2017-11-18 4696

-

基于FPGA和SSD的嵌入式数据存储系统实现方法2017-11-05 1102

-

Tera-Store高速数据采集存储系统2017-10-24 1320

-

高速图像存储系统中SDRAM控制器的实现2016-08-29 757

-

基于PXIe的中频信号采集存储系统2016-08-16 2675

-

高速数据采集与存储系统技术方案2011-07-07 796

-

一种针对存储系统设计的应用级缓存回收策略2010-04-24 1904

-

高速大容量存储系统设计2010-03-08 1420

全部0条评论

快来发表一下你的评论吧 !