ADN2805 1.25Gbps时钟和数据恢复IC技术手册

描述

概述

ADN2805可提供下列接收器功能:量化以及时钟和数据恢复,适用于1.25 Gbps数据。它可自动锁定至所有数据速率,而无需外部参考时钟或编程。该器件满足所有的SONET抖动要求,包括抖动传递、抖动产生和抖动容差。

所有规格均相对于−40°C至+85°C环境温度而言,除非另有说明。ADN2805采用紧凑型5 mm × 5 mm、32引脚LFCSP封装。

数据表:*附件:ADN2805 1.25Gbps时钟和数据恢复IC技术手册.pdf

应用

- GbE 线路卡

特性

- 锁定1.25 Gbps NRZ串行数据输入

- 取得专利的时钟恢复架构

- 无需参考时钟

- 失锁指示器

- 通过I^2^C 接口访问可选特性

- 单电源供电:3.3 V

- 低功耗:390 mW(典型值)

- 5 mm × 5 mm 、32引脚LFCSP无铅封装

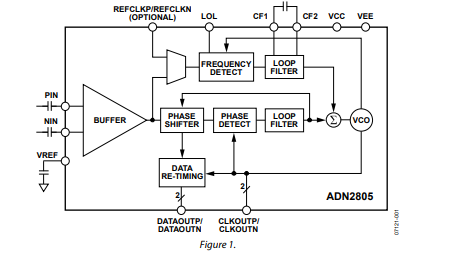

框图

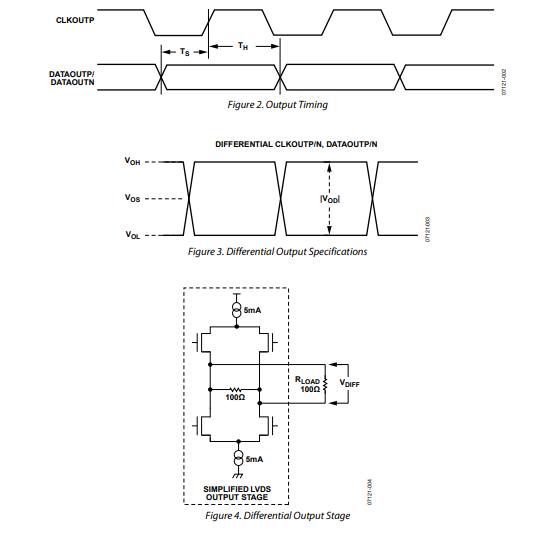

时序图

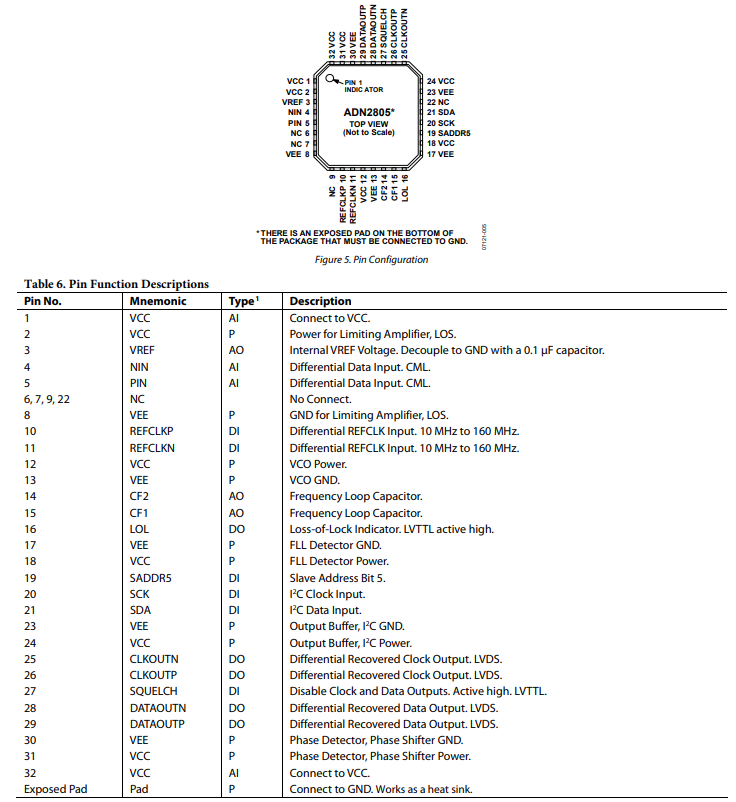

引脚配置描述

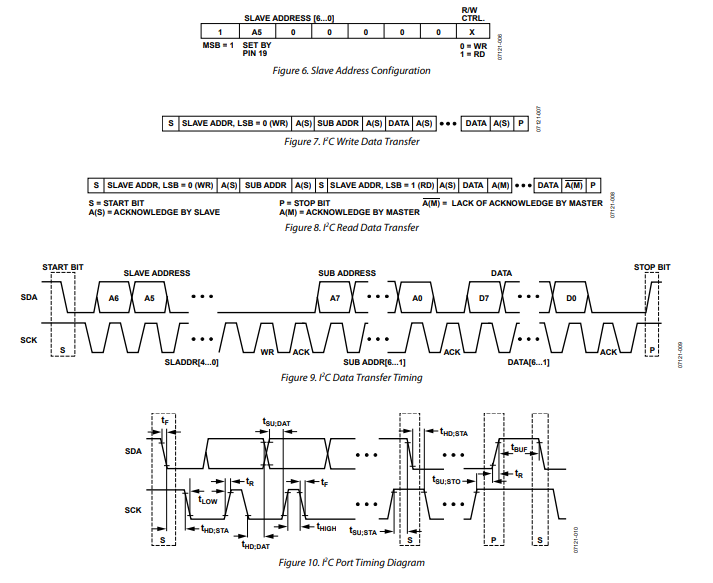

I2C接口时序和内部寄存器描述

工作原理

ADN2805 是一款用于时钟恢复和数据恢复的延迟锁相环电路,适用于从非归零(NRZ)编码数据中恢复时钟和数据。一个单独的反馈回路可对公共模式电压进行整形。高速延迟锁相环路径采用压控移相器,以跟踪输入抖动的高频率分量。VCO(压控振荡器)的独立相位控制可跟踪输入抖动的低频率分量。VCO 的初始频率由注入的第三个频率设定,该频率将 VCO 频率与输入数据频率进行比较,然后通过锁相环(PLL)的一阶调谐控制来控制 VCO。

延迟和锁相环路径共同跟踪输入数据信号。例如,当检测到时钟滞后于输入数据时,鉴相器会驱动 VCO 至更高频率,同时增加延迟移相器的相位;这两个动作都旨在减少时钟与数据之间的相位误差。较快的时钟会加快相位,而延迟的数据会减慢相位。由于环路滤波器是一个积分器,静态相位误差会被驱动至零。

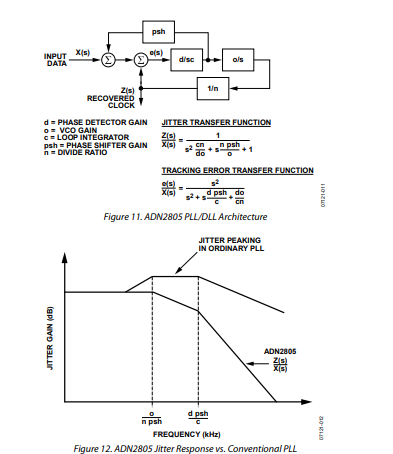

从另一个角度看,该电路中的移相器实现了二阶函数闭环操作所需的零频率响应。由于环路滤波器是一个积分器,因此在闭环传输函数中不存在零频率响应,这与传统的二阶锁相环传输函数不同。该电路在闭环传输函数中不存在零频率响应,因此不会出现抖动峰值。

延迟和锁相环路径共同提供宽带宽抖动调节和窄带滤波。图 11 中的线性化框图显示了抖动传输函数 (Z(s)/X(s)) ,在中等低频率下具有卓越的滤波性能。这表明抖动传输函数在低频段具有高增益,这意味着主 PLL 具有虚拟零抖动峰值(见图 12)。这使得该电路在信号再生应用中,对于需要抖动峰值以补偿由于光纤或同轴电缆传输导致的抖动累积的情况而言,是理想之选。

误差传输函数 (e(s)/X(s)) 具有与普通锁相环类似的高通形式。该传输函数经过优化,可实现宽带抖动调节,因为抖动传输函数 (Z(s)/X(s)) 提供了窄带抖动滤波。

抖动和相位环路共同为输入抖动对数据调制的整体影响提供了宽带滤波。在低频段,积分器与环路滤波器一起提供高增益,使 VCO 能够跟踪低频抖动。因此,VCO 调谐范围可提供较大的低频抖动调节余量。由于小相位误差对应的控制电压变化很小,移相器可保持接近其范围的中心位置,从而对低频抖动的贡献很小。

在中等频率下,VCO 的增益和调谐范围不足以跟踪抖动。此时,VCO 控制电压达到其调谐范围的任一极端并饱和,VCO 频率则根据其固有频率发生变化,这对抖动的影响很小。因此,延迟锁相环控制电压承担了跟踪输入抖动的任务。

移相器的增益在 UI(单位间隔)中可视为一个平坦的平台,其最小值为 2 个 UI,在所有数据速率下均如此。

-

1.25 Gbps时钟和数据恢复IC ADN2805:特性、原理与应用全解析2026-03-23 505

-

ADN2917连续速率8.5 Gbps至11.3 Gbps时钟和数据恢复IC,集成限幅放大器/均衡器技术手册2025-04-10 1678

-

ADN2913:连续速率6.5 Mbps至8.5 Gbps时钟和数据恢复IC,集成限幅放大器/均衡器数据表2021-05-25 1002

-

ADN2815:连续速率10 Mb/s至1.25 Gb/s时钟和数据恢复IC数据表2021-05-09 730

-

ADN2806:622 Mbps时钟和数据恢复IC数据表2021-05-08 1345

-

ADN2917:连续速率8.5 Gbps 至11.3 Gbps 时钟和数据恢复IC,集成限幅放大器/均衡器2021-03-22 903

-

ADN2805 1.25 Gbps时钟和数据恢复IC2019-02-15 409

-

ADN2805,pdf datasheet (1.25 Gb2009-09-23 1624

全部0条评论

快来发表一下你的评论吧 !