AD9549双输入网络时钟发生器/同步器技术手册

描述

概述

AD9549为包括同步光纤网络 (SONET/SDH)在内的许多系统提供同步。AD9549可以产生与两个外部输入基准之一同步的输出时钟。外部基准可能包含非常恶劣的时间抖动,或者相位噪声。在基准丢失期间、甚至两个基准都丢失的情况下,AD9549能够利用数控环路和保持(holdover)电路连续产生有效的干净的(低抖动)输出时钟。

AD9549工作温度在工业温度范围,为-40°C ~ +85°C。

数据表:*附件:AD9549双输入网络时钟发生器 同步器技术手册.pdf

应用

- 网络同步

- 基准时钟抖动清除

- SONET/SDH时钟,直到OC-192,包括前向纠错(FEC)

- Stratum 3/3E基准时钟

- 无线基站,控制器

- 有线线缆基础设施

- 数据通信

特性

- 灵活的基准输入

- 输入频率8 kHz到750 MHz

- 两个基本输入

- 基准丢失指示器

- 自动与手动保持(Holdover)/转换模式

- 自动与手动保持(Switchover)/转换模式

- 平滑的A ~ B输出相变

- 保持(holdover)模式具有卓越的稳定性

- 可编程的16+1位输入分配器

- 差分HSTL时钟输出

- 输出频率高达750 MHz

- 单端CMOS输出;频率<50MHz

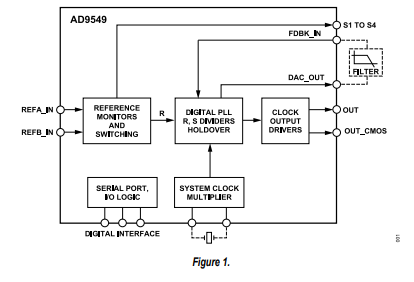

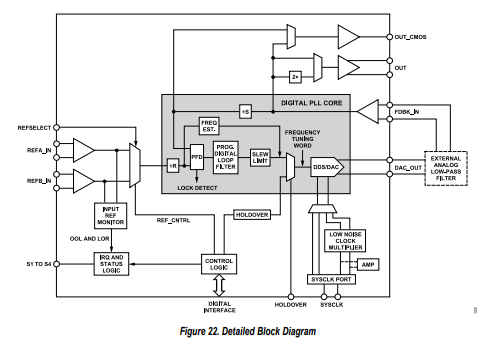

框图

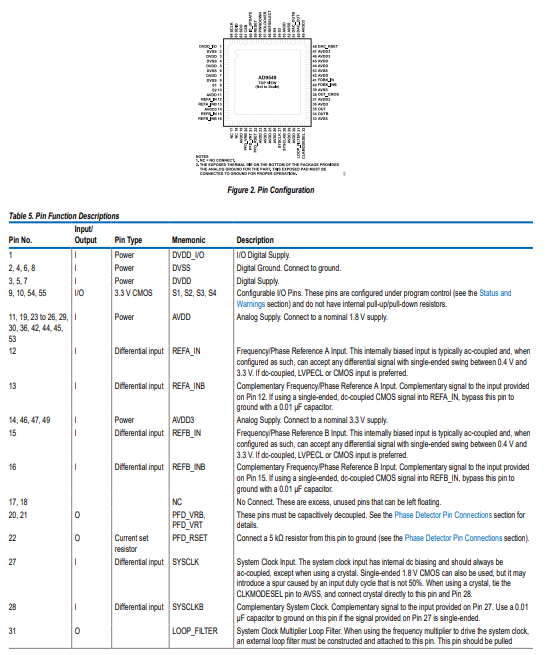

引脚配置描述

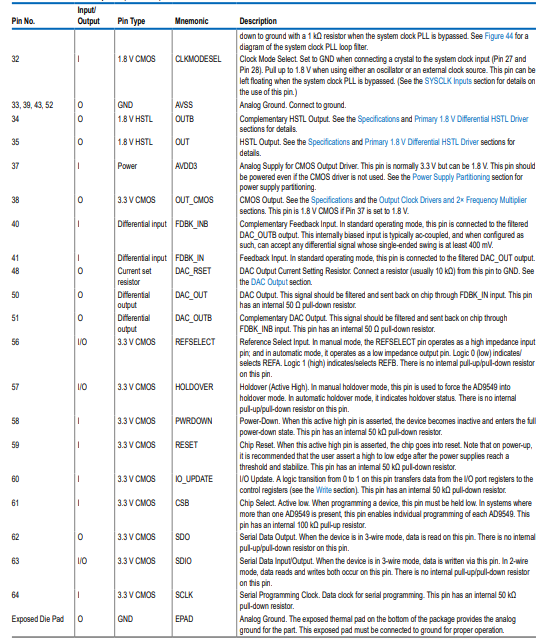

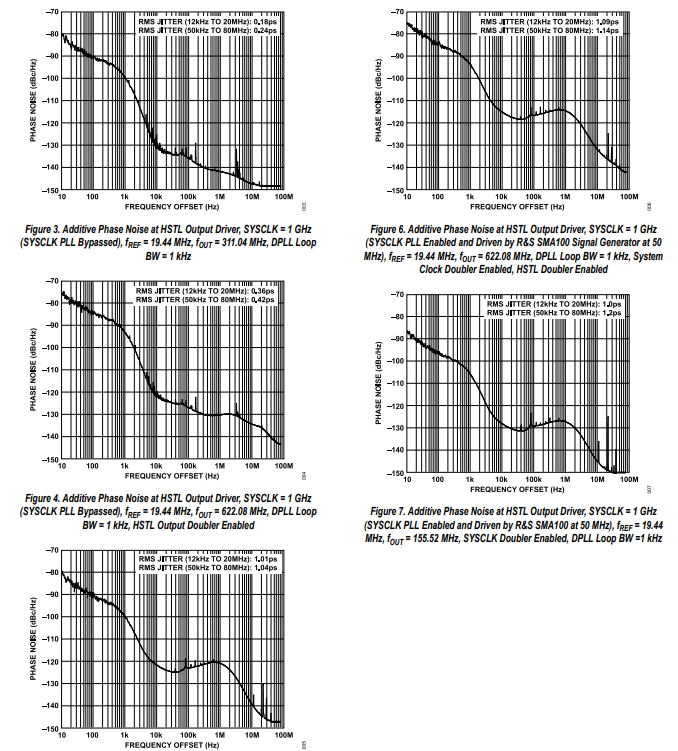

典型性能特征

操作理论

AD9549 提供的时钟输出,其相位和频率与所选的(激活的)参考信号(REFA 或 REFB)直接相关,但其相位噪声频谱主要由系统时钟决定。参考频率由支持的时钟提供。现有参考信号中的抖动通过可编程数字滤波器(数字锁相环,PLL)大幅降低,这是本产品的核心技术。AD9549 支持手动和自动校准。在锁定期间,AD9549 持续运行以提供输出,只要系统时钟保持正常工作。输出频率是系统时钟在自动校准之前的稳态输出频率的平均值。

此外,AD9549 还提供手动和自动切换模式,用于在两个参考信号之间进行切换,以防其中一个信号出现故障或丢失。通过使用数字控制振荡器(DCO)实现数字合成器(DDS),并集成数模转换器(DAC),由系统时钟对其进行时钟控制。旁路 PLL 反馈频率乘法器可使系统时钟直接用作低频源,以实现更好的抖动性能。应直接为数字频率合成器提供采样理论集上限,该上限为输出频率的 50%(其中 fs 是 DAC 速率),但实际限制为 40%,以便能够选择性地启用片外重构滤波器。AD9549 的输出信号会反馈到数字 PLL 中,完成 PLL 闭环,并包括直通输出电路。输出电路包含 HSTL 和 CMOS 输出缓冲器,以及用于 DDS 必须生成高于奈奎斯特电平频率的混频器设计。

各个功能模块将在以下部分进行介绍。

数字锁相环内核(DPLLC)

数字锁相环内核(DPLLC)包含频率估计模块和驱动 DDS 的信号链锁定控制模块。

DPLLC 的起始信号是参考信号 (f_R) ,它出现在 REFA 或 REFB 输入引脚上。该信号的频率可通过前向分频器按整数因子 (R) 进行分频。前向分频器的输出是馈送到鉴频鉴相器(PFD)的相位/频率检测信号。因此,PFD 的输入频率由下式给出:

PFD 输出一系列数字字,这些数字字被路由到数字环路滤波器。数字滤波器的实现方式具有诸多优势:滤波器响应由数值系数而非离散元件值确定;不存在元件老化、漂移或随时间变化的问题;不存在热噪声(在环路滤波器中),并且不存在控制节点泄漏电流(这会导致传统模拟 PLL 中出现参考杂散)。

环路滤波器的输出是一系列数字字。这些数字字被应用于 DDS 的频率调谐输入,以调节 DCO 频率。DDS 通过集成 DAC 有效地模拟了压控振荡器(VCO)的操作,从而产生模拟输出信号。

-

AD9549:高性能网络时钟发生器/同步器的深度解析2026-04-14 69

-

LMK5B33414EVM网络时钟发生器评估模块技术解析2025-09-08 1064

-

AD9547双路/四路输入网络时钟发生器/同步器技术手册2025-04-11 1062

-

毫微微时钟网络同步器、抖动衰减器和时钟发生器RC32112A 数据表2024-01-31 483

-

时钟发生器AD9516-0技术手册2022-01-25 1000

-

AD9575:网络时钟发生器,双输出数据表2021-05-09 845

-

AD9542:四输入、五输出、双DPLL同步器和自适应时钟转换器产品手册2021-05-08 866

-

AD9549:双输入网络Clock生成器/同步数据Sheet2021-04-30 984

-

AD9548:四/八路输入网络时钟发生器/同步器数据表2021-04-16 920

-

如何选择合适的时钟发生器2020-11-22 3915

-

用于评估AD9549A 8kHz至750MHz输入时钟发生器的评估板AD9549A/PCBZ2019-02-26 1929

-

AD9549 双输入网络时钟发生器/同步器2019-02-15 549

-

Microchip基于MEMS的时钟发生器2018-06-07 6004

-

双输入网络时钟发生器/同步器ad9549数据表2017-10-19 857

全部0条评论

快来发表一下你的评论吧 !