高速SSD存储+传输系统方案设计

描述

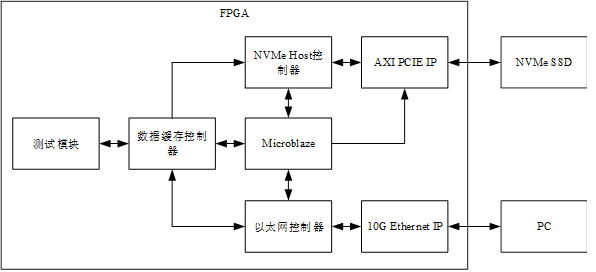

如图1所示,系统整体架构由NVMe存储,Microblaze控制及以太网高速传输构成。该系统能够持续接收高速数据流数据,并经缓存模块处理后,存储至NVMe SSD,同时可以将存储数据通过万兆光纤以UDP协议上传至上位机以供后续处理。

该系统主要包含数据缓存控制器、NVMe Host控制器、以太网控制器、Microblaze处理器、测试模块、10 Gigabit Ethernet Subsystem(以下简称10G Ethernet IP)、AXI Bridge for PCI Express Gen3(以下简称AXI PCIe IP)等模块。系统中NVMe Host控制器实现了对NVMe命令执行流程的加速,以太网控制器实现了对UDP、ARP和ICMP数据包的处理工作,数据缓存控制器实现了对大量突发数据的缓存工作以及对输入的数据流数据进行自动存储管理。下面将对系统的整体工作流程和各模块的功能设计分别进行阐述。

图1 高速存储传输系统整体架构

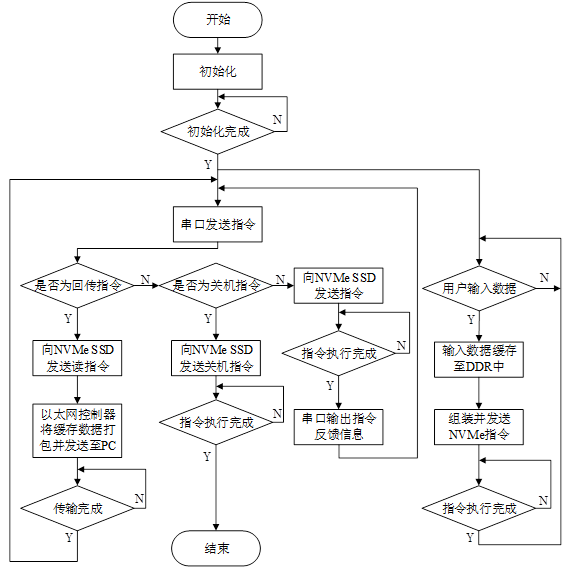

本设计通过将数据存储和数据回传划分为两个传输通道同步进行工作,保证在系统进行数据存储工作时,可以执行其他命令。高速存储传输系统的整体工作流程图如图2所示。

图2 系统整体工作流程图

对NVMe IP视频感兴趣的,请看B站视频。搜用户名: 专注与守望

高速存储传输系统工作流程描述如下:

(1)系统上电后,对各个模块进行初始化,包括对数据缓存控制器、NVMe Host控制器和以太网控制器参数的配置以及监测NVMe SSD的连接状态等工作;

(2)为了提高系统的灵活性,把数据存储和数据回传划分为两个通道,每个通道可以独立工作。因此,等待初始化完成后,有两个进程可以同时进行,一方面用户可以通过串口向系统发送读取、关机、识别等命令,分别进入流程(3)、(4)、(5)执行相应流程。另一方面若同时有数据输入时,流程(6)会以并行的方式同时进行;

(3)若用户发送读取命令,则根据用户信息组装相应的NVMe读命令并发送至NVMe SSD,等待命令执行完成后,将读取到的数据通过以太网控制器发送至上位机;

(4)若用户发送关机命令,则进入关机流程,向NVMe SSD按照关机步骤发送相应的命令,命令执行完成,流程结束;

(5)若为识别、SMART等命令,则向NVMe SSD发送相应的命令,等待NVMe SSD反馈命令信息后,通过串口输出;

(6)若有数据输入系统,先将数据流数据缓存至DDR,并根据输入的数据量大小组装相应的NVMe写命令发送至NVMe SSD,重复此过程,直至无数据输入。

审核编辑 黄宇

-

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构2026-01-29 398

-

采用nvSRAM确保企业级SSD故障时电源可靠性2018-09-26 2708

-

最佳SSD电源选择方案2018-11-28 4439

-

如何用MRAM和NVMe SSD构建未来的云存储的解决方案2021-01-11 1867

-

SOR160系列高速光纤海量存储记录系统2021-11-17 1425

-

基于 NVMe 接口的带 exFAT 文件系统的高速存储 FPGA IP 核演示2022-06-03 16338

-

氨纶工程DCS 系统方案设计2009-04-07 637

-

高速数据采集与存储系统技术方案2011-07-07 796

-

实现ARINC 429数字信息传输的方案设计2017-01-14 1219

-

PIS车地无线双向数据传输方案设计2016-12-27 1074

-

一种高可靠星载大容量存储器的坏块表存储方案设计2017-01-03 610

-

某转台伺服系统方案设计2017-02-08 1148

-

高速数据采集及其存储方案设计_王宜结2017-03-19 854

-

基于FPGA器件实现大容量高速存储系统的方案设计2020-07-30 3255

-

Samtec Flyover QSFP系统:高速信号传输新方案2025-12-18 556

全部0条评论

快来发表一下你的评论吧 !