ADCLK905超快型SiGe ECL时钟/数据缓冲器技术手册

描述

概述

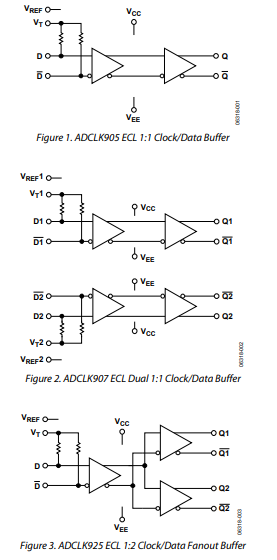

ADCLK905(单输入/单输出)、ADCLK907(双通道单输入/单输出)和ADCLK925(单输入/双输出)为超高速时钟/数据缓冲器,采用ADI公司专有的XFCB3硅锗(SiGe)双极性工艺制造。

数据表:*附件:ADCLK905超快型SiGe ECL时钟 数据缓冲器技术手册.pdf

ADCLK905/ADCLK907/ADCLK925内置全摆幅射极耦合逻辑(ECL)输出驱动器。对于PECL(正ECL)工作模式,将VCC偏置到正电源,VEE 偏置至接地。对于NECL(负ECL)工作,将VCC偏置至接地,VEE 偏置到负电源。

缓冲器提供95 ps传播延迟就、7.5 GHz反转速率、10 Gbps数据速率和60 fs随机抖动(RJ)。

输入含有100 Ω的中心抽头片内端接电阻。提供VREF引脚用于偏置交流耦合输入。

ECL输出级旨在从各端将800 mW直接驱动至端接于VCC − 2 V的50 Ω负载,从而获得1.6 V的总差分输出摆幅。

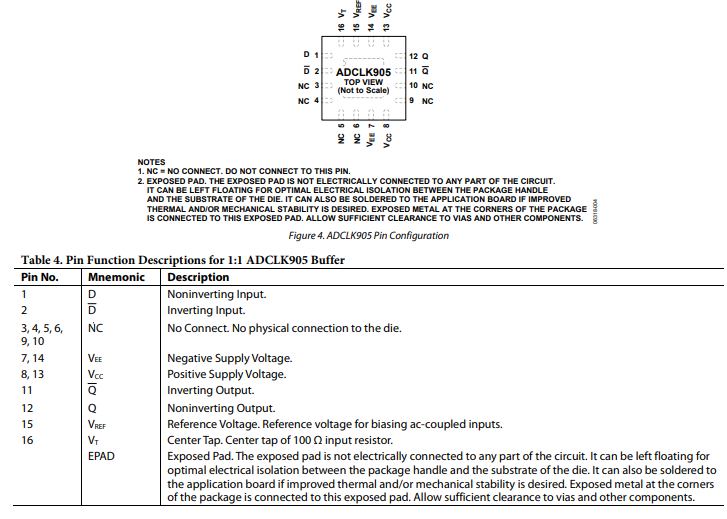

ADCLK905/ADCLK907/ADCLK925提供16引脚LFCSP封装。

应用

- 时钟和数据信号恢复和电平转换

- 自动测试设备(ATE)

- 高速仪器仪表

- 高速线路接收机

- 阈值检测

- 转换器时钟

特性

- 传播延迟:95 ps

- 反转率:7.5 GHz

- 典型输出上升/下降:60 ps

- 随机抖动(RJ):60 fs

- 两个输入引脚上均有片内端电极

- 扩展工业温度范围:−40°C至+125°C

- 电源:2.5 V至3.3 V(V

CC– VEE)

典型应用电路

引脚配置描述

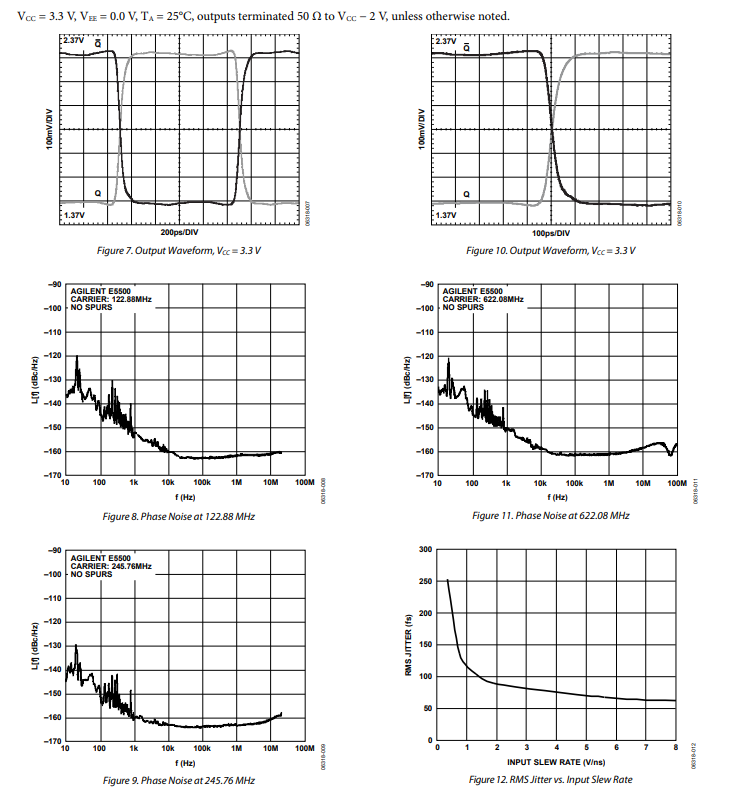

典型性能特征

应用信息

电源/接地布局与旁路

ADCLK905/ADCLK907/ADCLK925 缓冲器专为高速应用设计。因此,必须采用高速设计技术才能达到规定的性能指标。使用低阻抗电源层对于正负电源(VEE 和正电源 VCC )来说都至关重要,这是多层板设计的一部分。提供最低阻抗的回流路径可确保目标应用中最佳的抖动性能。

对输入和输出电源进行充分旁路也很重要。应在每个电源引脚几英寸范围内放置一个 1 μF 的电解旁路电容到地。此外,应尽可能靠近每个 VEE 和 VCC 电源引脚放置多个 0.001 μF 的高品质旁路电容,并通过冗余过孔连接到接地层。高频旁路电容应经过精心挑选,以实现最低的电感和等效串联电阻(ESR)。旁路的寄生电感应严格控制在最低水平,以最大限度地提高高频旁路的有效性。

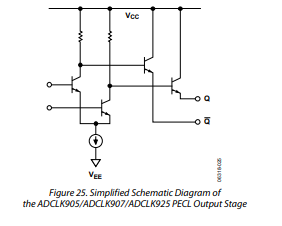

输出级

只有采用合适的传输线端接,才能实现规定的性能。ADCLK905/ADCLK907/ADCLK925 缓冲器的输出设计为可直接驱动 800 mV 电压进入 50 Ω 电缆或微带/带状线传输线,端接电阻为 50 Ω,参考电压为 VCC - 2 V。图 25 所示的 PECL 输出级在参考文献 25 中有详细说明。为实现最佳传输线匹配,若采用更高速度的信号,则走线长度应小于一个波长。此外,可能需要采用微带或带状线技术,以确保合适的过渡时间,并防止输出振铃以及与脉冲宽度相关的传播延迟偏差。

优化高速性能

与任何高速电路一样,恰当的设计和布局技术对于实现规定的性能至关重要。杂散电容、电感、电感电源和接地阻抗或其他布局问题会严重限制性能并导致振荡。不连续的信号和输出传输线也会严重限制规定的抖动性能,降低输入数据速率。

在 50 Ω 环境中,输入和输出缓冲对性能有显著影响。该缓冲器为 D 和 D 输入提供内部 50 Ω 端接电阻。返回端通常应连接到参考引脚(如有提供)。必须谨慎设置端接电位,使用陶瓷电容防止输入信号因端接回路中的寄生电感而产生不必要的畸变。如果输入直接耦合到信号源,必须注意确保引脚在额定输入差分和共模范围内。

如果回路浮空,器件会呈现 100 Ω 交叉端接,但信号源必须控制共模电压并提供输入偏置电流。

在输入引脚之间有静电放电(ESD)钳位二极管,以防止对输入转换器造成过度应力。当需要钳位时,建议使用合适的外部二极管。

缓冲器随机抖动

ADCLK905/ADCLK907/ADCLK925 经过专门设计,可在较宽的输入转换速率范围内最大限度地降低随机抖动。只要有足够的电压摆幅,随机抖动受输入信号转换速率的影响最大。只要有可能,过大的输入信号都应使用快速肖特基二极管进行钳位,因为限幅器会降低转换速率。输入信号走线长度应小于一个波长,并且应采用低损耗电介质或具有良好高频特性的电缆。

-

高速电路的理想之选:ADCLK905/ADCLK907/ADCLK925 ECL时钟/数据缓冲器2026-03-22 578

-

ADCLK907超快型SiGe ECL时钟/数据缓冲器技术手册2025-04-14 1382

-

ADCLK950 2路可选输入、10路LVPECL输出、SiGe时钟扇出缓冲器技术手册2025-04-11 1231

-

ADCLK944是一款超快型时钟扇出缓冲器2023-01-04 2039

-

EVADC905 ADCLK905评估板2021-06-08 718

-

ADCLK914:超高速、SiGe、开放采集器HVDS时钟/数据缓冲器数据表2021-05-26 1109

-

ADCLK946:六路LVPECL输出,SiGe时钟扇出缓冲器数据表2021-04-19 1410

-

ADCLK925 超快型SiGe ECL时钟/数据缓冲器2019-02-22 983

-

超快SiGe ECL时钟数据缓冲器adclk905/adclk907/adclk925数据表2017-10-20 1294

-

ADCLK905/ADCLK907/ADCLK925,pdf2009-09-15 699

全部0条评论

快来发表一下你的评论吧 !