DS1124 5.0V、8位可编程延时电路技术手册

描述

概述

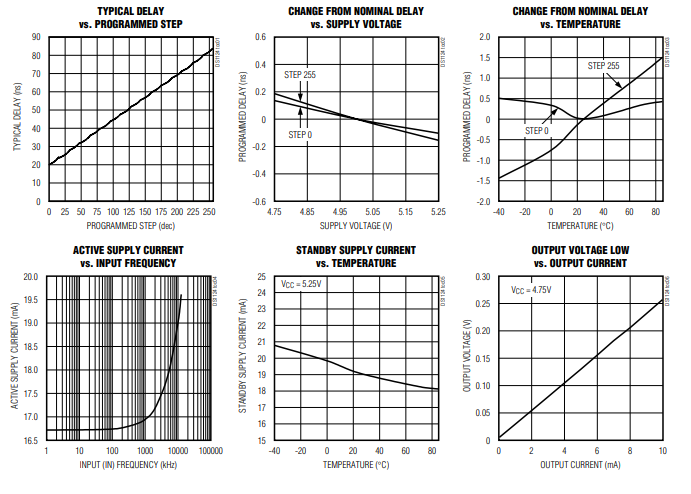

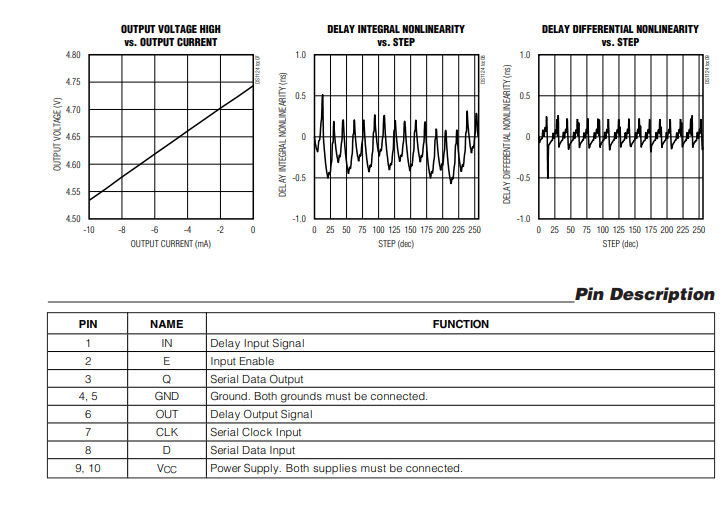

DS1124是一款功能与DS1021-25类似的8位可编程定时元件。可以通过3线串行接口编程256级延时间隔。DS1124具有0.25ns的步进,可以提供20ns至高达84ns延时,积分非线性为±3ns。

数据表:*附件:DS1124 5.0V、8位可编程延时电路技术手册.pdf

应用

- 数字测试设备

- 数字投影仪

- LCD电视

- 信号发生器与分析仪

- 电信

特性

- 0.25ns步进

- 精确的前沿和后沿

- CMOS/TTL兼容

- 可将信号延迟一个或多个周期

- 3线串行可编程接口

- 5.0V单电源

- 10引脚µSOP封装

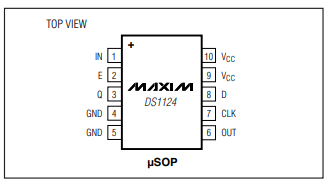

引脚配置

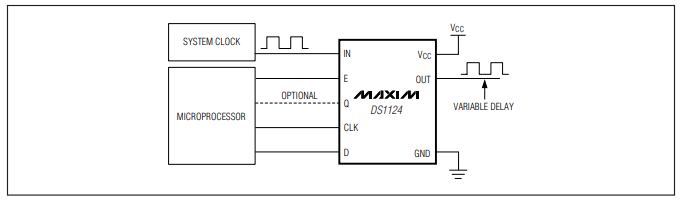

典型操作电路

典型操作特性

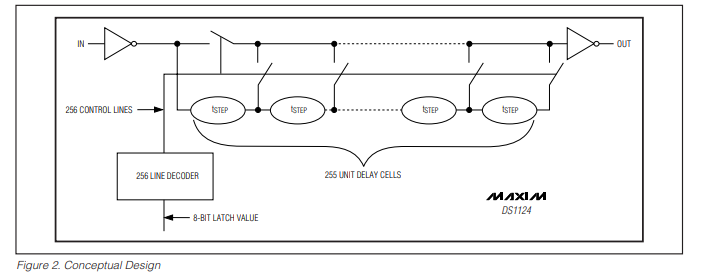

DS1124是一种8位可编程延迟线,可以在256个不同的延迟间隔之间进行调整。DS1124架构(见图2)允许某些信号延迟一个以上的周期,这使得信号的相位可以调整至360°。编程由三线式串行接口执行。利用三线式接口,可以将多个器件封装在一起,用于需要多个可编程延迟的系统,而无需使用额外的I/O资源。

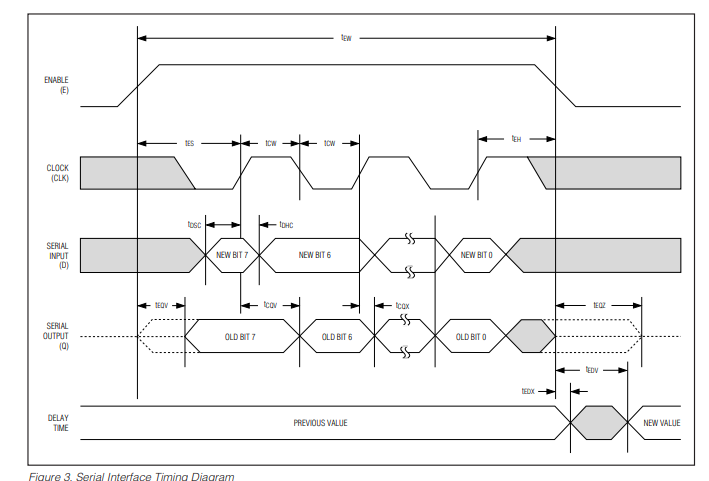

串行模式的操作类似于移位寄存器。当引脚设置为高逻辑电平时,它使能移位寄存器,CLK从最高有效位开始一次一位地将数据D读入寄存器。所有8位移入DS1124后,必须拉低E以结束数据传输并激活新值。在E被拉低之后,信号延迟达到其额定精度之前,需要一个建立时间(tEDv)。串行接口的时序图如图3所示。三线式接口还有一个输出(Q ),可用于级联多个三线式器件,并可用于读取总线上器件的电流值。要读取三线式器件存储的电流值,必须使能锁存器,读取q值,然后在寄存器计时之前写回D。这使得寄存器的当前值在被读取时被写回DS1124。这可以通过几种不同的方式来实现。如果微处理器的一个I/O引脚在设置为输入时为高阻抗,则可以使用一个反馈电阻(RFB,一般在1kω到10kQ之间)将Q上的数据写回D,见图4A。如果微处理器的I/O引脚上有一个内部上拉电阻,或者只提供独立的输入和输出引脚,寄存器中的值仍然可以读取。图4B所示电路允许微处理器读取Q值,微处理器必须先将Q值写入D,然后才能为总线提供时钟以读取下一位。如果读取Q值时没有将它们写入toD(通过上拉或其他方式),读取将是破坏性的。破坏性的读取周期可能会导致延迟设置发生不希望的变化。

-

深入解析DS1023:8位可编程定时元件的卓越性能与应用2026-03-23 233

-

LM136-5.0系列 5.0V 基准二极管技术手册2025-08-18 1794

-

可编程晶体振荡器SG-8002CA,CMOS和TTL兼容2025-01-07 1380

-

可编程直流电源程序编程手册(SCPI版)V022021-09-15 1673

-

LTC1859 - 16 位、8 通道 ADC 具有可编程输入范围和高达 ±25V 的故障保护2021-03-20 787

-

TEC9952可编程四位定时控制器技术手册2011-07-19 1177

-

可编程SoC(SoPC),什么是可编程SoC(SoPC)2010-03-26 2769

-

采用136 5.0V构成的5V低噪声缓冲电压基准电路2009-10-24 942

-

用8数据位设定1~125倍增益的可编程放大器电路图2009-07-16 825

-

5.0V方波标定器电路图2009-04-03 1243

-

DS1825 带有4位ID、分辨率可编程设置的1-Wire数2008-12-08 1616

-

DS1124中文资料pdf2008-04-15 1884

全部0条评论

快来发表一下你的评论吧 !