ADN2816连续速率10 Mb/s至675 Mb/s时钟和数据恢复IC技术手册

描述

概述

ADN2816可提供下列接收器功能:量化以及时钟和数据恢复,适用于从10 Mb/s到675 Mb/s的连续数据速率。它可自动锁定至所有数据速率,而无需外部参考时钟或编程。该器件满足所有的SONET抖动要求,包括抖动传递、抖动产生和抖动容差。所有规格均相对于−40°C至+85°C环境温度而言,除非另有说明。

ADN2816采用紧凑型5 mm × 5 mm、32引脚芯片级封装。

数据表:*附件:ADN2816连续速率10 Mb s至675 Mb s时钟和数据恢复IC技术手册.pdf

应用

- SONET OC-1/3/12 和所有相关FEC速率

- 光纤通道、ESCON、快速以太网、SDI等

- WDM应答器

- 再生器/中继器

- 测试设备

- 宽带交叉连接和路由器

特性

- 串行数据输入:10 Mb/s至675 Mb/s

- 超过SONET抖动传递/产生/容差要求

- 取得专利的时钟恢复架构

- 无需参考时钟

- 失锁指示器

- 通过I^2^C™ 接口访问可选特性

- 单电源供电:3.3 V

- 低功耗:366 mW(典型值)

- 5 mm × 5 mm、32引脚LFCSP无铅封装

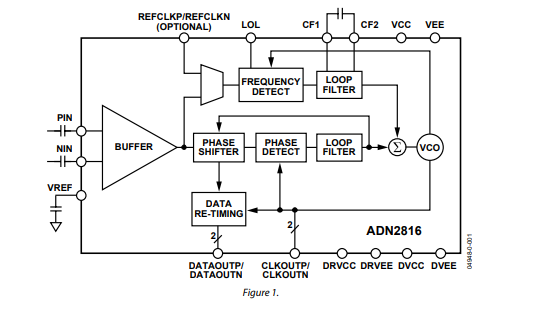

框图

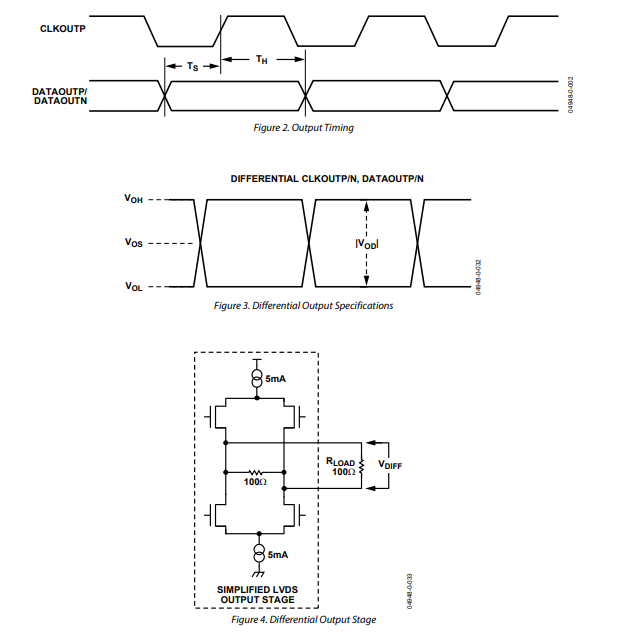

时序图

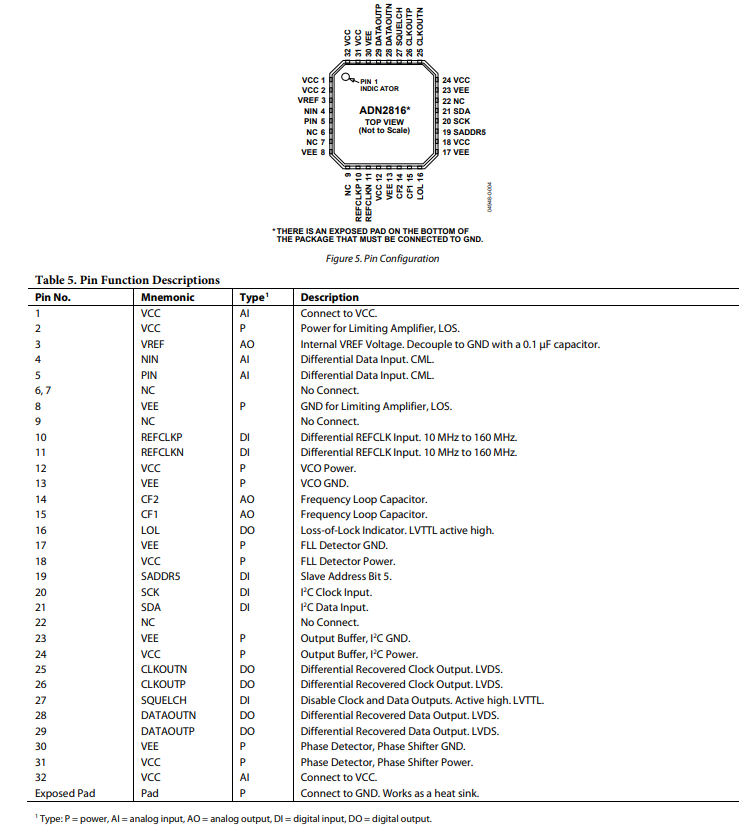

引脚配置描述

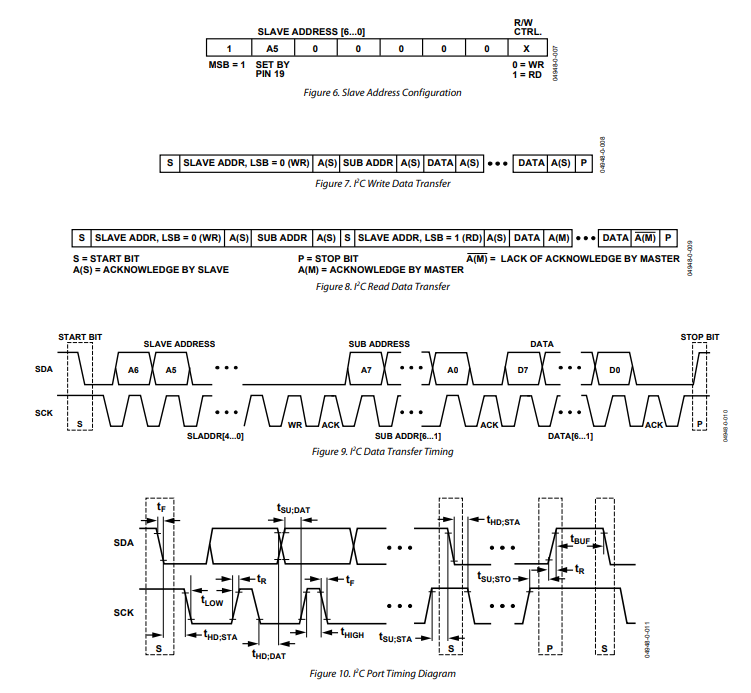

I2C接口时序和内部寄存器描述

抖动规格

ADN2816时钟数据恢复(CDR)器件旨在实现最佳误码率(BER)性能,并超越Telcordia Technologies公司GR - 253 - CORE文件(2000年9月第3版)中针对SONET/SDH设备提出的抖动传输、产生和容限规格。

抖动是指数字信号边沿相对于其长期平均位置的动态偏移,以单位间隔(UI)为测量单位,其中1 UI等于1比特周期。输入数据上的抖动会在恢复时钟的采样沿上导致动态相位误差。恢复时钟上的抖动会在重新定时的数据上产生抖动。

以下部分简要概述了抖动产生、传输和容限的规格,这些规格与Telcordia文件(GR - 253 - CORE,2000年9月第3版)中针对设备级光接口以及ADN2816在这些规格方面的性能所规定的内容一致。

抖动产生

抖动产生规格限制了在无抖动和无漂移输入信号情况下,器件所能产生的抖动量。对于SONET设备,产生的抖动必须小于0.01 UI均方根值,且必须小于0.1 UI峰峰值。

抖动传输

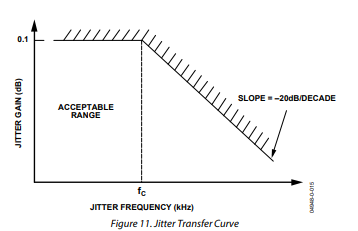

抖动传输函数是输出信号上的抖动与施加在输入信号上的抖动之比,它是频率的函数。该参数衡量了输入信号上能够传输到输出信号上的抖动量(见图11)。

抖动容限

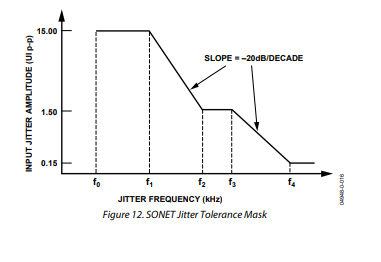

抖动容限定义为施加在输入信号上的正弦抖动的峰峰值幅度,该幅度会导致1 dB的功率损失。这是一项应力测试,旨在确保在工作条件下不会产生额外的损耗(见图12)。

-

ADN2807:155/622 Mb/s时钟和数据恢复IC的技术剖析与应用指南2026-03-23 353

-

ADN2812连续速率12.3 Mb/s至2.7 Gb/s时钟和数据恢复IC,集成限幅放大器技术手册2025-04-15 2107

-

ADN2816:连续速率10 Mb/s至675 Mb/s时钟和数据恢复IC数据表2021-05-25 2145

-

ADN2865:连续速率12.3Mb/s至2.7 Gb/s时钟和数据恢复IC,带环路定时SERDES初步数据表2021-05-09 1029

-

ADN2812:连续速率12.3 Mb/s至2.7 Gb/s时钟和数据恢复IC,带集成限幅放大器数据表2021-05-08 1180

-

ADN2816 连续速率10 Mb/s至675 Mb/s时钟和数据恢复IC2019-02-22 1885

-

ADN2816,pdf datasheet (Data Re2009-09-15 1019

全部0条评论

快来发表一下你的评论吧 !