AD9513 800MHz时钟分配IC,分频器,延迟调整,三路输出技术手册

描述

概述

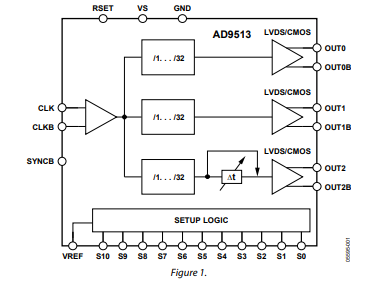

AD9513是一款三路输出时钟分配IC,其低抖动和低相位噪声特性能够实现优质的数据转换器性能。这款器件也适合于对相位噪声和抖动有严格要求的其它应用。

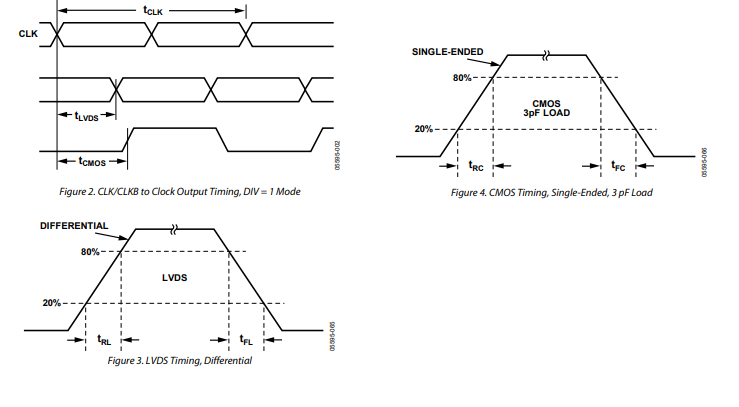

三路独立的时钟输出可被设置为LVDS或CMOS电平。在LVDS模式下,输出工作在800 MHz;在CMOS模式下,输出工作在250 MHz。

每路输出都具有可编程的分频器,可设置1~32的整数分频比。一路时钟输出相对于其它时钟输出的相位可通过分频器相位选择功能进行设置,用作时序粗调。

其中一路输出提供延迟单元,具有3个可选择的满量程延迟值(1.5 ns、5 ns及10 ns),均可提供16级精调。

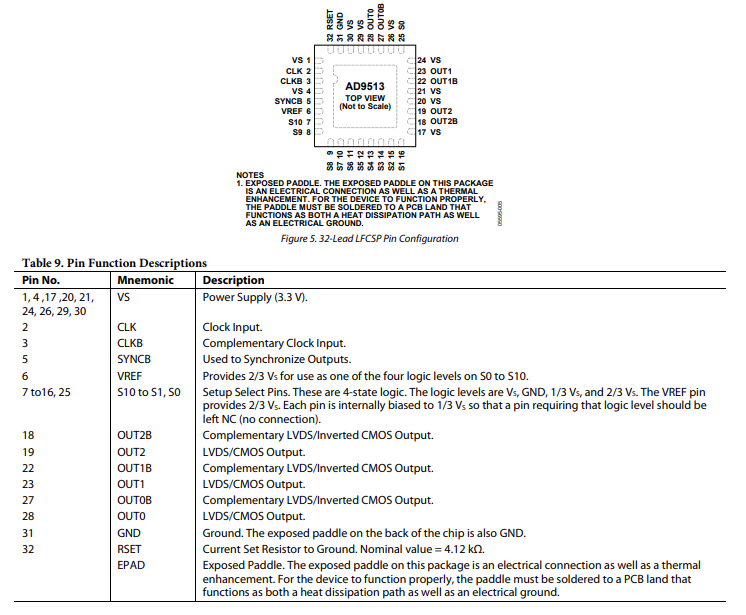

AD9513无需外部控制器即可进行操作或设置。器件通过11个引脚(S0~S10)和4个逻辑电平进行编程。编程引脚被内部偏置为⅓ VS。VREF引脚提供⅔ VS电平。VS (3.3 V)和GND(0 V)提供另外两个逻辑电平。

AD9513 非常适合于数据转换器时钟应用,利用亚皮秒抖动编码信号,可实现优质的转换器性能。

AD9513采用32引脚LFCSP封装,3.3 V单电源供电,工作温度范围为−40°C~+85°C。

数据表:*附件:AD9513 800MHz时钟分配IC,分频器,延迟调整,三路输出技术手册.pdf

应用

- 低抖动,低相位噪声时钟分配

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 高性能仪器仪表

- 宽带基础设施

- 自动测试设备(ATE)

特性

- .6 GHz差分时钟输入

- 3个可编程分频器

- 编程范围:1至32

- 用于延迟粗调的相位选择

- 节省空间的32引脚LFCSP封装

- 三路800 MHz/250 MHz LVDS/CMOS时钟输出

- 加性输出抖动:300 fs rms

- 延迟时间最长11.6 ns

- 可利用4电平逻辑引脚进行器件配置

框图

时序图

引脚配置描述

功能描述

总体

AD9513 可将其输入时钟分配至多达三个输出端。每个输出端可设置为低压差分信号(LVDS)或互补金属氧化物半导体(CMOS)逻辑电平。每个输出端都有各自的分频器,可从整数 1(旁路)至 32 的列表中选择分频比。

输出端 2(OUT2)包含一个模拟延迟模块,可设置为增加 2.5 纳秒、6.0 纳秒或 11.6 纳秒的额外延迟,每种延迟都有 16 级精细调整。

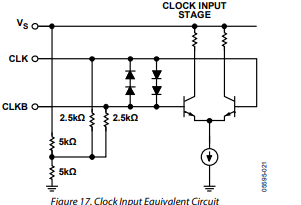

差分时钟输入(CLK, CLKB)

CLK 和 CLKB 引脚是差分时钟输入引脚。此输入适用于高达 1600 MHz 的频率。抖动性能会以低于 1 V/ns 的速率下降。输入电平应在 2.2 V 至 3.1 V 峰峰值(p - p)之间。任何更大的值都会导致输入引脚上的保护二极管导通。

参见图 17 了解 CLK 等效输入电路。此输入为全差分且直流耦合。信号输入必须交流耦合。如果使用单端输入,可通过在差分输入的一侧连接一个电容器来实现交流耦合,另一侧则通过一个电容器旁路至安静的交流地。

同步

上电同步

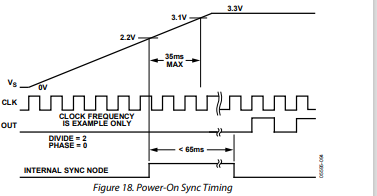

上电时会发出上电同步信号(POS),以确保输出端同步启动。上电同步仅在 Vₛ 电源转换期间起作用,以确保输出端同步启动。Vₛ 电源转换的区域范围为 2.2 V 至 3.1 V,最长可能在 Vₛ 超过 2.2 V 后 65 毫秒内发生。只有分频比不为 1 的输出端会进行同步。

SYNCB

如果在 AD9513 运行期间更改设置配置,输出端可能会失去同步。但随时都可通过 SYNCB 引脚使输出端重新同步。

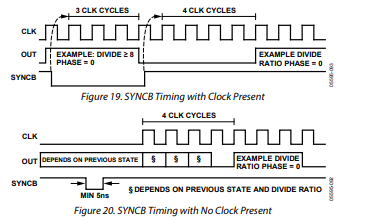

当 SYNCB 引脚被拉低并释放时,会进行同步。时钟输出端(分频比为 1 的情况除外)会被强制进入固定状态(由分频和相位设置决定)并保持在该静态条件下,直到 SYNCB 引脚恢复为高电平。释放 SYNCB 引脚后,在时钟信号(CLK)的四个周期后,所有输出端将恢复同步(分频比为 1 的情况除外)。

对于分频比为 1 的输出端,该输出端不受 SYNCB 影响。

-

深入解析 AD9513:高性能时钟分配芯片的卓越之选2026-03-22 643

-

AD9515 1.6GHz时钟分配IC,分频器,延迟调整,两路输出技术手册2025-04-15 1118

-

AD9515 1.6 GHz时钟分配IC,分频器,延迟调整,双输出数据表2021-06-16 841

-

AD9515:1.6 GHz时钟分配IC、分频器、延迟调整、双输出数据表2021-04-13 829

-

AD9512:1.2 GHz时钟分配IC,1.6 GHz输入,分频器,延迟调整,五输出数据表2021-03-22 912

-

AD9510:1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出2021-03-21 979

-

AD9513: 800 MHz Clock Distribution IC, Dividers, Delay Adjust, Three Outputs Data Sheet2021-01-28 783

-

基于AD9513时钟分配IC的评估板AD9513/PCBZ2019-02-22 2244

-

AD9513和AD9517输出频谱的相关问题?2018-10-24 3591

-

800兆赫时钟分配IC分频器延迟调整三输出ad9513数据表2017-10-19 1226

-

Hi-Fi三路有源分频器2009-11-27 2033

全部0条评论

快来发表一下你的评论吧 !