AD9512 1.2 GHz时钟分配IC、2路1.6 GHz输入、分频器、延迟调整、5路输出技术手册

描述

概述

AD9512提供多路输出时钟分配功能,输入信号最高可达1.6 GHz。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。

数据表:*附件:AD9512 1.2 GHz时钟分配IC、2路1.6 GHz输入、分频器、延迟调整、5路输出技术手册.pdf

3路独立的LVPECL时钟输出和2路LVDS时钟输出工作频率分别为1.2 GHz和800 MHz。可选的CMOS时钟输出工作频率为250 MHz。每路输出都有一个可编程分频器,可以旁路该分频器或者设置最高32的整数分频比。

用户可以通过各分频器改变一路时钟输出相对于其它时钟输出的相位,这种相位选择功能可用于时序粗调。1路输出还提供可编程延迟特性,具有最长10 ns的用户可选满量程延迟值。该精调延迟模块通过一个5位字进行编程,提供32个可用的延迟时间供用户选择。

AD9512非常适合数据转换器时钟应用,利用亚皮秒抖动编码信号,可实现优质的转换器性能。

AD9512提供48引脚LFCSP封装,额定温度范围为-40°C至+85°C,可以采用3.3 V单电源供电。

应用

- 低抖动、低相位噪声时钟分配

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE™转换器提供时钟

- 无线基础设施收发器

- 高性能仪器仪表

- 宽带基础设施

特性

- 两路1.6 GHz差分时钟输入

- 5个可编程分频器,1至32整数分频比

- 用于输出到输出延迟粗调的相位选择

- 3路独立的1.2 GHz LVPECL输出

加性输出抖动:225 fs均方根值 - 2路独立的800 MHz/250 MHz LVDS/CMOS输出

加性输出抖动:275 fs均方根值

1路输出提供延迟精调,5位延迟字 - 4线式或3线式串行控制端口

- 节省空间的48引脚LFCSP封装

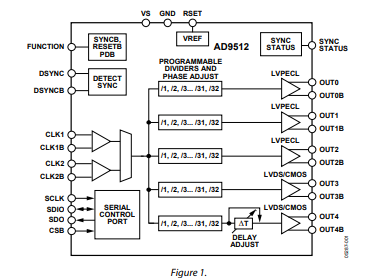

框图

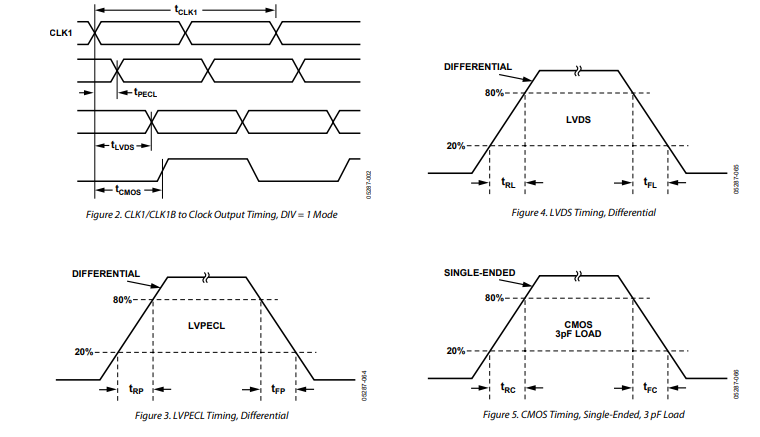

时序图

引脚配置描述

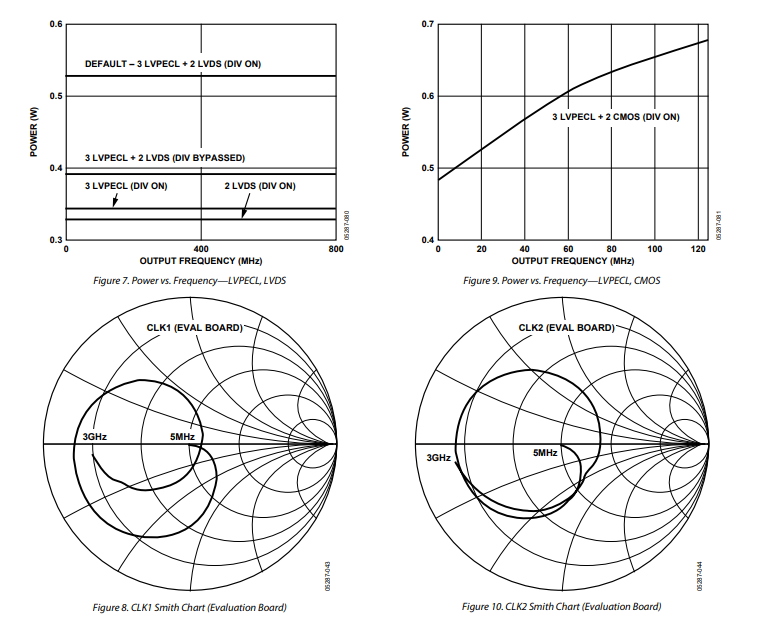

典型性能特征

功能描述

总体

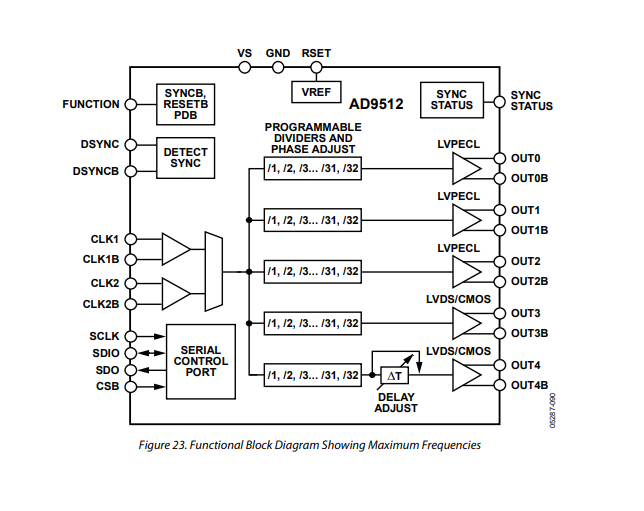

图 23 展示了 AD9512 的框图。AD9512 接受两个时钟输入(CLK1 或 CLK2)中的任意一个。该时钟可被除以 1 到 32 之间的任意整数值。输出的占空比和相对相位可进行调整。

有三个 LVPECL 输出(OUT0、OUT1、OUT2)和两个可设置为 LVDS 或 CMOS 逻辑电平的输出(OUT3、OUT4)。OUT4 也可使用可变延迟模块。

AD9512 仅提供时钟分配功能,不存在时钟倍频。输入时钟信号直接通过并可在输出端占主导地位。

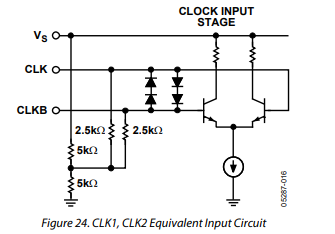

有关 CLK1 和 CLK2 的等效电路,请参见图 24。

功能引脚(FUNCTION PIN)

功能引脚(引脚 12)有三种功能,通过寄存器 58h<6:5> 中的设置进行选择。此引脚上有一个 30 kΩ 的下拉电阻。

- RESETB:58h<6:5> = 00b(默认) :在其默认模式下,功能引脚充当 RESETB,拉低时会产生异步复位或硬复位。复位结果会将默认值写入串行控制端口缓冲寄存器,并使芯片控制寄存器恢复默认值。AD9512 会立即按照默认值恢复运行。当该引脚再次拉高时,会发出异步 SYNC 信号(参见 SYNCB:58h<6:5> = 01b 部分)。

- SYNCB:58h<6:5> = 01b :功能引脚可用于使不同时钟输出之间实现同步或对齐相位。同步仅适用于以下时钟输出:

- 未断电;

- 分频器未被屏蔽(no_sync = 0);

- 未被旁路(bypass = 0)。

SYNCB 低电平有效。当 SYNCB 为低电平时,所选输出会进入预设状态。分频器以预设的分频值或快速时钟(fast clock,由 CLK1 或 CLK2 中的选定时钟输入决定)开始计数。SYNCB 的应用会影响分频器相位引脚中的所有位。无论该引脚是否也被指定用于复位或断电,只要 SYNCB 功能被选中,功能引脚就不会充当 RESETB 或 PDB。

- PDB:58h<6:5> = 11b :功能引脚也可被编程为全功率关闭。在此断电模式下,仍有一些残余电压 V 存在。在 PDB 模式下,功能引脚为高电平有效。芯片在该引脚变为低电平之前一直保持低功耗状态。返回设置请参阅芯片断电或睡眠模式 - PDB 部分,以了解有关功能引脚启动断电时的更多详细信息。

动态同步引脚(DSYNC AND DSYNCB PINS)

DSYNC 和 DSYNCB 引脚(引脚 1 和引脚 2)用于 AD9512 在多路同步配置中(见多路同步部分)。

时钟输入(CLOCK INPUTS)

AD9512 有两个时钟输入(CLK1、CLK2)可供使用。CLK2 和 CLK1 可接受高达 1600 MHz 的输入频率。图 24 为 CLK2 和 CLK1 的等效电路。

时钟输入为全差分且自偏置。如果必须使用单端输入,可通过在差分输入的一侧连接一个电容器来实现。另一侧应通过一个电容器旁路至安静的交流地。

未选择的时钟输入(无论是 CLK1 还是 CLK2)应接地,以消除不需要的时钟信号进入选定时钟输入的任何可能性。

-

深入剖析AD9512:高性能时钟分配IC的卓越之选2026-03-22 571

-

ADF5000 4GHz 至18GHz 2分频预分频器技术手册2025-04-16 1615

-

AD9513 800MHz时钟分配IC,分频器,延迟调整,三路输出技术手册2025-04-15 1227

-

AD9515 1.6 GHz时钟分配IC,分频器,延迟调整,双输出数据表2021-06-16 837

-

AD9515:1.6 GHz时钟分配IC、分频器、延迟调整、双输出数据表2021-04-13 828

-

AD9512:1.2 GHz时钟分配IC,1.6 GHz输入,分频器,延迟调整,五输出数据表2021-03-22 911

-

AD9510:1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出2021-03-21 979

-

AD9512: 1.2 GHz Clock Distribution IC, 1.6 GHz Inputs, Dividers, Delay Adjust, Five Outputs Data Sheet2021-01-28 680

-

AD9512 1.2 GHz时钟分配IC、2路1.6 GHz输入、分频器、延迟调整、5路输出2019-02-15 545

-

1.2千兆赫时钟分配IC 1.6GHz输入分频器延迟调整五输出ad9512数据表2017-10-19 1037

全部0条评论

快来发表一下你的评论吧 !