ADN2807 155/622 Mbps时钟和数据恢复IC,集成限幅放大器技术手册

描述

概述

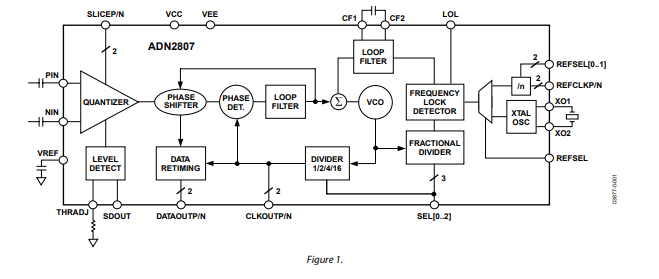

ADN2807可提供下列接收器功能:量化、信号电平检测、时钟和数据恢复,适用于OC-3、OC-12和15/14 FEC数据速率。该器件满足所有的SONET抖动要求,包括抖动传递、抖动产生和抖动容差。所有规格均相对于–40°C至+85°C环境温度而言,除非另有说明。

数据表:*附件:ADN2807 155 622 Mbps时钟和数据恢复IC,集成限幅放大器技术手册.pdf

该器件主要用于WDM系统,可以结合外部参考时钟或配有外部晶振的片内振荡器使用。ADN2807同时支持本有速率和15/14速率数字包装器,无需更改参考时钟。

该器件配合PIN二极管和TIA前置放大器,可以实现高度集成的低成本、低功耗光纤接收器。

当输入信号电平降至用户可调阈值以下时,接收器前端信号检测电路会予以提示。信号检测电路具有迟滞特性,可防止输出震颤。

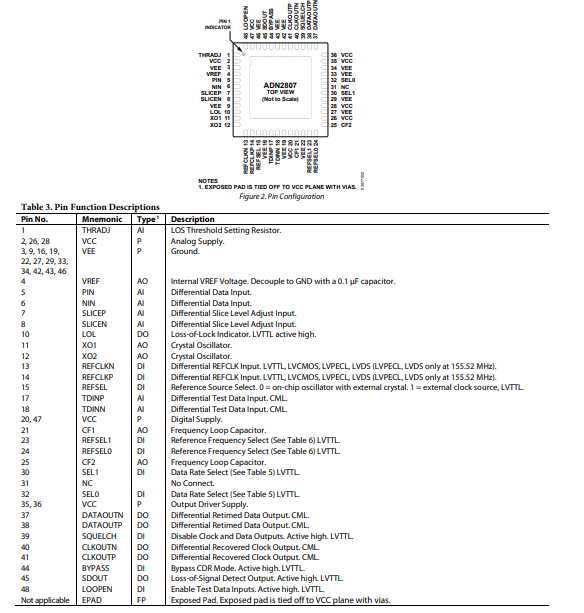

ADN2807采用紧凑型7 mm × 7 mm、48引脚芯片级(LFCSP)封装。

应用

- SONET OC-48、SDH STM-16和15/14 FEC

- WDM应答器

- 再生器/中继器

- 测试设备

- 背板应用

特性

- 符合SONET抖动传递/产生/容差要求

- 量化器灵敏度:4 mV(典型值)

- 可调限幅电平:±100 mV

- 取得专利的时钟恢复架构

- 信号丢失检测范围:3 mV至15 mV

- 单一参考时钟频率适用于所有速率,包括15/14 (7%)包装器速率

- 选择19.44 MHz、38.88 MHz、77.76 MHz或155.52 MHz REFCLK

- REFCLK输入:LVPECL/LVDS/LVCMOS/LVTTL兼容(LVPECL/LVDS,仅在155.52 MHz时)

- 可选19.44 MHz片内振荡器与外部晶振配合使用

- 失锁指示器

- 用于高速测试数据的回送模式

- 输出静噪和旁路特性

- 单电源供电:3.3 V

- 低功耗:540 mW(典型值)

- 7 mm × 7 mm、48引脚LFCSP

框图

引脚配置描述

术语定义

最大、最小和典型规格

各项参数的规格源自对多片晶圆上多个器件的数据进行统计分析。参数的典型值是该数据分布的平均值。对于某个参数,如果要计算最大值(或最小值),则是将分布的平均值加上(或减去)六个标准差。此程序旨在容忍生产过程中的变化。如果平均值为 1.5 个标准差,那么剩余的 4.5 个标准差对应的故障率仅为每百万个器件中 3.4 个。对于所有测试参数,测试限制都有容差范围,以考虑测试设备的变化,从而确保没有器件的性能超出数据表规格。

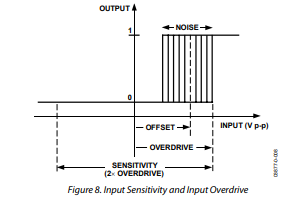

输入灵敏度与输入过驱动

灵敏度和过驱动指标与量化器的失调电压、增益和噪声相关。量化器的逻辑输出与模拟电压输入之间的关系如图 8 所示。对于足够大的正输入电压,输出始终为逻辑 1;对于足够大的负输入电压,输出始终为逻辑 0。然而,输出逻辑 1 和输出逻辑 0 之间的转换并非在精确的输入电压电平处发生,而是在一定的输入电压范围内。在此范围内,输出可能为逻辑 1 或 0,甚至可能无法达到有效逻辑状态。此范围的宽度由量化器输入电压噪声决定。该范围的中心是量化器输入失调电压。输入过驱动是指在 1×10⁻¹⁰ 的置信水平下保证正确逻辑电平所需的信号幅度。

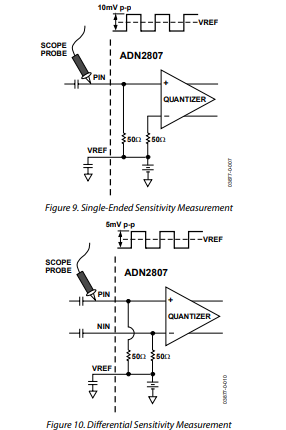

单端与差分

通常采用交流耦合来驱动量化器的输入。这些输入内部连接到大约 -0.6 V 的共模电位。驱动 ADN2807 单端输入并在图 9 所示点用示波器探头观察量化器输入时,会显示一个二进制信号,其平均值等于共模电位,瞬时值在平均值上下波动。测量该信号的峰 - 峰值幅度并将其最小值称为量化器灵敏度很方便。参考图 8,由于需要同时考虑正失调和负失调,灵敏度是过驱动值的两倍。

差分驱动 ADN2807(见图 10)时,用示波器探头观察量化器输入,灵敏度似乎有所提高。这是使用单端探头产生的错觉。一个 5 mV 峰 - 峰值信号似乎只能驱动 ADN2807 量化器的一半。然而,单端探头测量的只是信号的一半,因为量化器的另一个输入信号是所观察信号的互补信号,所以真实的量化器输入信号是该值的两倍。

-

解析ADN2804:622 Mbps时钟和数据恢复IC的卓越性能与应用指南2026-03-23 369

-

ADN2804 622Mbps时钟和数据恢复IC,集成限幅放大器技术手册2025-04-15 3021

-

ADN2913:连续速率6.5 Mbps至8.5 Gbps时钟和数据恢复IC,集成限幅放大器/均衡器数据表2021-05-25 1008

-

ADN2804:带集成限幅放大器的622 Mbps时钟和数据恢复IC产品说明书2021-05-09 2229

-

ADN2806:622 Mbps时钟和数据恢复IC数据表2021-05-08 1348

-

ADN2807:155/622 Mb/s时钟和数据恢复IC,带集成限幅放大器数据表2021-04-17 883

-

ADN2917:连续速率8.5 Gbps 至11.3 Gbps 时钟和数据恢复IC,集成限幅放大器/均衡器2021-03-22 910

-

ADN2807 155/622 Mbps时钟和数据恢复IC,集成限幅放大器2019-02-22 1184

全部0条评论

快来发表一下你的评论吧 !