MAX9392任意逻辑至LVDS、双路、2 x 2交叉点开关技术手册

描述

概述

MAX9392/MAX9393双2 x 2交叉点开关能够实现高速、低功耗、低噪声信号切换。MAX9392/MAX9393将两路差分输入中的一路复用到一路或两路低压差分信号(LVDS)输出。独立的使能输入对每路差分信号进行通、断控制。

数据表:*附件:MAX9392任意逻辑至LVDS、双路、2 x 2交叉点开关技术手册.pdf

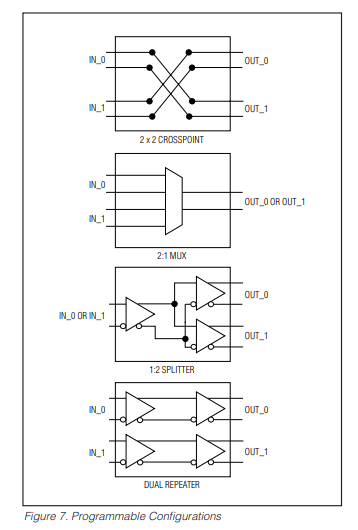

4路 LVCMOS/LVTTL逻辑输入(每通道两个)控制输入与输出之间的内部连接。可灵活实现以下配置:2 x 2交叉开关、2:1复用器、1:2分配器或双转发器,从而使MAX9392/MAX9393可理想用作故障容错系统中的保护开关、诊断器中的环回开关、时钟/数据分配中的扇出缓冲器和信号恢复。

当输入未被驱动或共模电压超出指定范围时,故障保护电路将输出拉至差分低电平。MAX9392为LVDS、HSTL和其它以GND为参考的差分输入提供高电平输入失效检测;MAX9393为LVPECL、CML和其它以VCC为参考的差分输入提供低电平输入失效检测。

具有98ps~(P-P)~ (最大值)超低抖动的伪随机序列(PRBS)能够在对定时误差高度敏感的高速链路中保证可靠通信,特别适合需要时钟和数据恢复的应用,或串行器和解串器应用。高速开关性能确保工作在1.5GHz,并保证小于67ps (最大值)的通道间偏差。

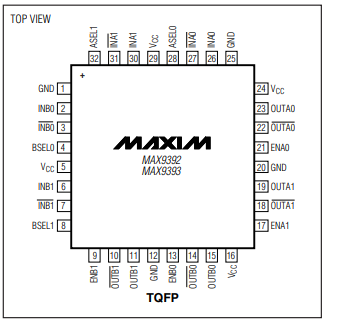

LVDS输入、输出兼容于TIA/EIA-644 LVDS标准,LVDS输出可驱动100Ω负载。MAX9392/MAX9393提供32引脚TQFP封装,工作在-40°C至+85°C扩展级温度范围。

交叉切换产品请参考MAX9390/MAX9391。

应用

- 局端背板时钟分配

- DSLAM

- 故障容错系统

- 高速电信/数据通信设备

- 保护开关

特性

- 250mV差分输出摆幅,可工作在1.5GHz

- 2ps

RMS(最大)随机抖动 - 交流指标保证接受150mV差分输入

- 信号输入可接受任何差分信号标准

- 用于时钟或高速数据的LVDS输出

- 高电平输入失效检测(MAX9392)

- 低电平输入失效检测(MAX9393)

- 3.0V至3.6V供电范围

- LVCMOS/LVTTL逻辑输入控制信号切换

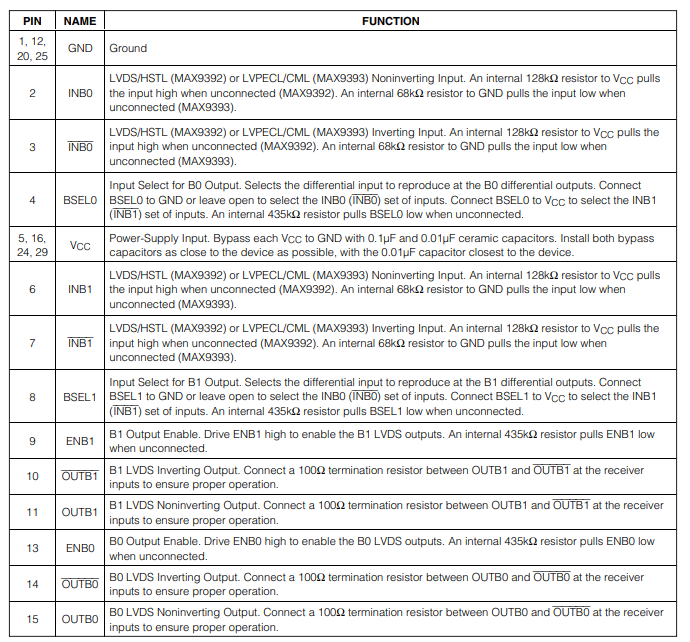

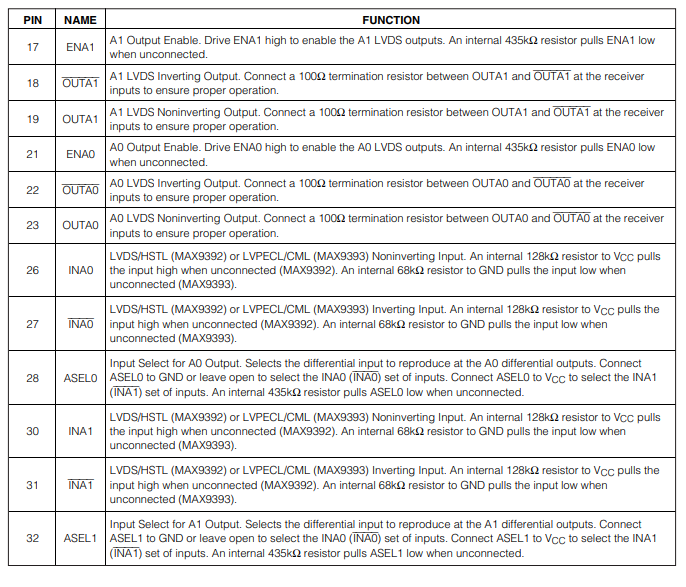

引脚描述

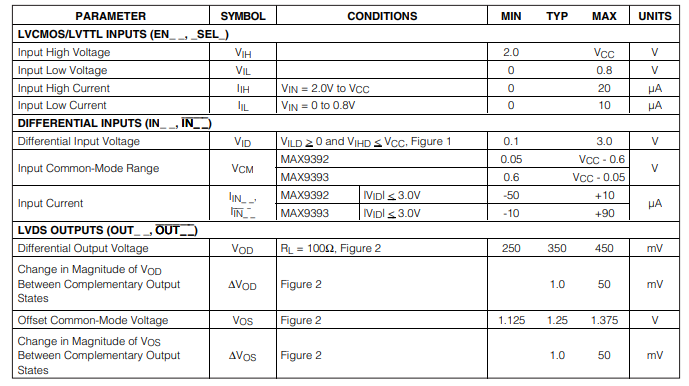

DC电气特性

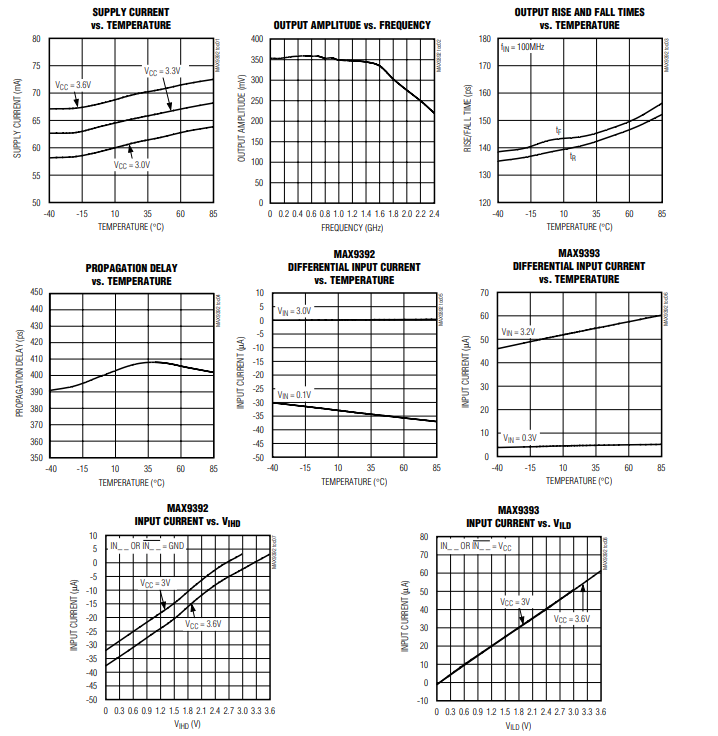

典型操作特性

详细说明

低压差分信号(LVDS)接口标准为受控阻抗介质上的点对点通信提供了一种信令方法,该标准由美国国家标准协会(ANSI)TIA/EIA - 644 定义。LVDS 使用比其他通信标准更低的电压摆幅,从而在降低电磁辐射和系统对噪声敏感度的同时,实现更高的数据速率并降低功耗。

MAX9392/MAX9393 1.5G Hz 双 2×2 交叉点开关优化高速信号,实现点对点接口。MAX9392 支持 LVDS 和高速晶体管 - 晶体管逻辑(HSTL),而 MAX9393 接受 LVPECL 和 CML 电平。这两款器件都将输入信号路由至一个或两个 LVDS 输出。

配置为 1:2 分配器时,器件会复制所选输入的配置,创建信号副本以实现保护切换。配置为中继器时,器件在双声道缓冲器中运行。中继可恢复信号幅度,从而实现隔离。在媒体段或长距离媒体传输中,这有助于信号传输。

配置为 2:1 多路复用器时,可选择主信号或备用信号,以提供保护切换、故障转移或其他应用功能。

输入故障保护

MAX9392/MAX9393 的差分输入具备内部故障保护功能。故障保护电路会在输入未驱动或共模电压超出规定范围时,强制将差分输入设置为低电平状态。MAX9392 为 LVDS、HSTL 及其他高速差分输入提供高电平输入故障保护。MAX9393 为 LVPECL、CML 及其他低压差分输入提供低电平输入故障保护。

选择功能

SEL 逻辑输入控制每个通道的输入和输出信号连接。SEL0 和 SEL1 可将器件配置为差分交叉点开关、2:1 多路复用器或 1:2 分配器(见图 7 )。有关模式选择设置,请参见表 1(插入 A 或 B 代表相应表格 )。A 通道和 B 通道的输入具有独立的选择输入,可为每个通道实现不同的配置。

使能功能

EN 逻辑输入用于启用或禁用每组差分输出。将 EN_0 连接到 VCC 可启用 OUT_0/OUT_0 差分输出对;将 EN_0 连接到地可禁用该差分输出对。禁用时,差分输出对会呈现差分故障低状态。

-

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉点开关技术手册2025-04-16 951

-

MAX9393任意逻辑至LVDS、双路、2 x 2交叉点开关技术手册2025-04-15 1314

-

DS10CP152 1.5Gbps 2X2 LVDS交叉点开关数据表2024-07-09 247

-

DS90CP22 800 Mbps 2x2 LVDS交叉点开关数据表2024-07-05 293

-

DS25CP152 3.125Gbps LVDS 2x2交叉点开关数据表2024-07-03 354

-

2x2 LVDS交叉点开关SN65LVCP22数据表2024-06-26 308

-

双路2x2交叉点开关MAX3840相关资料下载2021-04-02 1237

-

美国国家半导体两款低功率LVDS 2x2交叉点开关电路2018-08-27 1302

-

MAX14885E 低电容VGA 2:2双通道图形交叉点开关2010-04-10 840

-

MAX4989 USB 2.0高速4选2交叉点开关2009-02-23 944

-

Maxim推出双向、4选2、USB 2.0交叉点开关MAX42008-10-30 979

全部0条评论

快来发表一下你的评论吧 !