MAX9390任意逻辑至LVDS、双路、2 x 2交叉点开关技术手册

描述

概述

MAX9390/MAX9391是双路2 x 2交叉点开关,完成高速、低功耗和低噪声信号分配。对于每个通道来说,MAX9390/MAX9391可将两组差分输入信号对中的一组分配到任何一个或两个LVDS输出端,独立的使能输入可闭合或关断每一个差分输出对。

数据表:*附件:MAX9390任意逻辑至LVDS、双路、2 x 2交叉点开关技术手册.pdf

4个LVCMOS/LVTTL逻辑输入端(每通道两个)控制输入和输出的内部互联,这种灵活性允许下列配置方式:2 x 2交叉点开关、2:1多路复用器、1:2分割器、2组中继器。这使得MAX9390/MAX9391尤其适合于容错系统中的保护切换、诊断中的环回切换、时钟/数据分配中的扇出缓冲,以及信号再生应用。

当输入无驱动或共模电压超过规定范围时,安全失效电路强制输出为差分低电平状态。MAX9390为LVDS、HSTL和其它参考地的差分输入信号,提供高电平输入安全失效检测;而MAX9391为LVPECL、CML和其它参考VCC的差分输入信号,提供低电平输入安全失效检测。

超低的(最大82ps (P-P) )伪随机比特流(PRBS)抖动确保高速链路的可靠通讯,这些高速链路对定时误差极为敏感,特别是那些包含时钟和数据恢复,或串行器和解串器的高速链路。高速开关性能保证1.5GHz的工作频率和通道间小于65ps (最大)的扭曲。

LVDS输入和输出特性兼容于TIA/EIA-644 LVDS标准,LVDS输出可驱动100Ω负载,MAX9390/MAX9391提供32引脚的TQFP封装,工作于-40°C至+85°C扩展温度范围。

另请参考具有顺畅的引脚排列的MAX9392/MAX9393。

应用

- 局端背板时钟分配

- DSLAM

- 故障容错系统

- 高速电信/数据通信设备

- 保护开关

特性

- 250mV差分输出工作频率可达1.5GHz

- 2ps~(RMS)~ (最大)随机抖动

- 对于150mV差分输入,保证AC特性

- 信号输入端接受任何差分信号标准

- 适合于时钟或高速数据的LVDS输出

- 高电平输入安全失效检测(MAX9390)

- 低电平输入安全失效检测(MAX9391)

- 电源电压范围3.0V至3.6V

- LVCMOS/LVTTL逻辑输入控制信号路由

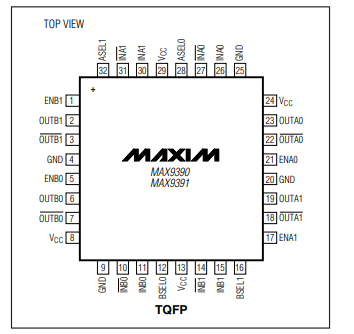

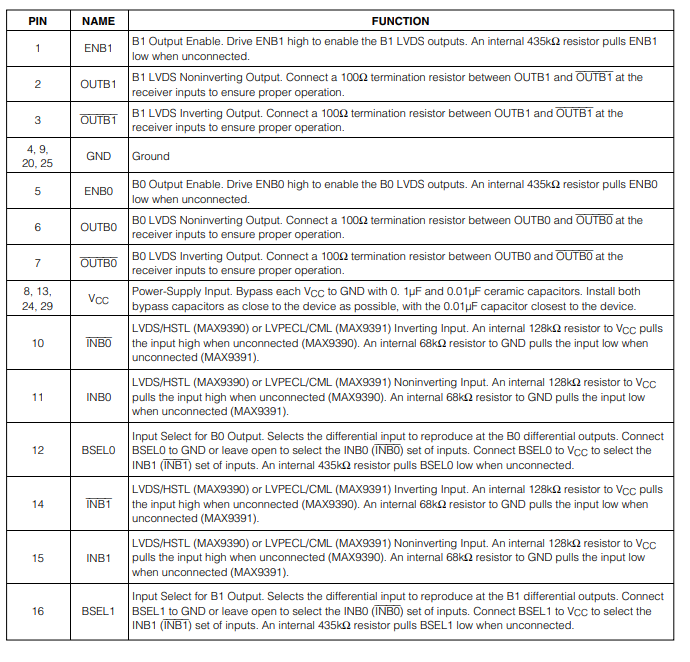

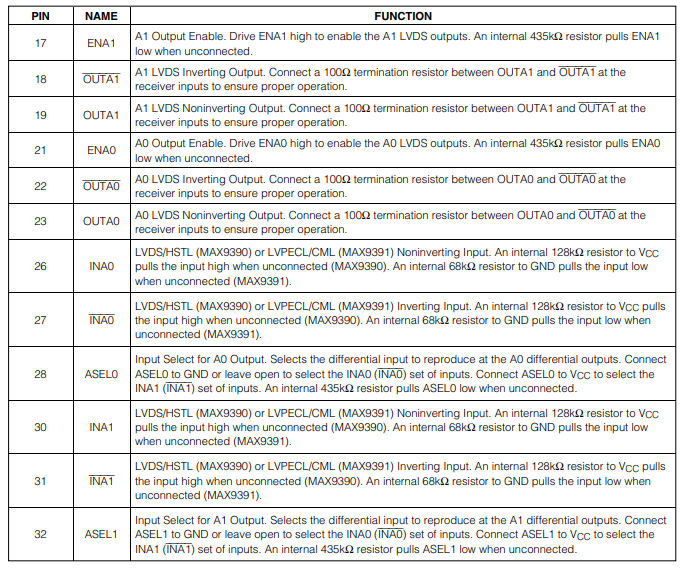

引脚配置描述

应用信息

差分输入

MAX9390/MAX9391 的输入可接受共模电压在指定范围内的任何差分信令标准。故障保护功能可检测共模输入信号电平,并在共模电压超出规定范围,或者输入未被驱动时,生成差分输出低电平状态。对于 MAX9390,将未使用的输入连接到 VCC;对于 MAX9391,连接到 GND。

差分输出

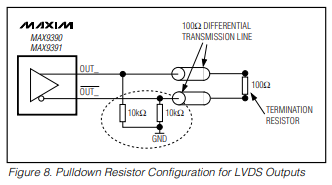

当电源电压高于 0.6V 时,LVDS 输出的输出共模电压无法正确建立。这种情况可能在 LVDS 输出驱动 LVDS 输入的芯片时出现。为避免这种情况,对于 MAX9390/MAX9391,可在同相输出(OUT⁺)连接一个 10kΩ 电阻至地,并在反相输出(OUT⁻)连接一个 10kΩ 电阻至地。这些下拉电阻可使输出保持在 0.6V 以下(见图 8)。

扩展 LVDS 输出端口数量

通过级联器件来构建更大的开关。在确定最大允许开关尺寸时,需考虑总传播延迟和总抖动。

电源旁路

将每个 VCC 通过表面贴装陶瓷 0.1μF 和 0.01μF 高频电容旁路至 GND,尽可能靠近器件。安装 0.01μF 电容时,使其尽可能靠近器件的输入和输出引脚。

差分走线

MAX9390/MAX9391 的输入和输出走线应具有 50Ω 特性阻抗。保持差分走线间的距离恒定,消除尖锐拐角,避免差分走线出现不连续情况。保持差分走线长度一致,以最大限度降低共模噪声干扰。尽量减少差分输入和输出走线上的过孔数量,以防止阻抗不连续。通过连接器和电缆保持 50Ω 特性阻抗,匹配电缆的电气长度,从而减少反射并最小化偏斜。

输出端接

在接收器输入端的差分输出之间使用 100Ω 电阻来端接 LVDS 输出。LVDS 输出需要 100Ω 端接电阻才能正常工作。确保输出电流不超过“绝对最大额定值”中规定的电流限制。在所有工作条件下,均需遵守 MAX9390/MAX9391 的总热限制。

电缆和连接器

传输介质应使用匹配的差分阻抗。使用具有匹配差分阻抗的电缆和连接器,以最大限度减少不连续性。避免使用不平衡电缆。平衡电缆(如双绞线对)可提供更好的信号质量,且由于抵消效应,往往会产生较少的电磁干扰(EMI)。

电路板布局

使用信号、电源和接地(PG)层相互独立的四层印制电路板(PCB),为高速信令应用提供平面。尽可能将 Vcc 旁路至 GND,靠近器件。尽可能在靠近接收器输入处安装端接电阻。匹配差分走线的电气长度,以最小化信号偏斜。

-

SN65LVCP22:高速2x2 LVDS交叉点开关的卓越之选2025-12-30 484

-

探索DS10CP152:1.5 Gbps 2x2 LVDS交叉点开关的卓越性能2025-12-26 478

-

探索DS10CP152Q:汽车级1.5 Gbps 2x2 LVDS交叉点开关2025-12-25 409

-

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉点开关技术手册2025-04-16 1425

-

MAX9392任意逻辑至LVDS、双路、2 x 2交叉点开关技术手册2025-04-15 1840

-

DS10CP152 1.5Gbps 2X2 LVDS交叉点开关数据表2024-07-09 336

-

DS90CP22 800 Mbps 2x2 LVDS交叉点开关数据表2024-07-05 411

-

DS25CP152 3.125Gbps LVDS 2x2交叉点开关数据表2024-07-03 484

-

2x2 LVDS交叉点开关SN65LVCP22数据表2024-06-26 394

-

双路2x2交叉点开关MAX3840相关资料下载2021-04-02 1309

-

美国国家半导体两款低功率LVDS 2x2交叉点开关电路2018-08-27 1359

-

MAX14885E 低电容VGA 2:2双通道图形交叉点开关2010-04-10 892

-

Maxim推出双向、4选2、USB 2.0交叉点开关MAX42008-10-30 1048

全部0条评论

快来发表一下你的评论吧 !