MAX9389差分8:1 ECL/PECL多路复用器,带有双输出缓冲器技术手册

描述

概述

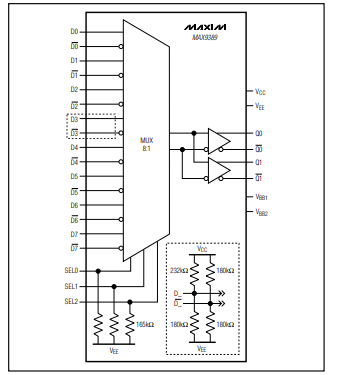

MAX9389是具有两路输出缓冲器的全差分、高速、低抖动的8至1 ECL/PECL多路复用器,该器件设计应用于时钟和数据分配,具有极低的传输延迟(典型值310ps)和输出至输出扭曲(典型值30ps)。

数据表:*附件:MAX9389差分ECL PECL多路复用器,带有双输出缓冲器技术手册.pdf

3个单端选择输入SEL0、SEL1、SEL2控制复用功能。多路复用器选择输入兼容于ECL/PECL逻辑,其内部参考至片上输出电压(V BB1 , V BB2 ),标称为VCC - 1.425V。选择输入端可接受幅度在VCC和VEE之间的输入信号,输入端内部下拉到V EE ,确保输入端开路时处于缺省的低电平状态。

差分输入D_和/D_可以配置成接受单端信号输入,只需将未用的互补输入端连接到作为参考电压的片上电源输出端(V BB1 , V BB2 )即可。所有差分输入端都有偏置和箝位电路,当输入端开路或连接到VEE时,强制电路输出低电平(缺省值)。

MAX9389工作于2.375V至5.5V的宽电源电压范围,提供32引脚TQFP和薄型QFN两种封装,工作于-40°C至+85°C的扩展温度范围。

应用

- 局端背板时钟分配

- DSLAM/DLC

- 高速电信与数据通信应用

特性

- 310ps传输延迟

- 保证2.7GHz工作频率

- 0.3ps

RMS随机抖动 - <30ps输出至输出扭曲

- -2.375V至-5.5V电源电压用于差分LVECL/ECL

- +2.375V至+5.5V电源电压用于差分LVPECL/PECL

- 输入开路时,输出低电平

- 2路输出缓冲器

2kV ESD保护(人体模型)

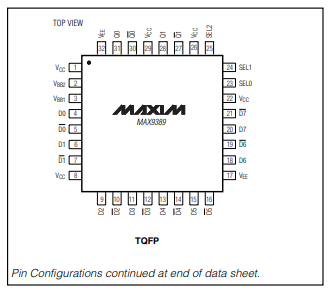

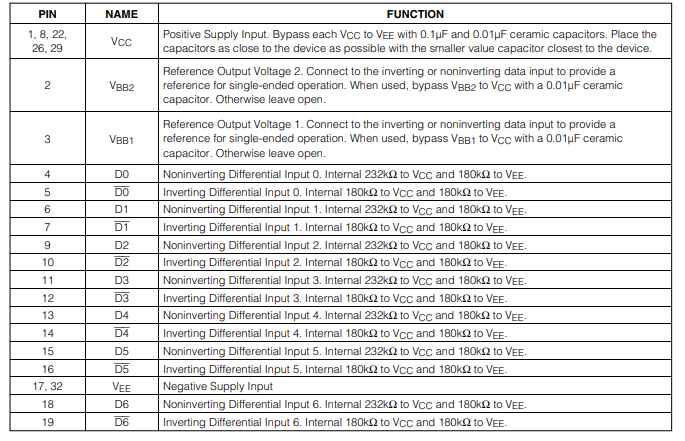

引脚配置描述

框图

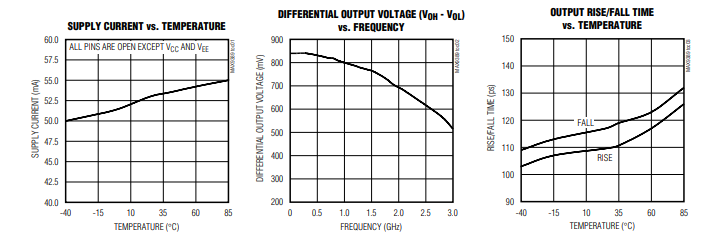

典型操作特性

应用信息

输出端接

用一个 50Ω 至 VCC、-2V 或等效戴维南端接的电阻对每个输出进行端接。使每个 Q 和 Q̅ 输出的端接相同,以将信号失真降至最低。当采用单端输出时,同时端接 Q 和 Q̅ 。

确保输出电流不超过“绝对最大额定值”表中规定的电流限制。在所有工作条件下,器件的总热限制均不应被超过。

电源旁路

使用高频表面贴装陶瓷 0.1μF 和 0.01μF 电容将每个 VCC 旁路至 VEE。对于 PECL,用 0.1μF 电容将每个 VCC 旁路至 VEE。将电容尽可能靠近器件引脚放置。0.01μF 电容应最靠近器件引脚。

连接旁路电容至地时使用多个过孔。使用 VBB1 或 VBB2 参考输出时,用 0.01μF 陶瓷电容将其旁路至 VCC。如果不使用 VBB1 或 VBB2 参考输出,可将其悬空。

-

MAX9388差分5:1或4:1 ECL/PECL多路复用器,带有单/双输出缓冲器技术手册2025-04-15 1227

-

DS40MB200双通道4 Gbps 2:1/1:2 CML多路复用器/缓冲器数据表2024-07-05 523

-

SCAN15MB200双通道1.5 Gbps 2:1/1:2 LVDS多路复用器/缓冲器数据表2024-06-28 500

-

双 1-of-4 多路复用器/解复用器-74CBTLV3253_Q1002023-02-17 888

-

1-of-8 FET 多路复用器/解复用器-CBT32512023-02-16 886

-

模拟开关和多路复用器的基础参数2022-11-08 1092

-

具有8:1多路复用器的通用输入/输出(GPIO)扩展功能2022-11-07 836

-

组合逻辑基础之多路复用器设计2022-08-04 4312

-

KOYUELEC光与电子提供ASW3410双通道差分多路复用器2022-06-06 1046

-

MAX4638,MAX4639低电压模拟多路复用器2012-11-15 8927

全部0条评论

快来发表一下你的评论吧 !