MAX9388差分5:1或4:1 ECL/PECL多路复用器,带有单/双输出缓冲器技术手册

描述

概述

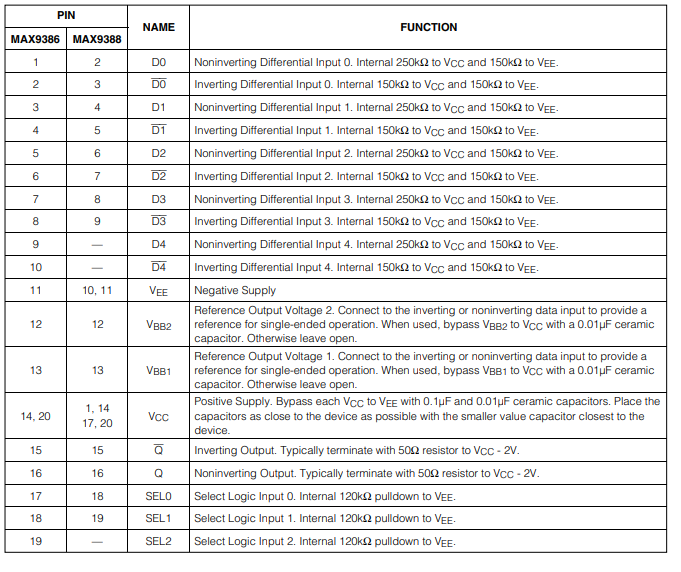

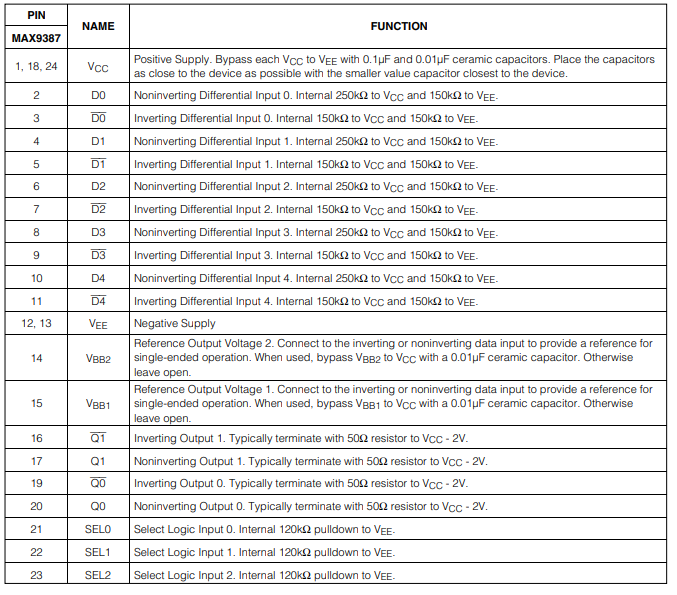

MAX9386/MAX9387/MAX9388是具有输出缓冲器、全差分、高速、低抖动的ECL/PECL多路复用器。这些器件设计应用于时钟和数据分配,具有极低的传输延迟(典型值318ps)和输出至输出扭曲(典型值3.9ps)。MAX9386是具有一个输出缓冲器的5:1多路复用器;MAX9387是具有2个缓冲器的5:1多路器,目的在于应用于冗余系统;MAX9388是具有一个输出缓冲器的4:1多路复用器,其引脚兼容于MC100EP57。

数据表:*附件:MAX9388 ECL PECL多路复用器,带有单 双输出缓冲器技.pdf

3个单端选择输入SEL0、SEL1、SEL2控制MAX9386/MAX9387的复用功能,而MAX9388只有2个选择输入端SEL0和SEL1。多路复用器选择输入兼容于ECL/PECL逻辑,其内部参考至片上输出电压V BB ,标称为VCC - 1.425V。选择输入端可接受幅度在VCC和VEE之间的输入信号,输入端内部下拉到V EE ,确保输入端开路时处于缺省的低电平。

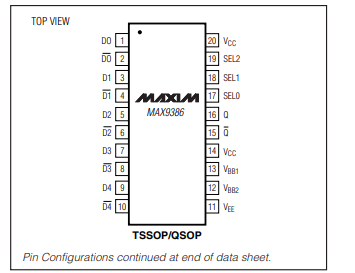

差分输入D_和/D_可以配置成接受单端信号输入,只需将未用的互补输入端连接到作为参考电压的片上电源输出端VBB即可。所有差分输入端都有偏置和箝位电路,当输入端开路时,强制电路输出低电平(缺省值)。MAX9386/MAX9387/MAX9388可在很宽的电源电压范围内工作(|VCC - V EE |从2.735V至5.5V)。MAX9386/MAX9387提供20引脚TSSOP和QSOP封装形式,MAX9387提供24引脚TSSOP和QSOP封装。

应用

- 局端背板时钟分配

- DSLAM/DLC

- 高速电信与数据通信应用

特性

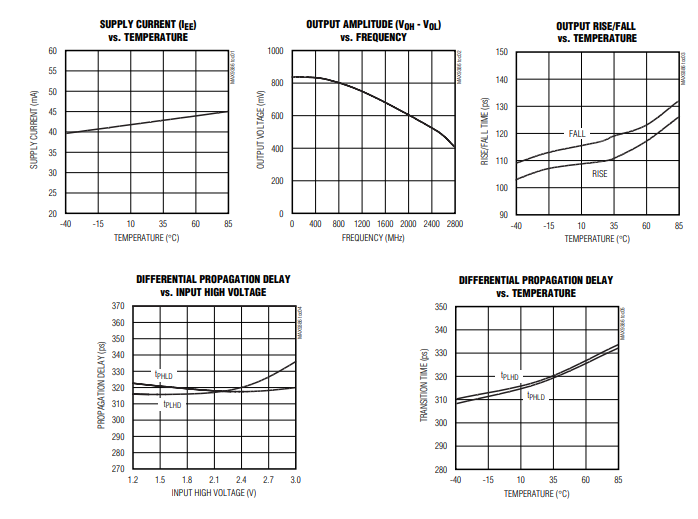

- 318ps (典型)传输延迟

2.7GHz翻转频率

- 0.3ps(RMS)随机抖动

- <14ps (最大,+25°C)输出至输出扭曲(MAX9387)

- -2.375V至-5.5V电源电压用于差分LVECL/ECL

- +2.375V至+5.5V电源电压用于差分LVPECL/PECL

- 输入开路时,输出低电平

- 2路输出缓冲器(MAX9387)

- 引脚兼容于MC100EP57 (MAX9388EUP)

2kV ESD保护(人体模型)

引脚配置描述

典型操作特性

应用信息

输出端接

通过等效戴维南端接方式,使用 50Ω 到 -2V 或等效电源的电阻对输出进行端接。使每个 Q 和 Q̅ 输出的端接一致,以实现最小信号失真。当采用单端输出时,需同时端接 Q 和 Q̅ 。

确保输出电流不超过“绝对最大额定值”表中规定的电流限制。在所有工作条件下,都应遵守器件的总热限制。

电源旁路

使用高频表面贴装的 0.1μF 和 0.01μF 陶瓷电容,将 VCC 旁路至 VEE。对于正发射极耦合逻辑(PECL),使用 0.1μF 电容将每个 VCC 旁路至 VEE。尽可能将电容靠近器件引脚放置,其中 0.01μF 电容应最靠近引脚。

连接旁路电容到地时使用多个过孔。使用 VBB1 或 VBB2 参考输出时,用 0.01μF 陶瓷电容将其旁路至 VCC。若不使用 VBB1 或 VBB2 参考输出,可将其悬空。

走线

电路板走线布局对于维持高速差分信号的信号完整性至关重要。维持信号完整性可通过减少反射和偏斜,以及提高共模噪声抑制能力来实现。

信号反射由 50Ω 特性阻抗的不连续引起。通过保持差分走线之间的距离不变或使用渐变线,避免出现不连续情况。不使用尖锐拐角,减少过孔数量。保持走线间距恒定也有助于提高共模噪声抑制能力。通过匹配差分走线的电气长度来减少偏斜。

-

MAX9389差分8:1 ECL/PECL多路复用器,带有双输出缓冲器技术手册2025-04-15 1057

-

TMUXHS4212双通道差分2:1多路复用器或1:2多路信号分离器数据表2024-07-12 614

-

DS40MB200双通道4 Gbps 2:1/1:2 CML多路复用器/缓冲器数据表2024-07-05 515

-

SCAN15MB200双通道1.5 Gbps 2:1/1:2 LVDS多路复用器/缓冲器数据表2024-06-28 493

-

双 1-of-4 多路复用器/解复用器-74CBTLV3253_Q1002023-02-17 875

-

双 1-of-4 FET 多路复用器/解复用器-CBT32532023-02-16 628

-

KOYUELEC光与电子提供ASW3410双通道差分多路复用器2022-06-06 1041

-

AD8174缓冲模拟多路复用器2020-06-17 1999

-

MAX4638,MAX4639低电压模拟多路复用器2012-11-15 8927

全部0条评论

快来发表一下你的评论吧 !