MAX9155低抖动、低噪声、LVDS转发器,SC70封装技术手册

描述

概述

MAX9155是一款低压差分信号(LVDS)中继器,接收单路LVDS输入,再生为另一路LVDS输出。其低抖动,低噪声等特性,尤其适合于缓冲长距离或噪声环境下发送的LVDS信号,如通过电缆和背板等。

数据表:*附件:MAX9155低抖动、低噪声、LVDS转发器,SC70封装技.pdf

MAX9155的微小尺寸使其特别适合于要求尽可能减小多点背板应用中的分支连线长度。SC70封装(SOT23尺寸的一半)能够将MAX9155置于连接器附近,以尽可能减小分支连线长度和总线上的信号反射。MAX9155的输出与目标IC,如FPGA或ASIC等之间的点对点连接,允许目标IC放置在离总线连接器较远的地方。

23psP-P的超低加性系统抖动和0.6psRMS的加性随机抖动等特性,保证在那些定时误差极其敏感的高速链路中,尤其是那些包含时钟和数据恢复电路、PLL、串行器或解串器应用中,进行可靠地通讯。MAX9155的转换性能保证200Mbps的数据传输速率,且通过保证0.5ns的最小输出过渡时间,以尽可能减小辐射噪声。当输入处于未驱动的开路、短路或终端匹配时,MAX9155的安全失效电路设置输出为高。

MAX9155工作于+3.3V单电源,仅消耗10mA电源电流,满足-40°C至+85°C的工作温度范围。对于四路总线LVDS驱动器,请参考MAX9129的数据资料;对于SC70封装的低抖动、低噪声的LVPECL至LVDS电平转换器,请参考MAX9156的数据资料。

应用

- 上/下路复用器

- 电缆中继器

- 蜂窝电话基站

- 数字交叉连接

- DSLAM

- 多点总线

- 网络路由器和交换机

特性

- 微型SC70封装

- 超低抖动

- 23ps

P-P加性系统抖动 - (2 ^23^ -1 PRBS)

- 0.6ps

RMS加性随机抖动

- 23ps

- 0.5ns (最小)过渡时间,以尽可能减小辐射噪声

- 保证200Mbps的数据速率

- 当输入未驱动(开路,终端匹配或短路)时,安全失效电路设置输出为高

- 10mA的低电源电流

- 在安全失效状态时,6mA的低电源电流

- 符合ANSI/EIA/TIA-644 LVDS标准

- 断电模式下,输入输出均处于高阻态

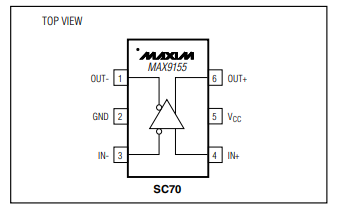

引脚配置描述

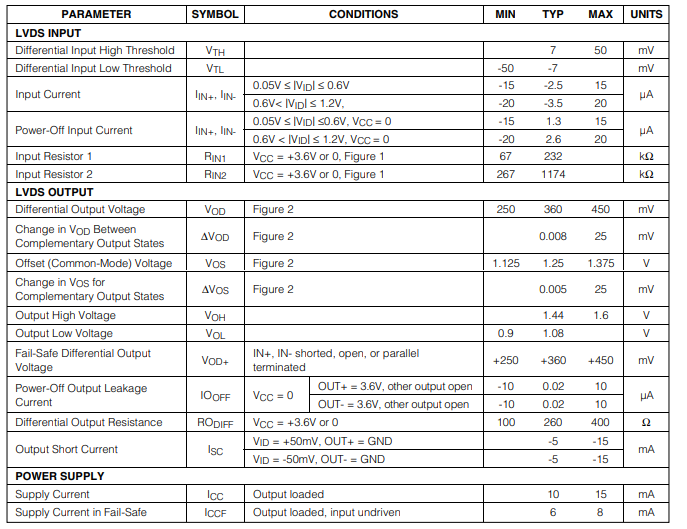

DC电气特性

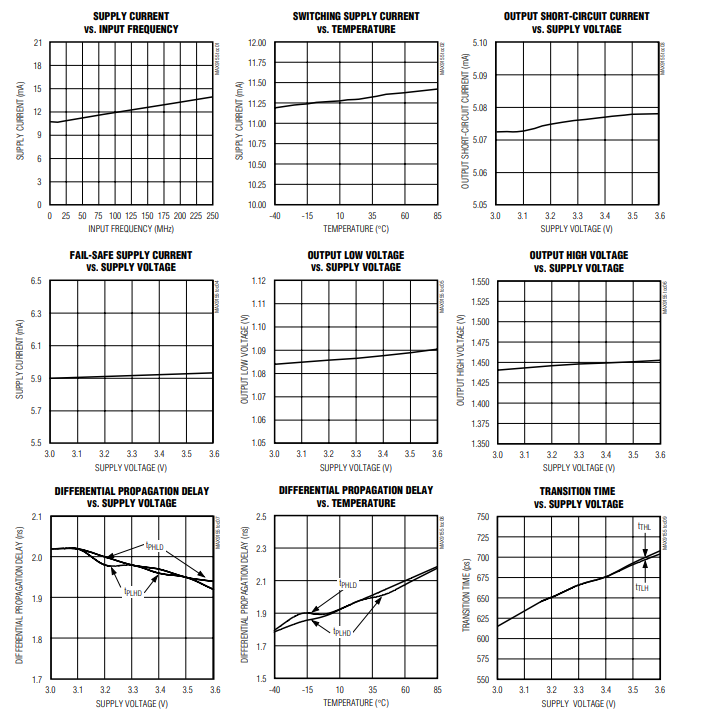

典型操作特性

应用信息

电源旁路 :用0.01μF高频表面贴装陶瓷电容将VCC旁路,尽可能靠近器件。

差分走线 :输入和输出的走线特性会影响MAX9155的性能。使用受控阻抗差分走线。通过将走线紧密排列成差分对的形式,确保信号以共模方式耦合。保持差分对内的距离一致,避免出现不连续情况;避免90°转弯,并尽量减少过孔数量,以减少阻抗不连续问题。

电缆和连接器 :LVDS标准定义了差分特性阻抗为100Ω且端接特性阻抗的互连信号电平,同时允许特性阻抗为90Ω至132Ω且端接的情况(详见“端接”部分)。使用具有匹配差分阻抗的电缆和连接器,以减少阻抗不连续问题。避免使用非平衡电缆,如带状电缆或同轴电缆。平衡电缆,如双绞线,具有更好的信号质量,且能产生较少的电磁干扰,不易拾取共模噪声,LVDS接收器可抑制共模噪声。

端接

对于点对点链路,端接电阻应位于LVDS接收器输入端,并与传输线的差分特性阻抗匹配。

对于一端驱动的多点总线,在总线另一端用与总线负载差分特性阻抗匹配的电阻进行端接。

对于两端均由点驱动器驱动的多点总线,在总线两端都用与总线负载差分特性阻抗匹配的电阻进行端接。当在两端进行端接,或需要驱动大量分支时,需要使用总线LVDS(BLVDS)驱动器来驱动双端接的多点总线。MAX9155并非用于驱动双端接的多点LVDS总线。

差分输出电压电平取决于互连的差分特性阻抗和端接电阻值。MAX9155保证在100Ω负载下,典型输出电流为3.6mA。使用100Ω端接电阻(3.6mA×100Ω = 360mV)时,MAX9155产生的输出电压为360mV。有关典型输出电平与负载关系,参见“差分输出电压与负载电阻典型工作曲线”。

-

探索MAX9155:低抖动、低噪声LVDS中继器的卓越性能2026-02-09 518

-

MAX9169/MAX9170 4端口LVDS和LVTTL至LVDS转发器技术手册2025-05-19 1750

-

MAX9180 400Mbps、低抖动、低噪声LVDS转发器,SC70封装技术手册2025-04-16 1056

-

SC70/SOT-323封装的10mALDO线性稳压器TPS797xx数据表2024-03-29 544

-

超低功率SC70/SOT-323封装10毫安LDOLINER稳压器数据表2024-02-28 720

-

LTC5508:300 MHz至7 GHz射频功率检测器,具有SC70封装数据表中的缓冲输出2021-05-20 800

-

采用微型SC70封装的DN315白光LED驱动器提供高效率和均匀的LED亮度2021-05-08 1144

-

LT1937: 采用 SC70 和 ThinSOT 封装的白光 LED 升压型变换器 数据手册2021-03-22 868

-

AN-734: 通用精密运算放大器评估板,采用SC70封装2021-03-21 881

-

SC70-6封装2020-04-08 4292

-

Maxim推出满摆幅、低噪声运算放大器MAX9636–MAX96382010-07-09 1643

-

空间转发器系统,空间转发器系统是什么意思2010-04-03 2267

-

MAX3370, MAX3371 低电压电平转换器,SC702009-11-19 1929

全部0条评论

快来发表一下你的评论吧 !