MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉点开关技术手册

描述

概述

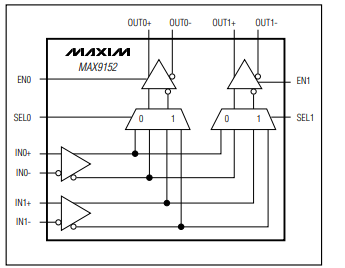

MAX9152 2 x 2交叉点开关专为需要高速、低功耗和低噪声信号分配的应用而设计。该器件包括两路LVDS/LVPECL输入、两路LVDS输出和两路用于设置差分输入和输出之间内部连接的逻辑输入。

MAX9152可编程为将任何输入连接至任一输出或两路输出,使其可采用以下配置:2 5 2交叉点开关、2:1多路复用器、1:2解复用器、1:2分路或双中继器。这种灵活性使MAX9152非常适用于容错系统中的保护开关、诊断用的环回开关、用于时钟/数据分配的扇出缓冲以及用于远距离通信的信号再生。

数据表:*附件:MAX9152 800Mbps、LVDS LVPECL至LVDS、2 x 2交叉点开关技术手册.pdf

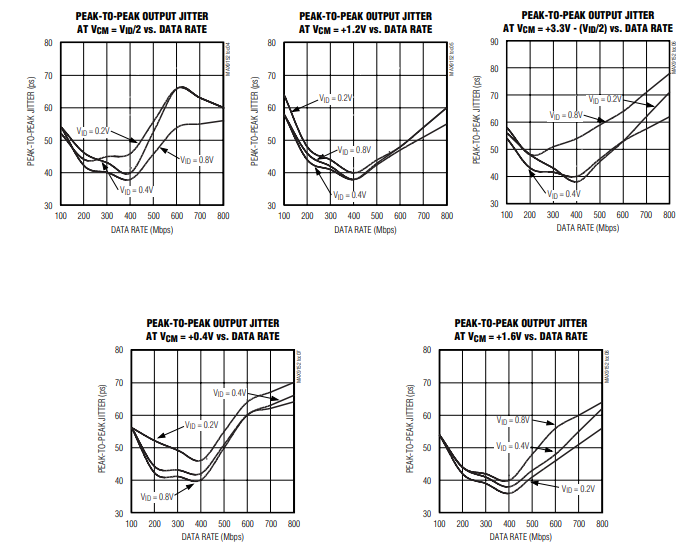

120psPK-PK(最大值)超低PRBS抖动可确保在对时序误差高度敏感的高速链路中实现可靠通信,尤其是那些包含时钟和数据恢复或串行器和解串器的链路。高速开关性能支持800Mbps的数据速率和小于50ps(最大值)的通道间偏斜。

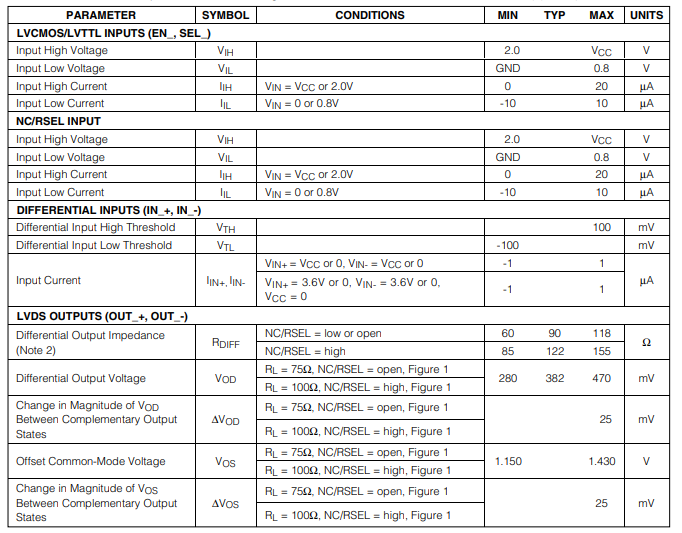

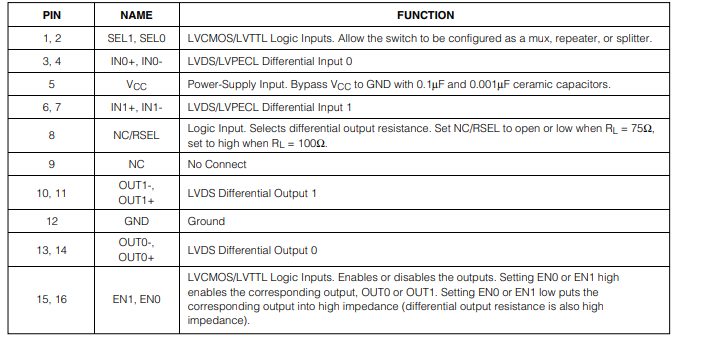

LVDS输入和输出符合TIA/EIA-644 LVDS标准。LVDS输入也可直接接受LVPECL信号,以及通过衰减网络接受PECL信号。LVDS输出可驱动75Ω或100Ω负载,并具有可选择的差分输出电阻以尽可能地减少反射。

MAX9152采用16引脚TSSOP和SO封装,在-40°C至+85°C温度范围内采用+3.3V单电源供电时功耗仅为109mW。

特性

- 引脚可编程配置

- 2 x 2交叉点开关

- 2:1多路复用

- 1:2解复用器

- 1:2分路器

- 双中继器

- 120ps

PK-PK(最大值)超低抖动,800Mbps,PRBS = 2^23^ -1 数据模式 - 低通道间偏斜:50ps(最大值)

- 109mW功耗

- 符合ANSI TIA/EIA-644 LVDS标准

- 输入接受LVDS/LVPECL信号

- LVDS输出额定用于75Ω和100Ω负载

- 引脚可编程差分输出电阻

- DS90CP22的引脚兼容升级版(SO封装)

- 采用16引脚TSSOP封装(SO尺寸的一半)

框图

DC电气特性

典型操作特性

引脚配置描述

详细说明

LVDS接口标准是一种信令方法,旨在通过受控阻抗介质进行点对点通信,符合ANSI TIA/EIA - 644和IEEE 1596.3标准。LVDS使用比其他常见通信标准更低的电压摆幅,在降低功耗的同时实现高速数据速率,并减少电磁干扰(EMI),提高系统抗扰度。

MAX9152是一款800Mbps的2×2交叉点开关,专为高速、低功耗的点对点和多点接口而设计。该器件可接受LVDS和差分LVPECL信号,并根据所选模式将其路由至输出端。

幅度在0.1V至VCC之间、单端电压在MAX9152的VCC和地之间的差分输入会切换输出。需要幅度至少为0.15V且单端电压在MAX9152的VCC和地之间的差分输入,才能满足交流规格。

在1:2分路器模式下,输出会重复所选输入。这在分配信号或创建备份副本(用于保护切换,如在转发器中)时很有用。

在双通道缓冲器模式下,器件会恢复信号幅度,允许隔离介质段或延长介质传输距离。该器件是一个交叉点开关,任何输入都可以连接到任何一个或多个输出。在2:1最大模式下,可以选择主信号和备份信号,以提供故障切换、容错应用。

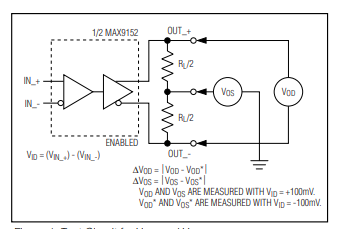

图1. VOD和VOS测试电路

(图中展示了相关测试电路的连接和参数测量方式 )

-

探索DS90CP22:800 Mbps 2x2 LVDS交叉点开关的卓越性能与应用2025-12-31 1566

-

SN65LVCP22:高速2x2 LVDS交叉点开关的卓越之选2025-12-30 460

-

探索DS10CP152:1.5 Gbps 2x2 LVDS交叉点开关的卓越性能2025-12-26 469

-

探索DS10CP152Q:汽车级1.5 Gbps 2x2 LVDS交叉点开关2025-12-25 398

-

MAX9392任意逻辑至LVDS、双路、2 x 2交叉点开关技术手册2025-04-15 1793

-

DS10CP152 1.5Gbps 2X2 LVDS交叉点开关数据表2024-07-09 334

-

DS90CP22 800 Mbps 2x2 LVDS交叉点开关数据表2024-07-05 408

-

DS25CP152 3.125Gbps LVDS 2x2交叉点开关数据表2024-07-03 477

-

2x2 LVDS交叉点开关SN65LVCP22数据表2024-06-26 392

-

美国国家半导体两款低功率LVDS 2x2交叉点开关电路2018-08-27 1358

全部0条评论

快来发表一下你的评论吧 !