地线干扰的形式分类及信号接地方式

电源/新能源

描述

在大多数电子系统中,降噪是一个重要设计问题。与功耗限制、环境温度变化、尺寸限制以及速度和精度要求一样,必须处理好无所不在的噪声因素,才能使最终设计获得成功。

这里,我们不考虑用于降低“外部噪声”(与信号一起到达系统)的技术,因为其存在一般不受设计工程师直接控制。相比之下,防止“内部噪声”(电路或系统内部产生或耦合的噪声)扰乱信号则是设计工程师的直接责任。今天我们就说说“接地”,而且是针对高频工作的“接地"

“接地”(Grounding)一般指将电路、设备或系统连接到一个作为参考电位点或参考电位面的良好导体上,为电路或系统与“地”之间建立一个低阻抗的通道。

地线是作为电路或系统电位基准点的等电位体,是系统中各个电路的公共导体,任何电路的电流都会经过地线形成回路。然而,任何导体都存在着一定的阻抗,当地线中有电流通过时,根据欧姆定律,地线上就会有电压存在,那么地线就不是一个等电位体。所以在实际设计电路或系统时,关于地线上各点的电位一定相等的假设就不是成立的,实际的情况是底线上各点存在电位差,有的相位差还可能很大。地线的公共阻抗会使各接地点间形成一定的电压,从而就会产生接地干扰。

如上面所说,地线作为导体,存在一定的阻抗,顾名思义,阻抗也就是由电阻和感抗两部分组成,即:

导体的阻抗是频率的函数,随着频率的升高,阻抗增加很快。对于高速数字电路而言,电路的时钟频率是很高的,脉冲信号包涵丰富的高频成分,因此会在地线上产生较大的电压,则地线阻抗对数字电路的干扰十分可观。

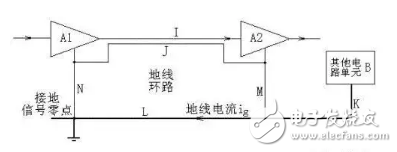

在电子产品的PCB设计中,抑制或防止地线干扰是需要考虑的最主要问题之一。所谓干扰,必然是发生在不同的单元电路、部件或系统之间,而地线干扰是指通过公用地线的方式产生的信号干扰。注意这里所提到的信号,通常是指交流信号或者跳变信号。地线干扰的形式很多,有人把它归结成两类:地线环路干扰、公共阻抗干扰,其实应该还要加上地线环路的电磁耦合干扰,因此是三类。下图可以很好的说明三类地线干扰的成因。

一、地环路干扰。横向,每根导线上的电流不同,因此会产生差模电压,对电路造成影响。具体的说就是“其他电路单元B”的地线电流,在J、N、L、M形成的“地线环路”中,对放大器A1和A2造成了影响。由于这种干扰是由电缆与地线构成的环路电流产生的,因此成为地环路干扰。

二、地环路电磁耦合干扰。在实际电路的PCB上,J、N、L、M形成的“地线环路”将包围一定的面积,根据电磁感应定律,如果这个环路所包围的面积中有变化的磁场存在,就会在环路中产生感生电流,形成干扰。空间磁场的变化无处不在,于是包围的面积越大干扰就越严重。

三、公共阻抗干扰。认真考察上图所示的电路结构,我们将发现,J、N、L、M中,有一条连接是多余的,随便去除其一,仍然可以满足各个接地点的连通关系,同时又可以消除地线环路。那么,将哪一条连线去除比较合理呢?这时就要考虑另一类的干扰问题——公共阻抗干扰。

①去除J:这是最差的方案。J去除后地线环路似乎消失了,可是另一个更可怕的环路又形成了(I、N、L、M),其中I是信号线,因此干扰比原来有线J时还要严重。

②去除M:环路消失,但是我们发现,此时放大器A2的地线电流需要流过J、N到达接地零点,注意N段是A1和A2共同的接地线,因此A2接地电流在N上形成的电压降就加到了A1上,形成干扰。这种因共用一段地线而形成的干扰称为“公共阻抗干扰”。

③去除L:不仅不能解决A2与A1之间的公共阻抗干扰问题,还引起了“B单元电路”与A1、A2之间的公共阻抗干扰问题。

④去除N:看来这是最后的方法。其实这样做将使M成为A1、A2的“公用阻抗”,同样形成干扰。还是存在问题!但是,我们注意到,此法中的干扰是A1对A2的干扰,A2是后级,工作信号强度远大于A1,因此A1对A2的干扰,很难造成不良后果。

最合理的走线方案是:去除N,然后将M的下端直接连到“接地信号零点”上。

以上是关于接地干扰产生的原因,下面再介绍的几种常见的接地方式,结合前面对接地干扰产生原因的了解,有助于我们在实际设计PCB板电路时,正确的选择干扰最小的接地方式,设计出合理的电路或系统。

信号接地方式可以大体上分为:单点接地、多点接地、混合接地和悬浮接地。

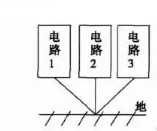

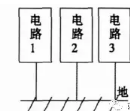

一、单点接地。单点接地就是把真个电路系统中的某一点作为接地的基准点,所有电路及设备的地线都必须接到这一点上,并以该点作为电路、设备的零电位参考点。单点接地又分为串联单点接地和并联单点接地。如下图所示:

图2.串联单点接地

对于串联式单点接地方式,如果该电路的功率很大,会产生很大的电路回流,在有限阻抗上会产生一个电压降,造成电路和基准地之间的电压参考值的差异可能使系统不能如预期的那样工作。如存在多种不同功率等级的电路,不能采用串联式单点接地方式,因为大功率电路产生大的回地电流,将影响低功率器件和电路。如果说一定要采取这种接地方法,那么最敏感的电路必须直接设置在电源输入位置处,并且尽量远离低功率器件和电路。串联单点接地方式和结构都比较简单,如果各个电路的接地引线比较短,其阻抗也会相对小。如果各个电路的接地电平差别不大,可以采用这种接地方式。

并联单点接地方式中,每个电路单元独用地线连接到同意地点,其优点是各电路的地点为只与本电路的地电流及地线阻抗有关,不受其他电路的影响。低频时可有效的避免各电路单元之间的低阻抗干扰,但是也存在很多缺点。主要表现在:首先,各个电路分别采用独立地线接地,需要多跟地线,势必增加地线长度,从而增加地阻抗,结构复杂使用麻烦;其次,这种接地方式会造成各地线互相间的耦合,并且随着频率增加,地线阻抗、地线电感、电线电容都会增大,这种接地方式不适用高频电路。

二、多点接地。多点接地是指某一个系统中各个需要接地的电路、设备都直接接到距离它最近的接地平面上,一边接地长度最短,接地阻抗减到最小。

当电子系统的工作频率高于1MHz时,以致工作波长与系统接地引线的长度可比拟时,地线就象一根终端短路的传输线,地线的电流、电压呈驻波分布,地线变成了辐射天线,而不能起到地线的作用。为了减少接地阻抗,避免辐射,地线的长度应小于1/20波长,因而单点接地方法是不合理的,通常采用多点接地技术。多点接地电路结构简单,接地线上可能出现的高频驻波现象显著减少,但多点接地可能会导致设备内部形成许多接地环路,容易对设备内部的敏感店里产生地环路干扰。

-

信号调理设备的接地方式有哪些?2025-11-14 3427

-

电子电路设计中常用的接地方式详解2025-04-17 1568

-

不同的接地方式,浪涌保护器怎么选型2024-02-21 1660

-

什么是GND接地?GND地线的分类2024-02-03 7118

-

电力系统中性点接地方式分类2023-10-12 4792

-

电路板接地的作用及常见接地方式2023-05-18 1615

-

中性点接地电阻接地方式的分类2022-08-11 5878

-

PLC的接地属于低压电器设备的单点接地方式2022-07-25 2190

-

PCB中为了防止共阻抗干扰的地线设计方案浅析2019-06-03 1992

-

PCB设计的接地干扰消除2018-09-10 2295

-

简述关于PLC的正确接地方式2016-12-20 2782

-

接地方式的分类2009-10-03 3115

-

地线干扰与接地技术2009-04-23 1272

全部0条评论

快来发表一下你的评论吧 !