浮思特 | CMOS技术原理与应用:从晶体管结构到反相器设计

描述

MOSFET在数字电路中的常见形式是互补MOS(CMOS)电路。CMOS技术将n沟道和p沟道MOSFET成对集成在同一芯片上,成为数字集成电路的主导技术,相比单独使用NMOS和PMOS晶体管具有诸多优势。

发展互补MOSFET(CMOS)技术的主要动机是实现数字电路逻辑门的高速运行与低功耗。CMOS技术支持构建多种高性能模拟和数字电路,其工作原理与BJT逻辑器件类似,但通过电压而非电流触发——CMOS栅极不存在电流输入。

1970年代CMOS技术仅应用于电子表等特定消费领域。但到1980年代,凭借低功耗、高噪声容限、更宽的工作温度/电压范围、电路简化、抗电迁移、高可靠性及版图设计便捷等优势,VLSI技术开始转向CMOS。80年代VLSI的发展使单芯片集成度达到数百万晶体管。目前CMOS已成为VLSI数字和混合信号设计的主流技术,相比晶体管-晶体管逻辑(TTL),CMOS速度更快、更适应低电源电压工作且功耗更低。

下文将阐述n型与p型互补晶体管对如何构成CMOS模块基础。

反相器介绍

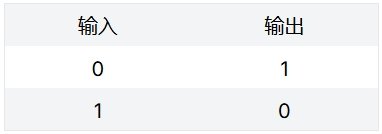

反相器是实现信号反转的逻辑元件。数字电路中,二进制算术和开关函数的数学运算最佳采用0(低电平)和1(高电平)表示。当逻辑电平定义为0V(地)和V伏时,反相器使0V输入产生V伏输出,反之亦然。

除文字描述外,真值表可系统呈现所有可能输入组合及其对应输出。表1即为反相器真值表。

表1

表1

NMOS反相器

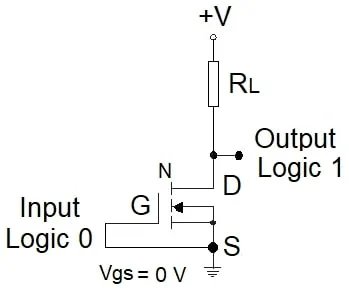

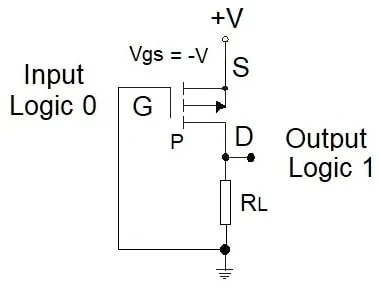

常规用法以栅极为输入、漏极为输出,源极与衬底接地。图1显示增强型n沟道MOS(NMOS)在输入接地时的符号与连接。正电压+V通过负载电阻(RL)为漏极供电形成偏置。负载电阻产生Id∙RL压降(Id为漏极电流),衬底、源极和栅极均接地。

图1

图1

输入接地时,栅电容电压为零(逻辑0),电容保持放电状态,晶体管无导电沟道形成,呈现高阻开路特性,漏源电流Id极低。因负载电阻压降可忽略,输出为正电压+V(逻辑1)。故输入逻辑0时晶体管截止,输出近似电源电压(逻辑1)。

当栅极施加正电压时,电子被吸引至栅极氧化层。当电荷积累足够时,硅表面转变为n型材料,形成连接n型源漏区的低阻n沟道,使漏极电流Id从漏极流向源极。栅极正电压使晶体管开启(阈值电压VT),表现为闭合开关。此时n沟道电阻远小于负载电阻,输出近似接地(逻辑0)。

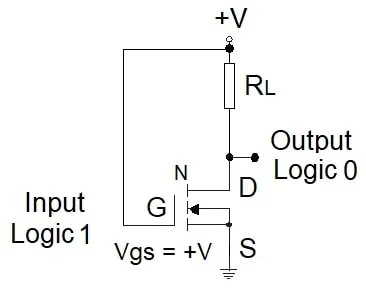

图2

图2

综上,输入逻辑0时输出近V伏(逻辑1),输入逻辑1时输出接地(逻辑0),实现反相功能。"增强型"得名于晶体管常态开路、导通需激活的特性。需注意:栅极连接电容使直流输入始终开路,仅电容充放电时存在输入电流。

NMOS反相器的缺陷在于晶体管导通时存在电源到地的持续电流,这在复杂电路中会导致显著功耗增加。

PMOS反相器

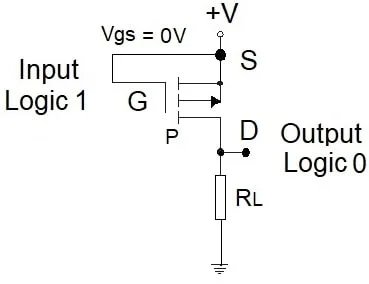

PMOS晶体管以互补方式工作,其反相器连接与NMOS相反。图3展示输入接+V(逻辑1)时PMOS反相器的符号与连接,衬底和源极接+V,负载电阻接地。

图3

图3

+V输入(Vgs=0V)不充电栅电容,晶体管保持截止,其高阻使输出接地(逻辑0)。接地输入(Vgs=-V)使栅电容充电,电容另一侧的正电荷将n型硅表面转为p型材料,形成源漏间低阻p沟道,晶体管开启,Id从源极流向漏极。此时导通电阻远小于负载电阻,输出近+V(逻辑1)。与NMOS相同,输入逻辑0输出逻辑1,反之亦然。

图4

图4

CMOS剖面结构

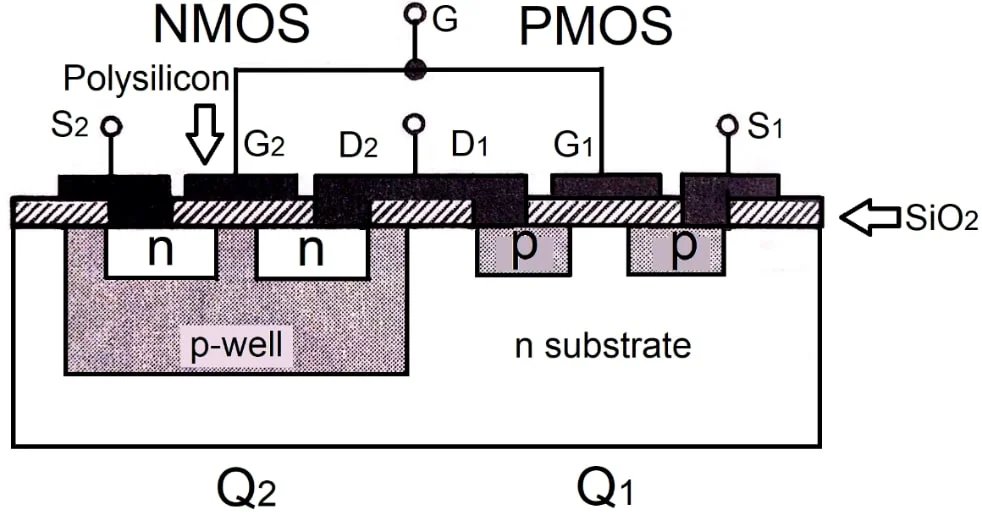

CMOS制造于兼具电气参考和机械支撑的衬底上。剖面图沿晶体管中部切割晶圆呈现侧视图。图5为CMOS栅极的简易剖面,NMOS和PMOS集成在同一芯片:p沟道器件右侧形成p沟道,n沟道器件左侧形成n沟道。

图5

图5

此结构中,PMOS直接制作于n型衬底(体区),NMOS制作于p型区域(p阱)。阱是低掺杂深扩散区,既作为器件衬底又提供隔离。也可采用p型衬底配合n阱工艺。n型体区与p阱的连接方式未具体说明。

CMOS反相器

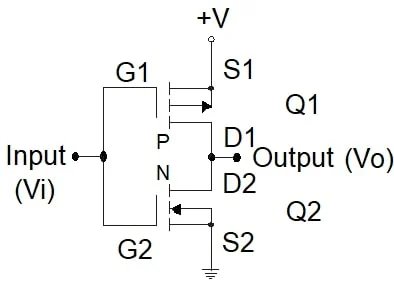

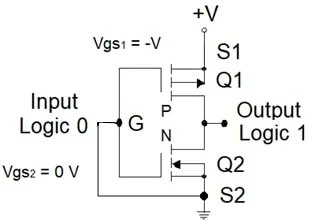

CMOS反相器结构简洁(图6),将功耗降至最低。它由增强型NMOS和PMOS串联构成,各晶体管互为对方的负载电阻。栅极并联为输入端,漏极连接处为输出端。PMOS(Q1)衬底和源极接+V,NMOS(Q2)对应端接地。

图6

图6

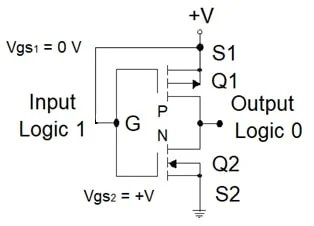

输入+V(逻辑1)时,Q2的Vgs=+V导通(漏源电阻极小),Q1的Vgs=0V截止(漏源电阻极大),根据分压规则输出近0V(逻辑0)(图7)。输入接地时,Q2截止,Q1的Vgs=-V导通,此时Q1低阻、Q2高阻,输出近+V(逻辑1)(图8)。NMOS作为下拉管将输出拉至地,PMOS作为上拉管将输出拉至+V。

图7

图7

图8

图8

CMOS反相器功耗

CMOS电路直流输入电流可忽略。因截止晶体管将漏电流限制为泄漏值,两种状态的功耗均极低,仅输入切换时出现显著功耗。虽然CMOS平均功耗低,但其值取决于电路活动性:静态电路功耗极小,此特性使CMOS总体比TTL更高效;但高频状态切换时功耗可能接近TTL水平。

CMOS反相器直流电压传输特性

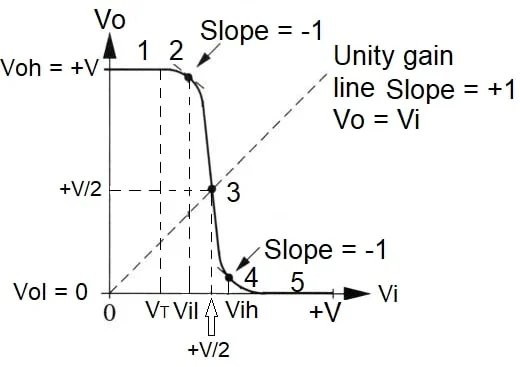

直流电压传输特性(VTC)可量化反相器工作状态,即输出电压(Vo)随输入电压(Vi)的变化曲线。CMOS反相器的VTC近乎理想,图9展示Q1/Q2匹配时的VTC曲线。

图9

图9

匹配晶体管使VTC对称且上下拉电流驱动能力相等。CMOS反相器的重要特性是高输出电压摆幅。如图9所示,根据Q1/Q2工作模式,VTC分为五段:

Q2截止

Q2饱和/Q1线性

Q1/Q2均饱和

Q1饱和/Q2线性

Q1截止

该曲线将逻辑0/1定义为电压范围,且输入/输出的逻辑电平阈值不同。关键参数包括输入高低电平Vih/Vil、输出高低电平Voh/Vol及阈值电压VT。Vih/Vil对应VTC斜率dVo/dVi=-1的点:Vi>Vil时增益增加进入转换区;Vi

数字设计追求窄转换区,而模拟设计则关注该区域。

CMOS技术回顾

互补MOS(CMOS)在数字电路中无处不在,成为复杂数字IC的首选技术。"互补"指同一芯片上配对的增强型NMOS和PMOS:导通晶体管漏源电阻极低,截止时极高。

CMOS反相器采用串联的NMOS和PMOS,PMOS接+V,NMOS接地。输入逻辑0时NMOS截止/PMOS导通,输出上拉至逻辑1;输入逻辑1时NMOS导通/PMOS截止,输出下拉至逻辑0。与其他FET器件相同,CMOS输入栅极绝缘,故输入电流极小。CMOS仅在状态切换时产生显著功耗,这一无静态功耗的特性使其自诞生起就大获成功。

-

晶体管反相器的原理及应用2024-10-08 4320

-

TTL反相器和CMOS反相器的区别2024-07-29 5768

-

影响CMOS反相器特性的因素2024-01-26 3904

-

晶体管反相器原理2023-11-20 731

-

CMOS反相器的电路结构和工作原理2023-10-31 9082

-

如果把cmos反相器中的nmos和pmos颠倒连接,电路能否工作?为什么?2023-09-12 4169

-

CMOS反相器的电路结构是怎样的?它有哪些特点?2023-04-25 1526

-

CMOS反相器构建Big Muff2022-06-30 2238

-

MOS反相器和CMOS反相器的详细资料说明2020-03-20 3707

-

cmos反相器的输出特性2018-08-16 25727

-

cmos反相器设计电路图2018-03-27 85973

-

详细讲解cmos反相器的原理及特点2017-11-30 92642

-

晶体管反相器原理及电路图2010-03-29 7214

-

CMOS晶体管,CMOS晶体管是什么意思2010-03-05 4107

全部0条评论

快来发表一下你的评论吧 !