ADF5002 4GHz至18GHz 8分频预分频器技术手册

描述

概述

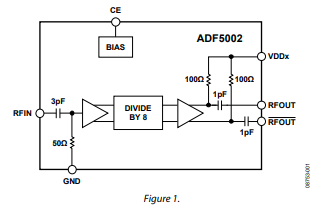

ADF5002预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18GHz的频率分频至适合输入到 [ADF4156]或[ADF4106]等PLL IC的较低频率。ADF5002提供8分频功能,采用3.3V电源供电,具有差分100Ω RF输出,可以直接与ADF4156和ADF4106等PLL的差分RF输入接口。

数据表:*附件:ADF5002 4GHz至18GHz 8分频预分频器技术手册.pdf

应用

- PLL 频率范围扩展器

- 点对点无线电

- VSAT无线电

- 通信测试设备

特性

- 8分频预分频器

- 高工作频率:4GHz至18GHz

- 集成RF去耦电容

- 低功耗

主动模式: 30 mA省电模式: 7 mA - 低相位噪声:−150dBc/Hz

- 单直流电源:3.3V,兼容ADF4xxxPLL

- 温度范围:−40°C至+105°C

- 小型封装:3mm×3mmLFCSP

框图

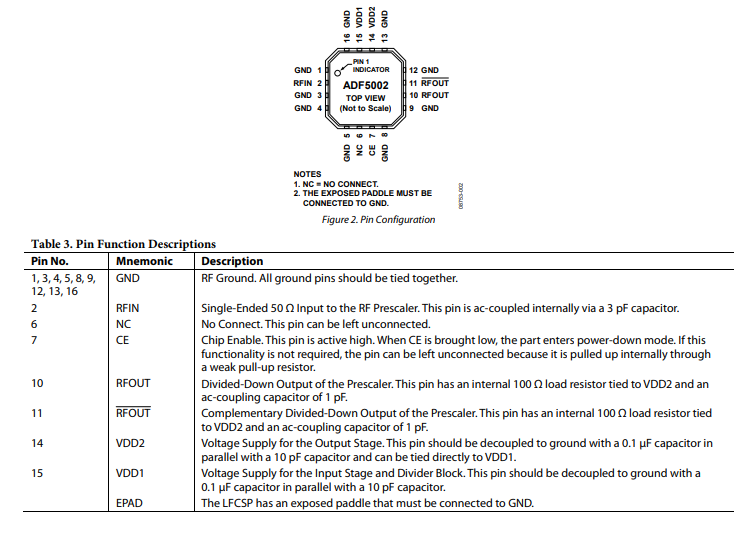

引脚配置描述

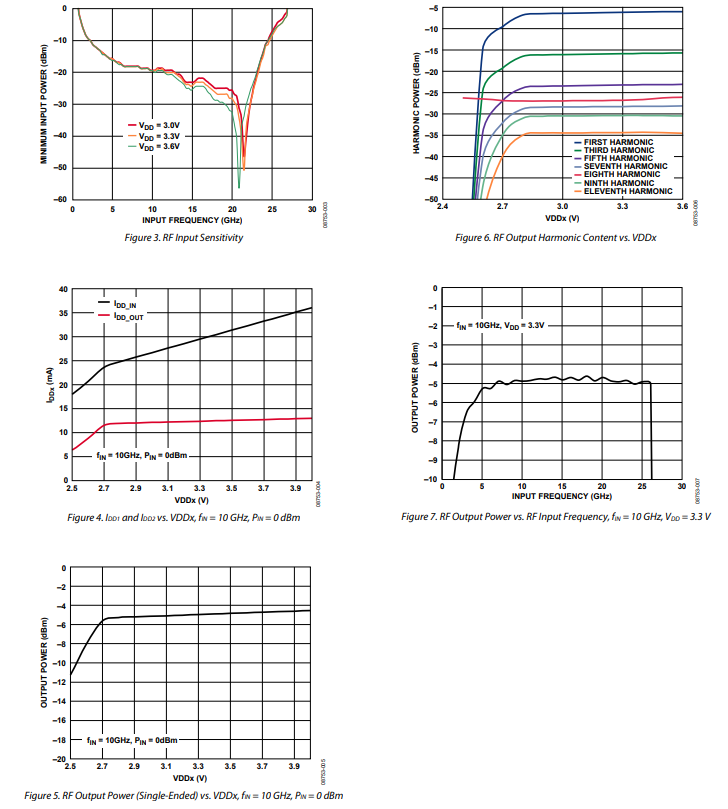

典型性能特征

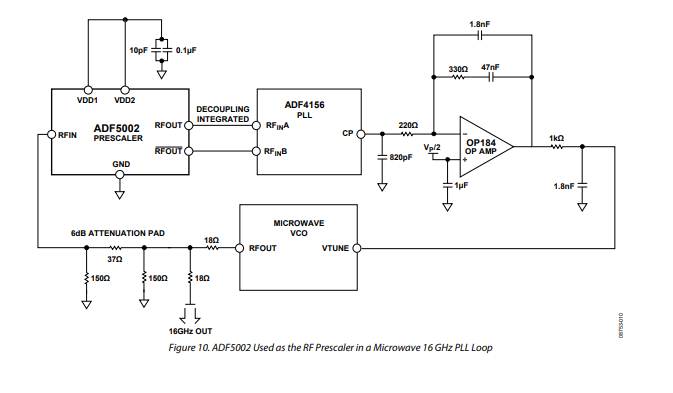

应用电路

ADF5002可以单端或差分方式连接到亚德诺半导体(Analog Devices)锁相环(PLL)系列的任意一款芯片。为实现最佳性能并达到最大功率传输,建议采用差分连接方式。图10所示的应用电路展示了ADF5002的情况。ADF5002用作射频预分频器,接入微波16 GHz锁相环(PLL)。ADF5002将16 GHz射频信号分频至2 GHz,随后以差分方式输入到ADF4156锁相环中。采用由OP184运算放大器构成的有源滤波器拓扑结构,为微波压控振荡器(VCO)提供所需的宽范围调谐电压。

OP184的正输入引脚偏置为ADF4156电荷泵电源(Vₑ)电压的一半。这可通过简单的电阻分压器轻松实现,同时要确保在OP184的+IN引脚附近进行充分去耦。这样的配置使得能够使用单个正电源为运算放大器供电。或者,为优化性能,可通过确保干净的偏置电压,使用低噪声调节器(如ADP150 ),为电阻分压器网络供电,或直接为+IN引脚供电。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADF5000 4GHz 至18GHz 2分频预分频器技术手册2025-04-16 1607

-

宽带放大器和预分频器模块覆盖直流至20 GHz2021-05-26 819

-

HMC434:0.2 GHz至8 GHz,GaAs,HBT MMIC,除以8个预分频器数据表2021-05-16 752

-

ADF5001:4 GHz至18 GHz除以4预分频器数据表2021-04-28 733

-

ADF5000:4 GHz至18 GHz除以2预分频器数据表2021-04-27 755

-

ADF5002:4 GHz至18 GHz除以8个预分频器数据表2021-04-22 892

-

4GHz至18GHz的ADF5001预分频器2020-09-25 1346

-

ADF5001预分频器是一个低噪声/低功率/固定射频分频器块2020-07-13 1921

-

ADF5000 4GHz 至18GHz 2分频预分频器2019-02-22 395

-

4千兆赫至18千兆赫八分频分频器ADF5002数据表2017-10-20 1115

-

ADI公司推出低功耗射频预分频器-- ADF500x2010-05-11 2094

全部0条评论

快来发表一下你的评论吧 !