基于RV1126开发板的MIPI-CSI硬件电路设计

电子说

1.4w人已加入

描述

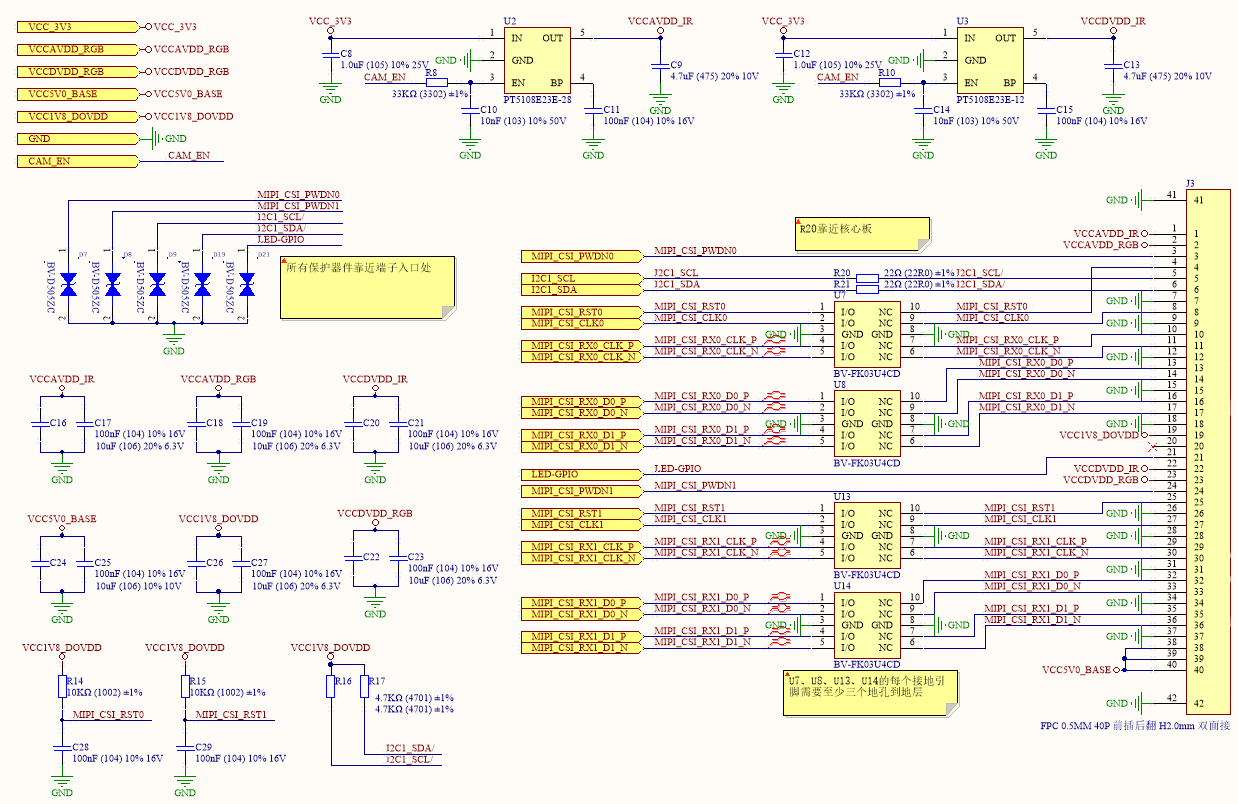

核心板引出了2路MIPI CSI信号,兼容MIPI组织接口标准V1.2。每一路具有4对数据差分信号和1对时钟差分信号。4路数据差分通道,每个通道最大支持2.0Gbps的速率,即最大支持8.0Gbps的速率,通过换算可同时支持4路1080p摄像头的数据输入。

在EASY EAI nano-T评估底板上面,将2路MIPI CSI信号引到了同一个FPC座子上面,不过每一路MIPI CSI只引出2对数据差分信号,外接200万像素MIPI双目摄像头。接口上面有I2C信号,用于配置双目摄像头。

PCB布局建议:

1.所有的ESD保护器件都要靠近FPC端子。

2.U7、U8、U13、U14这几个保护器件的每个接地引脚需要至少三个地孔到地层。

3.MIPI_CSI_RST0和MIPI_CSI_RST1复位信号是敏感信号,所以走线要尽量短,并且走线需做包地处理,避免干扰影响摄像头稳定性。

4.电阻R20靠近核心板。

5.MIPI CSI差分对需要控制PCB阻抗,差分阻抗为100Ω ±10%。

6.MIPI_CSI_CLK0和MIPI_CSI_CLK1单独走线并做包地处理,包地线每隔500mil至少添加一个GND过孔。

7.MIPI CSI差分对整组并行走线并包地,与GND信号间距遵循3W原则,并且包地线每隔300mil至少添加一个GND过孔。

8.差分信号组内2线长度差异小于24mil,数据差分线与时钟差分线之间的差异小于42mil。差分线最大长度小于150mm。线距遵循3W原则。

9.当差分信号走线需要换层时,确保走线上的过孔数量少于6个,并靠近信号过孔放置对称的地缝合孔。

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

替代升级实锤!实测RV1126B,CPU性能吊打RV11262025-12-11 2541

-

RV1126系列选型指南:从RV1126到RV1126B,一文看懂升级差异2025-09-04 5151

-

基于RV1126开发板实现人脸检测方案2025-04-21 99

-

基于RV1126开发板实现驾驶员行为检测方案2025-04-18 354

-

基于RV1126开发板的音频硬件电路设计2025-04-17 1420

-

基于RV1126开发板的以太网硬件电路设计2025-04-16 1025

-

基于RV1126开发板网络配置方法2025-04-15 1072

-

RV1126 实现人脸检测方案2025-04-14 1043

-

RV1126开发板数据手册2022-08-28 2336

-

RV1109/RV1126平台使用connman进行WiFi管理的操作方法2022-07-18 6402

-

科普一下RV1109/RV1126平台各种外设使用的方法2022-07-14 6545

-

分享一份有关TB-RV1126Ds开发板硬件的规格书2022-06-16 4852

全部0条评论

快来发表一下你的评论吧 !