浮思特 | NoC架构如何解决MCU设计挑战

描述

微控制器(MCU)经历了显著的变革,从基本的控制器发展为能够处理日益复杂任务的专用处理单元。它们曾经仅限于简单的命令执行,现在支持快速决策、高度安全性和低功耗操作等多种功能。

MCU的角色已经扩展到各个行业,从管理工业自动化中的复杂控制系统到支持安全关键的车辆应用以及在联网设备中实现高效能运作。

随着MCU承担的工作负载不断增加,传统的基于总线的互连方式已经无法满足性能和可扩展性的需求。引入人工智能(AI)加速器、机器学习技术、可重构逻辑和安全处理单元,需要更先进的片上通信基础设施。

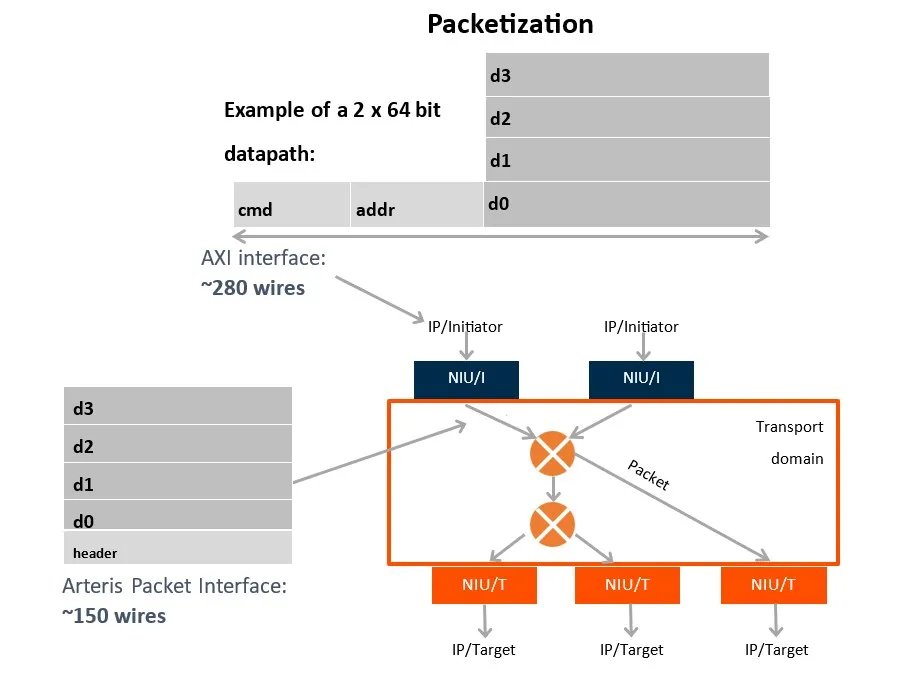

为了满足这些需求,设计师们开始采用网络芯片(NoC)架构,这种架构提供了一种结构化的数据传输方式,缓解拥堵并优化功率效率。与传统的交叉开关互连相比,NoC通过数据包化和串行化减少了路由拥堵,使数据流更加高效,同时减少了线路数量。

网络-on-chip (NoC) 通信中高效数据包化的工作原理

网络-on-chip (NoC) 通信中高效数据包化的工作原理

MCU厂商拥抱NoC互连技术

多年来,许多MCU厂商依赖专有互连解决方案,从基础交叉开关演进到定制化NoC实现。但随着AI/ML集成、安全需求和实时处理带来的设计复杂度提升,这些方案的维护成本和技术难度急剧增加。

此外,先进封装技术和芯片间互连的普及,使得自主维护互连架构的复杂度持续攀升——需要不断适配新的通信协议和电源管理策略。

为应对这些挑战,众多厂商正转向商用NoC解决方案。这些经过预验证的方案不仅提供可扩展性,更能显著降低开发成本。对设计AI驱动型MCU的工程师而言,NoC在加速器与存储器间建立的高效通信通道将极大影响系统效能。

这一转型的另一重要驱动力是能效优化。与通用SoC不同,多数MCU需在严格功耗限制下运行。先进NoC架构通过电源域划分、时钟门控及动态电压频率调节(DVFS)实现细粒度功耗控制,在保持实时处理能力的同时优化能耗。

NoC架构的性能优化之道

异构处理单元数量的激增对互连架构提出了空前要求。NoC技术通过可扩展的高性能方案应对这些挑战:缓解布线拥塞、优化功耗并增强数据流管理。其高效的数据包通信机制能减少布线数量,简化与各类处理核心的集成,完美契合现代MCU需求。

通过结构化数据传输,NoC消除了互连瓶颈,既提升响应速度又缩减芯片面积。基于NoC的设计可实现比传统总线架构高出30%的带宽效率,显著增强实时系统性能。这使得MCU设计者既能获得更高带宽效率,又能简化集成流程,确保其架构在汽车、工业和企业计算市场保持适应性。

除提升互连效率外,NoC架构支持网状、树状等多种拓扑结构,保障跨专用处理核心的低延迟通信。其可扩展设计在优化互连密度的同时减少拥塞,使MCU能处理更复杂工作负载。NoC还通过模块化设计、动态带宽分配和串行化技术提升能效。

如图表所示,采用先进串行化技术的NoC架构可将互连线路减少近50%,在保持性能的同时降低芯片面积和功耗。这些特性使MCU能在功耗限制与芯片面积最小化之间取得平衡,因此NoC方案成为需要实时处理和高效数据流的新一代设计的关键。

在扩展性之外,NoC还通过支持ISO 26262和IEC 61508合规的安全特性增强系统可靠性。其提供的确定性通信、自动带宽/延迟调节及内置死锁避免机制,既减少人工配置需求,又确保安全关键应用中的数据流可靠性。

面向下一代MCU的互连方案

随着MCU工作负载复杂度提升,NoC架构已成为管理高带宽实时自动化和AI推理应用的关键。除提升数据传输效率外,NoC在电源管理、确定性通信及功能安全合规方面的优势,使其成为新一代MCU的核心组件。

为满足从AI加速到严苛功耗可靠性要求等集成需求,MCU厂商正转向能简化系统设计的商用NoC方案。自动化流水线、拥塞感知路由及可配置互连框架,现已成为降低设计复杂度、确保可扩展性和长期适应性的关键。

现代NoC架构在支持高带宽低延迟通信的同时,能优化时序收敛、最小化布线数量并缩减芯片面积。这种灵活性确保新一代架构能高效处理新兴工作负载,并适应不断演进的行业标准。

-

飞思卡尔MCU开发全攻略2014-02-13 26791

-

从SoC到NoC:芯片架构的演进与变革2023-05-11 15262

-

FPGA领域NoC硬件架构下的应用2024-03-22 1724

-

浮思特 | ABOV MCU如何塑造高端吸尘器的高效“内核”2025-11-11 794

-

浮思特 | 小家电主控怎么选?聊聊一颗实用型8位MCU:MC96F8208S2026-01-20 323

全部0条评论

快来发表一下你的评论吧 !