ADMV4640集成小数N分频PLL和VCO的Ku频段下变频器技术手册

描述

概述

ADMV4640是一款微波下变频器,针对各种卫星通信(SATCOM)用户终端进行了优化,RF工作频率范围为10.7 GHz至12.7 GHz。

ADMV4640本振(LO)信号可从内部通过片内整数N分频(INT)频率合成器产生。内部频率合成器的LO频率覆盖范围为8.7 GHz至10.7GHz。10.7 GHz至12.7 GHz范围内的输入RF信号会下变频为1.4 GHz至2.2 GHz的输出中频(IF)信号。芯片具有滤波特性以抑制6.7 GHz至8.7 GHz的镜像频段。片内低噪声放大器在混频器前集成了6 dB步进衰减器,使用户能够在较低噪声系数和较高线性度之间进行权衡。此外,该芯片还在IF输出端集成了数字步进衰减器,可提供高达31 dB的增益控制范围和1 dB步进,以便对后续电缆损耗进行调整。

数字串行外设接口(SPI)可对该器件轻松编程。除了数字SPI控制之外,模拟控制引脚(RX_MUTE)可快速关断所有电路,让接收器进入待机模式以便省电。模拟通用输入-输出(AGPIO)引脚可用作由片内模数转换器(ADC)读取的输入,或与绝对温度(PTAT)电压成正比的内部模拟输出。还提供三个数字GPIO引脚,用于输出逻辑电平以使用SPI控制外部器件。

ADMV4640下变频器采用紧凑的散热增强型、6 mm × 6 mm、40引脚引脚架构芯片级封装(LFCSP)。ADMV4640工作壳温范围为−40°C至+85°C。

数据表:*附件:ADMV4640集成小数N分频PLL和VCO的Ku频段下变频器技术手册.pdf

应用

- SATCOM用户终端

特性

- 集成PLL的X/Ku频段至IF下变频器

- RF输入频率范围:10.7 GHz至12.7 GHz

- 内部LO频率范围:8.7 GHz至10.7 GHz

- 噪声系数:5.2 dB、最小衰减、LNA低增益模式

- 匹配、50 Ω、单端RF输入和IF输出

- 片内温度传感器

- 片内ADC

- 接收器频率合成器锁定检测引脚

- 20 MHz时可通过四线式SPI接口编程

- 接收器待机功能

- 40引脚、6 mm × 6 mm LFCSP封装

框图

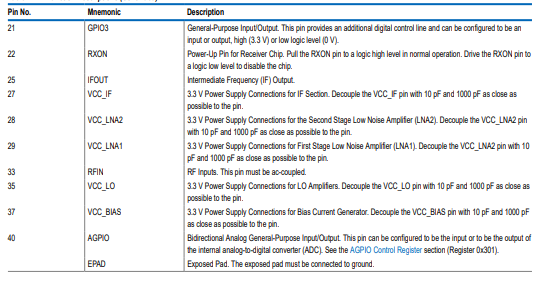

引脚配置描述

典型性能特征

工作原理

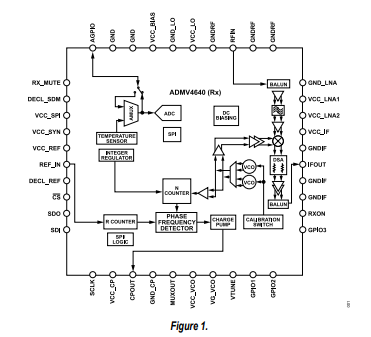

ADMV4640是一款针对工作在10.7 GHz至12.7 GHz频段的各类卫星通信(SATCOM)用户终端优化的微波下变频器。图1为该器件的功能框图。ADMV4640的数字设置通过SPI(串行外设接口)进行控制。

参考输入级

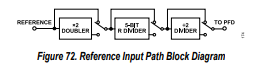

参考输入级如图72所示,可由外部单端25 MHz信号源驱动。需确保外部直流模块用于参考输入。

参考倍频器、R计数器和参考二分频器

内部有一个参考倍频2模块(×2倍频器,见图72),用于生成更高的鉴相频率(fpd)。通过设置寄存器0x20E的第3位(DOUBLER_EN位)使能参考倍频器。

有两个频率分频器:一个5比特R分频器(1至32可选,见图72)和一个二分频模块。这些分频器将输入参考频率(fref)降低,以产生更低的fpd。通过设置寄存器0x20C的第4 - 0位(R_DIV位)来设置R计数器。

通过设置寄存器0x20E的第0位(RDNV2_SEL位)使能参考二分频模块。

整数模式和N计数器

ADMV4640合成器工作在整数模式(INT模式)。

N计数器在锁相环(PLL)从压控振荡器(VCO)返回的反馈路径中设置分频比。分频比由INT位值决定。使用寄存器0x200和寄存器0x201来设置INT位值。

INT值与参考路径相结合,可生成间隔为fpd的VCO频率。

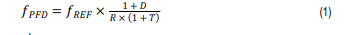

使用以下公式计算fpd,其中涉及fref和参考路径配置参数:

其中:

- D是参考倍频器位(0或1)。

- R是5比特二进制可编程计数器(1到31)的参考分频比。

- T是参考二分频比特(0或1)。

使用以下公式计算VCO频率(fVCO):

其中:

- fLO是驱动混频器的本振频率。

- N是INT的期望取值,INT是16比特整数值(0到65535)。

鉴相鉴频器(PFD)和电荷泵(CP)

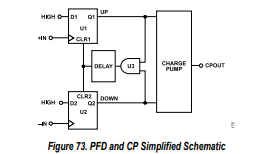

PFD接收来自R计数器和N计数器的输入,产生一个与两个计数器之间的相位和频率差成比例的输出。该比例信息输出到一个CP电路,产生电流以驱动外部环路滤波器,进而适当地增加或降低VTUNE调谐电压。

图73展示了PFD和CP的简化原理图。U1和U2是双D型触发器,U3是一个接地门。PFD包含一个固定延迟元件,用于确保PFD传递函数中不存在死区,从而保证参考杂散电平一致。

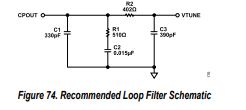

环路滤波器和电荷泵电流

为PLL定义环路滤波器取决于PFD频率、N计数器值、VCO的调谐灵敏度特性(kVCO)以及所选的CP电流。较低的fpd允许PLL在INT模式下工作,这可以消除整数边界杂散,但代价是带内相位噪声更高。

在频率规划和fpd选择时需谨慎,以确保带内相位噪声性能符合要求,同时杂散电平在最终应用可接受的范围内。

ADMV4640 - EVALZ评估板上实现的环路滤波器如图74所示。CP电流(ICP)由寄存器0x22E设置。推荐默认寄存器值0x0E。

-

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc2025-05-22 128

-

ADF4153A小数N分频频率合成器技术手册2025-04-25 1224

-

ADMV4630集成小数N分频PLL和VCO的Ku频段上变频器技术手册2025-04-18 1635

-

HMC1190ALP6NE集成小数N分频PLL和VCO的宽带高IP3双通道下变频器技术手册2025-03-28 1448

-

HMC1197集成小数N分频PLL和VCO的宽带直接正交调制器技术手册2025-03-01 1373

-

ADMV4530具有集成小数N分频PLL和VCO的双模式Ka频段上变频器技术手册2025-02-28 1429

-

ADRF6650:带DVGA和PLL/VCO的双下变频器,450 MHz至2700 MHz数据表2021-05-14 819

-

HMC1190ALP6NE:宽带High IP3双通道下变频器,带小数N PLL和VCO,0.7-3.8 GHz数据表2021-05-08 833

-

ADMV4420:集成小数N PLL和压控振荡器数据表的K波段下变频器2021-04-29 773

-

ADMV4530:带集成小数N PLL和压控振荡器的双模Ka波段上变频器数据表2021-04-24 908

-

ADMV4420 具有集成小数 N 分频 PLL 和 VCO 的 K 波段下变频器2019-02-22 626

-

用于无线应用的集成PLL和VCO2018-10-26 2445

全部0条评论

快来发表一下你的评论吧 !