ADA4355位接收器μModule的可编程跨阻抗和电流技术手册

描述

概述

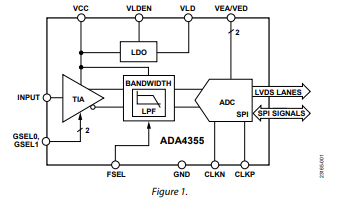

ADA4355 是一款完整的高性能电流输入 μModule ^®^ 。为了节省空间,ADA4355 包括所有必需的有源和无源元件,以实现完整的电流位数据采集解决方案,支持小型光学模块和多通道系统。

数据表:*附件:ADA4355位接收器μModule的可编程跨阻抗和电流技术手册.pdf

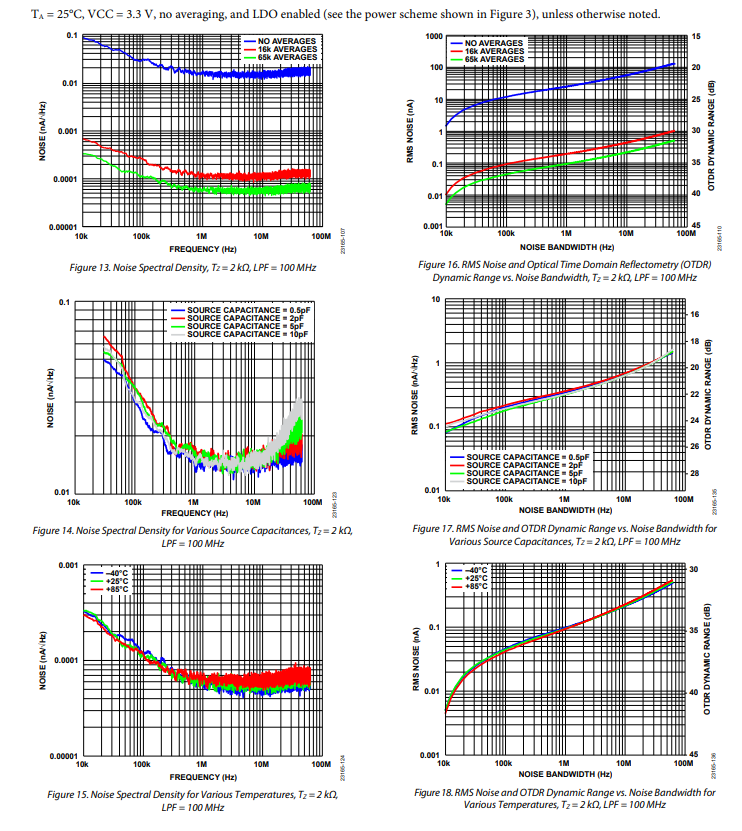

该套件的高速跨阻放大器(TIA)支持 10 ns 脉冲宽度,从而为飞行时间 (ToF) 的测量提供了高空间分辨率。此外,ADA4355 包含三个 TIA 增益 (T Z ) 设置,以较大限度地提高动态范围。内部可选模拟低通滤波器 (LPF) 可以将套件带宽限制在 100 MHz 的转折频率,以较大限度地降低宽带噪声,同时还可以作为 125 MSPS模数转换器的抗混叠滤波器。对于较低带宽的信号或较宽的信号脉冲(例如 20μs 或更宽),滤波器可以将截止频率设置为 1.0 MHz,进行额外降噪。

14 位 ADC 以高达 125 MSPS 的速率转换放大的电压信号,并通过两条串行低压差分信号 (LVDS) 数据通道输出数字化信号,每条通道的速率最高可达 1 Gbps。数据时钟输出 (DCO) 工作频率高达 500 MHz,支持双倍数据速率 (DDR) 操作。

ADA4355 从大输入电流信号中实现快速过驱恢复,采用 12.00 mm × 6.00 mm CSP_BGA 封装,工作温度范围为 40°C 至 +85°C。

应用

电流电压转换

化学分析仪

质谱分析

飞行时间

光纤检测

OTDR

光学放大器

可重新配置的光分插复用器(ROADM)

特性

高性能、电流输入、数据采集 μModule,括 TIA、模拟滤波器、ADC 驱动器和 ADC

- 3 个可选的 T

Z设置:2 kΩ,、20 kΩ 和 200 kΩ - ADC 的内部 1.8 V LDO

- 所有无源组件,包括电源去耦

- 3 个可选的 T

小尺寸:12.00 mm × 6.00 mm CSP_BGA

采用 3.3 V 单电源供电

满量程输入电流为 800 μA (T

Z= 2 kΩ)快速输入过载恢复

高模拟输入电流至 40 mA

模拟滤波器,用于降噪和抗混叠滤波

- 可选的 1.0 MHz 和 100 MHz LPF 带宽

低输入参考电流噪声:16 pA rms

T

Z= 200 kΩ,65536 平均值,1 MHz 模拟滤波器支持低至 10 ns 的输入脉冲宽度

采样率高达 125 MSPS 的 14 位 ADC

串行 LVDS 数据输出

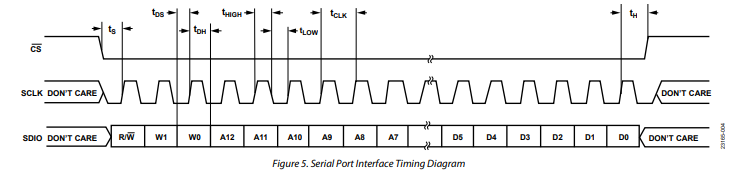

SPI 控制接口

静态功率:546 mW,启用 LDO

温度范围:−40 °C 至 +85 °C

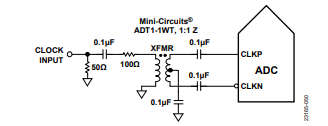

框图

ADC SPI时序图

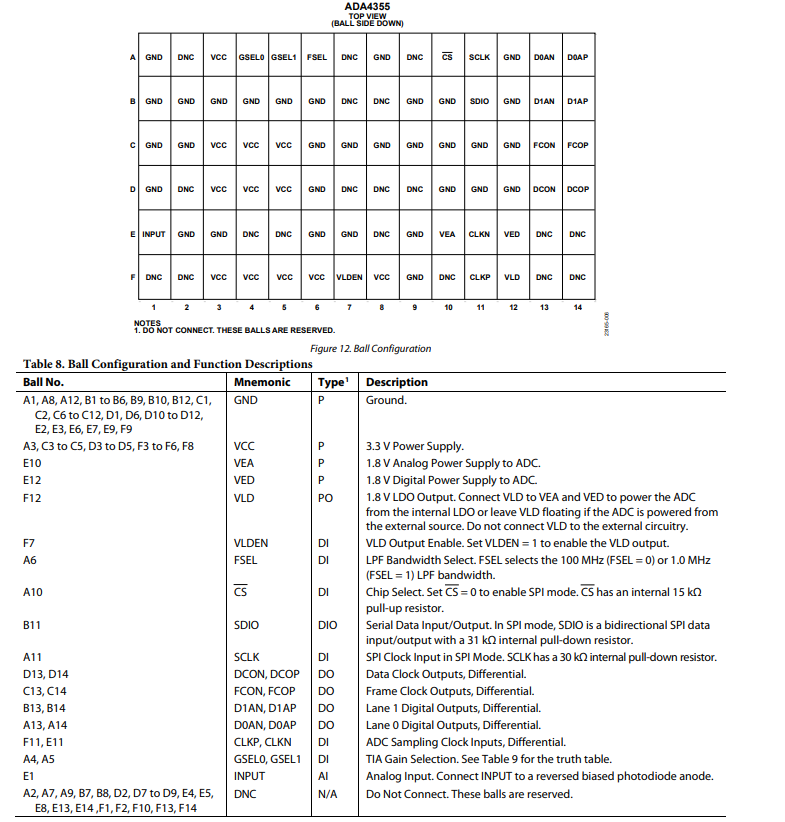

引脚配置描述

典型性能特征

工作原理

ADA4355集成了一个场效应晶体管(FET)、带有三种可切换增益(2 kΩ、20 kΩ和200 kΩ )的跨阻放大器(TIA )。增益切换设计用于将导致缓慢建立时间和缓慢过载恢复的误差源降至最低。内部过流限制电路允许输入电流超过满量程电流,同时仍能实现快速过载恢复。差分模式下,过流保护功能可使高达40 mA的模拟输入电流持续流入,而不会对TIA造成损坏。如图2所示,TIA的正节点偏置为1.65 V。

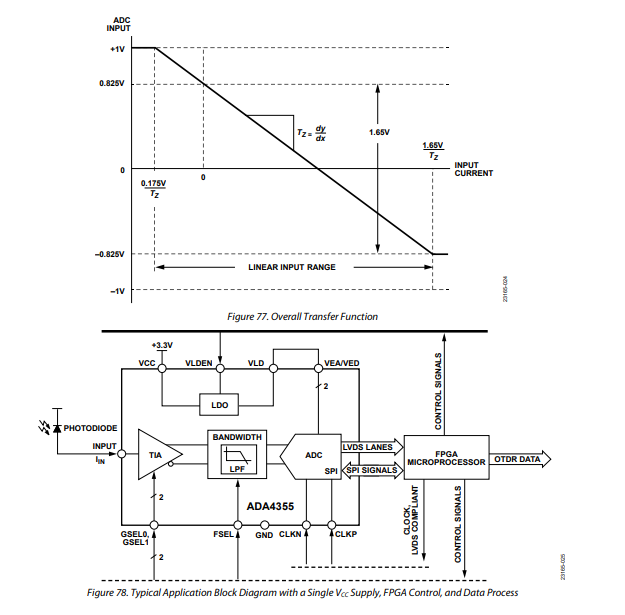

图77展示了整个系统的传递函数。由于光电探测器仅在一个方向(吸收或源出 )提供电流,因此整个传递函数存在0.825 V的偏移,以最大化ADC的输入范围。当输入电流为0 μA时,ADC差分输入为0.825 V。随着输入电流增加,TIA输出向地(GND)降低。当输入电流达到1.65 V/T(_z)时,总输出为地电平,将ADC差分输入电压限制为 - 0.825 V。正满量程输入电流为1.65 V/T(_z) ,并且有空间测量低至 - 0.175 V/T(_z) 的负输入电流。

应用信息

电源与电源控制

12 mm × 6 mm的CSP_BGA封装有多个引脚用于支持ADA4355的电源需求,其中12个引脚分别用于VCC、一个引脚用于VEA、VED和VLD。将VCC连接到干净的3.3 V电源,为ADA4355的模拟内核和片上LDO供电。将所有VCC引脚连接到3.3 V电源至关重要。VLD连接到片上1.8 V LDO输出,而VEA和VED是ADC电源引脚。要为ADC供电,需通过片上LDO将VLD连接到VEA和VED,并将VLDEN拉高(见图3 )。

如果需要外部1.8 V电源,可将VLDEN拉低,并将VEA和VED连接到外部1.8 V电源(见图4 )。

接地

ADA4355有多个引脚被指定为GND。封装内的GND引脚之间没有连接。因此,需将所有GND引脚连接到印刷电路板(PCB)上的低阻抗接地层。

时钟

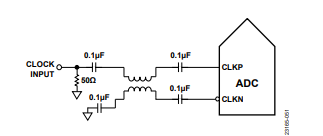

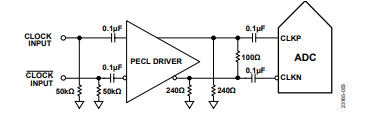

为实现最佳性能,需驱动ADC采样时钟输入CLKP和CLKN,采用差分信号。时钟信号通常通过变压器或电容与CLKIP和CLKIN引脚进行交流耦合。这些引脚内部已偏置(见图73 ),无需外部偏置。

时钟输入选项

ADA4355具有灵活的时钟输入结构。时钟输入可以是CMOS、LVDS、低电压正射极耦合逻辑(LVPECL)信号,或单端电压信号。无论信号类型如何,时钟源的抖动都是一个重要考量因素,具体内容在抖动考虑章节中描述。图79和图80展示了为ADA4355提供时钟的两种优选方法(时钟速率高达1 GHz ,优先采用内部时钟驱动器 )。低抖动时钟源可通过射频变压器或射频平衡 - 不平衡变换器将单端信号转换为差分信号。

图79. 变压器耦合差分时钟(高达200 MHz )

图80. 平衡 - 不平衡变换器耦合差分时钟(高达1 GHz )

建议对于125 MHz至1 GHz之间的时钟频率采用射频平衡 - 不平衡变换器配置,对于10 MHz至200 MHz的时钟频率采用射频变压器配置。

如果没有低抖动时钟源,另一种选择是如图81所示,将差分PECL信号交流耦合到采样时钟输入引脚。AD9510/AD9511/AD9512/AD9513/AD9514/AD9515/AD9516 - 0/AD9516 - 1/AD9516 - 2/AD9516 - 3/AD9516 - 4/AD9516 - 5/AD9517 - 0/AD9517 - 1/AD9517 - 2/AD9517 - 3/AD9517 - 4 PECL驱动器具有出色的抖动性能。

图81. 差分PECL采样时钟(高达1 GHz )

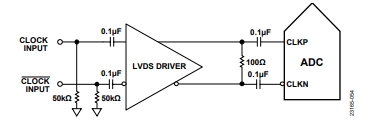

第三种选择是如图82所示,将差分LVDS信号交流耦合到采样时钟输入引脚。AD9510/AD9511/AD9512/AD9513/AD9514/AD9515/AD9516 - 0/AD9516 - 1/AD9516 - 2/AD9516 - 3/AD9516 - 4/AD9516 - 5/AD9516 - 6/AD9516 - 7/AD9517 - 0/AD9517 - 1/AD9517 - 2/AD9517 - 3/AD9517 - 4 LVDS驱动器具有出色的抖动性能。

图82. 差分LVDS采样时钟(高达1 GHz )

-

探索ADA4355:高性能电流输入μModule的卓越之选2026-03-27 122

-

深入解析ADA4356:可编程跨阻电流转比特接收器µModule2026-03-25 138

-

SN65LVDS302可编程27位串并接收器:设计与应用全解析2025-12-27 770

-

深入剖析SN65LVDS314:高性能可编程27位串并接收器2025-12-23 467

-

Analog Devices Inc. ADA4351-2精密可编程增益跨阻抗放大器数据手册2025-06-11 1107

-

ADA4352-2双通道、精密、可编程增益跨阻放大器(PGTIA),集成增益电阻器技术手册2025-05-09 1176

-

SN65LVDS314可编程27位串行至并行接收器数据表2024-07-11 476

-

高性能电流输入μModule ADA4355产品概述2023-09-15 1295

-

ADA4355 wiki用户指南2021-03-22 1429

-

ADA4355: Programmable Transimpedance, Current to Bits Receiver μModule Data Sheet2021-01-29 724

-

贸泽开售Analog Devices ADA4355紧凑型高性能光电探测器接收器μModule2021-01-27 3994

-

高速光学跨阻放大器ADA4355的功能特性及应用范围2020-11-30 2143

-

光学跨阻放大器ADA4355的功能特点及适用范围2020-11-28 2499

-

应用电路使用AD7799双通道色度计——可编程增益跨阻抗放大器和同步检测器2020-05-26 3269

全部0条评论

快来发表一下你的评论吧 !