ADL6317用于RF DAC和收发器的发射VGA技术手册

描述

概述

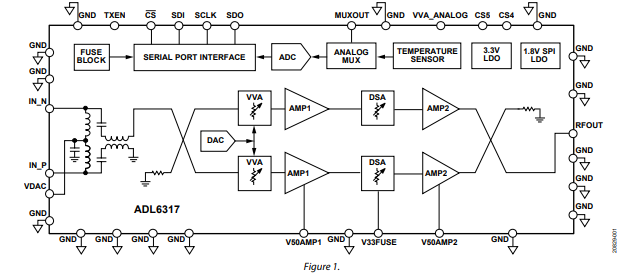

ADL6317 是一款发射可变增益放大器 (VGA),它可提供从射频数模转换器 (RF DAC)、收发器和片内系统 (SoC) 到功率放大器的接口。集成式平衡/不平衡转换器和混合耦合器可以在 1500 MHz 至 3000 MHz 的频率范围内实现高性能 RF 能力。

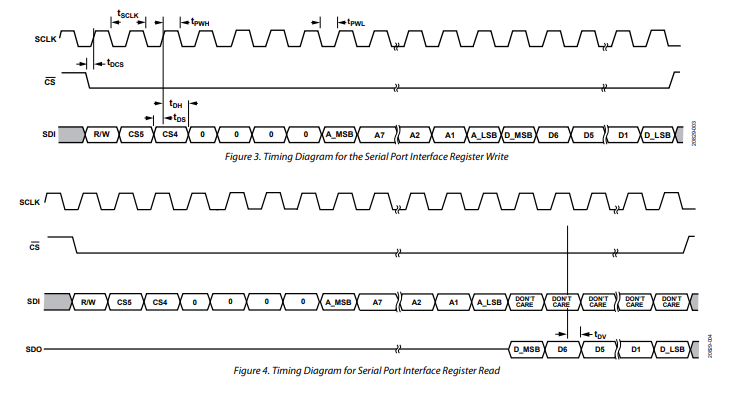

为了优化性能与功率水平,ADL6317 包含了电压可变衰减器 (VVA)、高线性度放大器和数字分级衰减器 (DSA)。集成到 ADL6317 中的所有套件都可以通过 4 线串行端口接口 (SPI) 进行编程。

ADL6317 采用高级硅锗 (SiGe)、双极互补金属氧化物半导体 (BiCMOS) 工艺制成。

数据表:*附件:ADL6317用于RF DAC和收发器的发射VGA技术手册.pdf

应用

- FDD/TDD 宽带通信系统中的 2G/3G/4G/长期演进 (LTE)

特性

- 提供从 RF DAC、收发器和 SoC 到功率放大器的接口的发射 VGA

- RF 输出频率范围:1500 MHz 至 3000 MHz

- 采用偏置器提供 RF DAC 输出的内部平衡/不平衡转换器

- 使用片内 DAC 时的集成 VVA 衰减范围:20.5 dB

- 2 级高线性度放大器

- RF DSA 衰减范围:15.5 dB,步进分辨率为 0.5 dB

- 50 Ω 差分输入和 50 Ω 单端输出

- 可通过 4 线 SPI 完全编程

- 5 V 单电源

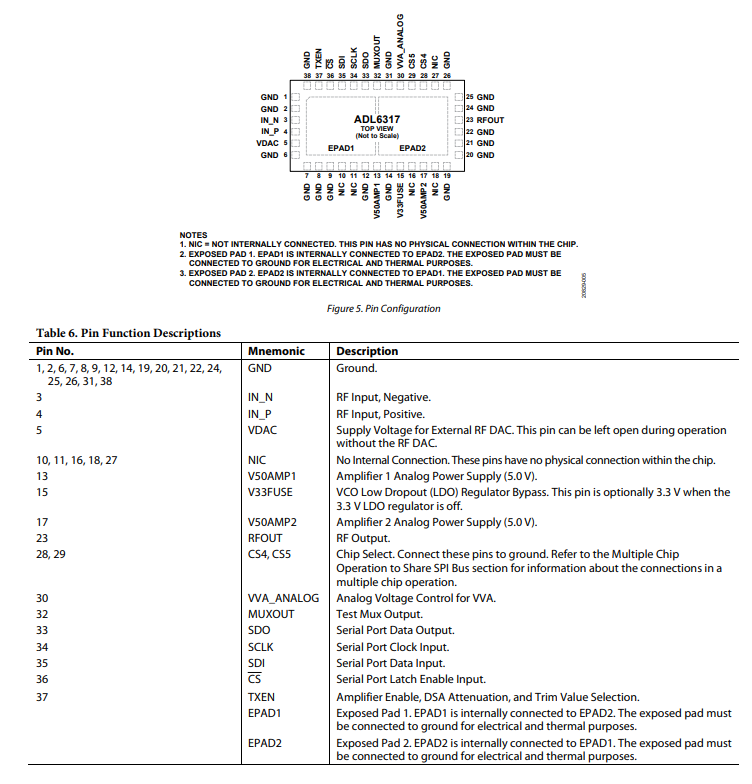

- 38 端子 10.5 mm × 5.5 mm LGA

框图

时序图

引脚配置描述

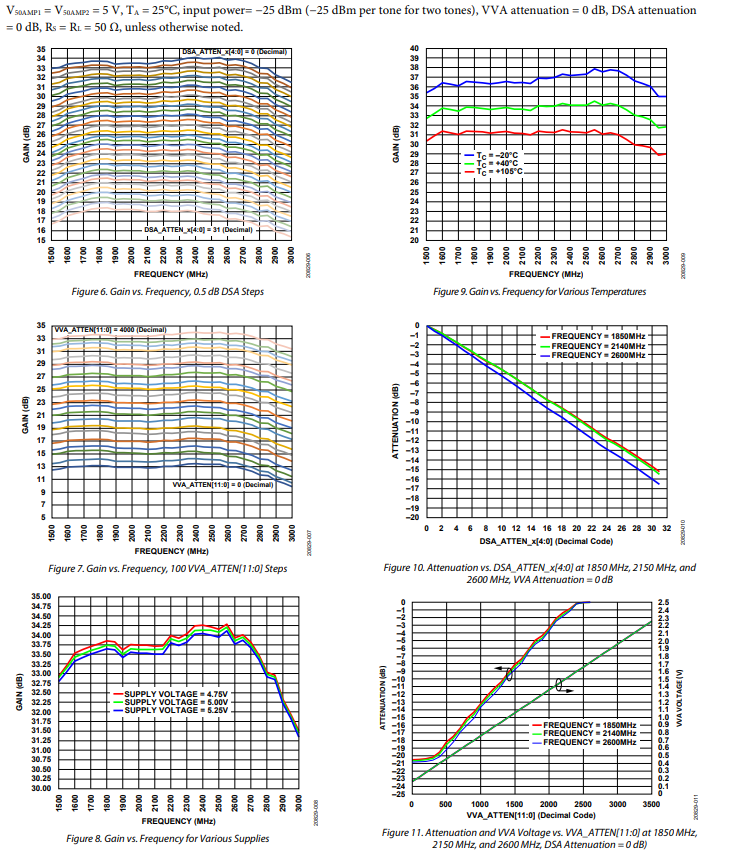

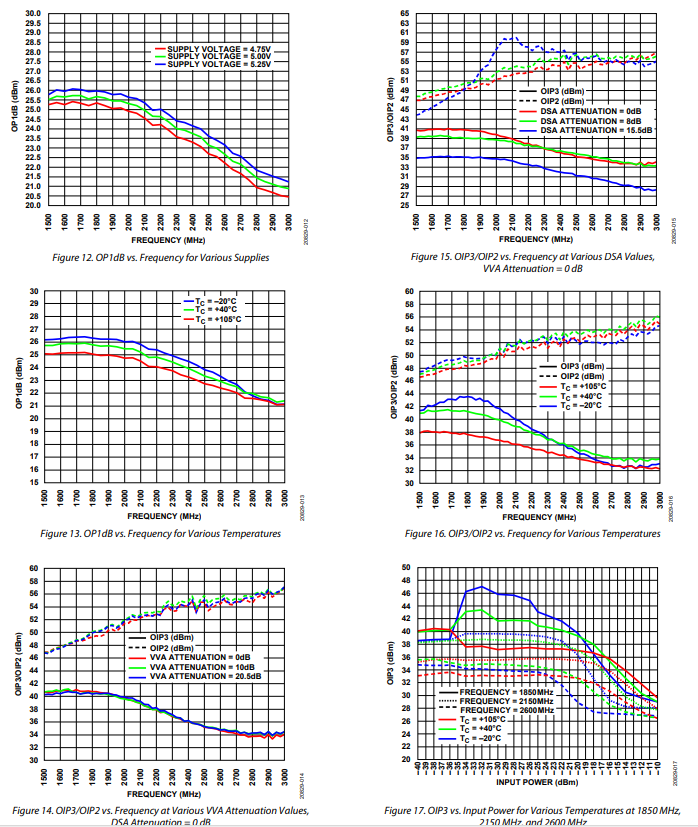

典型性能特征

工作原理

ADL6317是一款高度集成的发射可变增益放大器(VGA),用于在发射机中连接射频数模转换器(RF DAC)和功率放大器。ADL6317适用于高动态范围多载波发射机设计。

ADL6317提供多种增益控制选项,集成了一个20.5 dB可变增益放大器(VGA),可通过片内DAC控制或外部电压控制。它具有高线性度放大器、一个15.5 dB的射频数字步进衰减器(DSA),以0.5 dB的步长进行衰减,随后是第二级高线性度放大器。

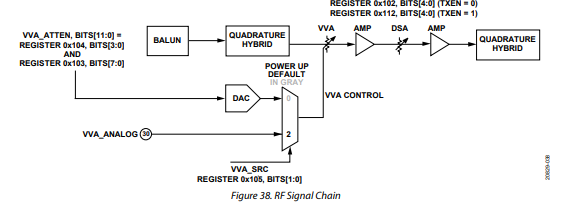

将ADL6317的各个模块组合起来,信号通过器件的路径从差分输入开始,由集成的平衡 - 不平衡变换器转换为单端信号,然后由内部正交耦合器进行正交耦合。

接下来,集成的VVA、放大器1、DSA和放大器2会在射频信号输出到输出端口之前对其幅度进行优化。ADL6317的所有集成模块均可通过SPI进行编程。

带DAC接口网络的射频输入平衡 - 不平衡变换器

ADL6317通过集成的平衡 - 不平衡变换器,将单通道50Ω输入差分信号转换为单端信号。宽带匹配使DAC能够在1500 MHz至3000 MHz的频率范围内进行操作,并且包含一个偏置三通,为RF DAC提供直流偏置。

正交混合器

射频输入和射频输出端的集成正交混合器可实现宽带反射系数匹配,并与低输入和输出回波损耗的RF DAC实现功率匹配。

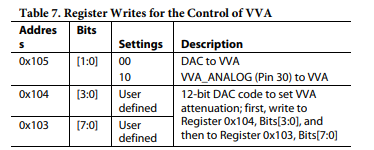

射频信号链

射频路径包括一个20.5 dB的VVA、第一级固定增益放大器(15.5 dB DSA)和第二级固定增益放大器(见图38 )。ADL6317对VVA衰减有两种控制模式:使用集成12位DAC的内部模拟控制,以及外部模拟控制。对于内部控制,使用寄存器0x04,位[3:0]和寄存器0x03,位[7:0]来设置衰减量。数字位采用双缓冲,以避免主载波毛刺。因此,在写入寄存器0x03之前,必须先写入寄存器0x04。对于VVA的外部模拟控制(引脚30 ),需将电压施加到VVA_ANALOG引脚(引脚30 )。图38展示了用于VVA控制的寄存器写入示例。

接下来,固定增益放大器采用正交平衡配置。DSA提供15.5 dB的衰减范围,步长为0.5 dB。数字5位DSA衰减控制在寄存器0x112的位[4:0]中。最后,第二级固定增益放大器采用正交平衡配置。

-

ADL6316:500 MHz - 1000 MHz 发射 VGA 的卓越之选2026-01-14 465

-

ADL6337 35dB增益,500MHz至5200MHz传输VGA技术手册2025-04-19 1136

-

EVAL-ADL6317 EVAL-ADL6317评估板2021-07-10 227

-

基于ADI ADL6317辅助射频(RF)增益增益(VGA)方案设计2021-06-12 3310

-

ADL6317:与射频DAC和收发器配合使用的传输VGA数据表2021-05-16 788

-

VGA光纤收发器是什么2020-12-25 1158

-

什么是用于RF收发器的简单基带处理器?2019-09-19 2846

-

RadioVerse生态系统中的宽带收发器分享!2019-09-17 2476

-

新型RF收发器对微微蜂窝基站发展的影响2019-06-27 1772

-

RadioVerse生态系统中的宽带收发器2018-08-16 2547

-

MAX2830 直接变频RF收发器2011-04-21 2139

全部0条评论

快来发表一下你的评论吧 !