LTC6912双通道可编程增益放大器,具有串行数字接口技术手册

描述

概述

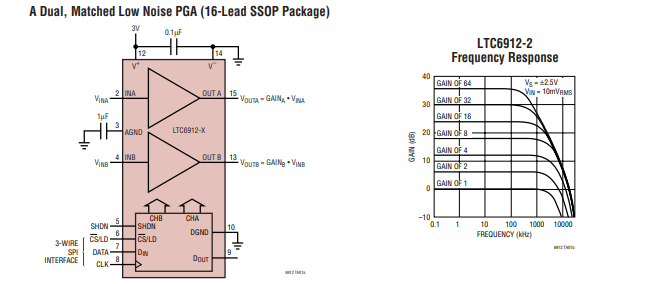

LTC6912 是双通道、低噪声、数字可编程增益放大器 (PGA) 系列,易于使用,占用的 PC 板空间非常小。两个通道的增益均可使用 3 线 SPI 接口独立编程,以选择 0、1、2、5、10、20、50 和 100V/V (LTC6912-1) 的电压增益;以及 0、1、2、4、8、16、32 和 64V/V (LTC6912-2)。所有增益都是反相的。

LTC6912 系列由 2 个具有轨到轨输出的匹配放大器组成。当使用运行时,它们还将处理轨到轨输入信号。在 AGND 引脚内部生成的半电源基准支持单电源应用。LTC6912-X 系列采用 2.7V 至 10.5V 的单电源或分离电源供电,采用微型 SSOP 和 DFN-12 封装。

数据表:*附件:LTC6912双通道可编程增益放大器,具有串行数字接口技术手册.pdf

应用

- 数据采集系统

- 动态增益变化

- 自动测距电路

- 自动增益控制

特性

- 2 个通道,具有独立的增益控制

- LTC6912-1:(0、1、2、5、10、20、50 和 100V/V)

- LTC6912-2:(0、1、2、4、8、16、32 和 64V/V)

- 失调电压 = 2mV (最大值) (–40°C 至 85°C)

- 通道间增益匹配:0.1dB (最大值)

- 3 线 SPI^TM^ 接口

- 高增益时扩展增益带宽

- 可提供有线 OR 输出(2:1 模拟多路复用器功能)

- 低功耗硬件关断(仅限 GN-16,2.7V 时最大 2μA)

- 轨到轨输入范围

- 轨到轨输出摆幅

- 单电源或双电源:2.7V 至 10.5V 总计

- 输入噪声:12.6nV/√Hz

- 总系统动态范围达 115dB

- 16 引脚 GN (SSOP) 或 12 引脚 DFN 封装选项

典型应用

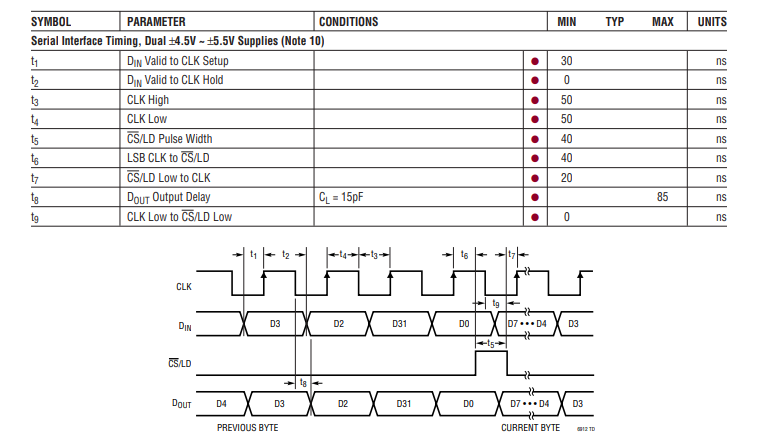

串行接口规格

注释

- 绝对最大额定值是指超过这些值可能会损害器件使用寿命的数值。

- LTC6912 - 1C和LTC6912 - 1L在 - 40°C至85°C的工作温度范围内可保证功能正常。LTC6912 - 1H在 - 40°C至125°C的工作温度范围内可保证功能正常。

- LTC6912 - 1C的规格性能是在0°C至70°C下测量确定的,LTC6912 - 1L按预期或要求应在 - 40°C至85°C达到指定性能,但未在此温度范围内进行测试或鉴定;LTC6912 - 1H在 - 40°C至85°C范围内可保证达到指定性能,LTC6912 - 1H在 - 40°C至125°C范围内保证达到指定性能。

- 输出电压摆幅是指输出与相应电源轨之间的差值。

- 不建议在高于150°C(对于GN封装)和125°C(对于DFN封装)的温度下进行输出短路操作。

- 增益不能通过输出电压在电源电压约30% - 70%范围内摆动的大信号直流测试来测量。

- 通道间隔离度的测量方法是:向一个通道施加200kHz输入信号,使其输出产生1V有效值的变化,测量另一个通道相对于AGND的输出电压有效值。隔离度计算公式为:隔离度 = 20×log_{10}(frac{V_{OUTB}}{V_{OUTA}}) (单位:dB)。高通道间隔离度很大程度上取决于正确的电路布局。更多信息请参见应用信息部分。

- 相对于INA或INB输入的失调电压是(1 + 1/增益)乘以内部OP放大器的失调电压,其中增益为标称增益值。典型的失调电压值仅适用于25°C。更多信息请参见应用信息部分。

- 在给定增益设置下,输入电阻的部件间差异约为±30% 。

- 通过设计保证,无需测试。

- 状态13、14和15(二进制110xx)未使用。将通道编程为这些状态之一,会使该通道进入低功耗关闭状态。需要注意的是,将通道编程为状态15(二进制11111)会导致该通道消耗高达20mA的电源电流,不建议这样做。

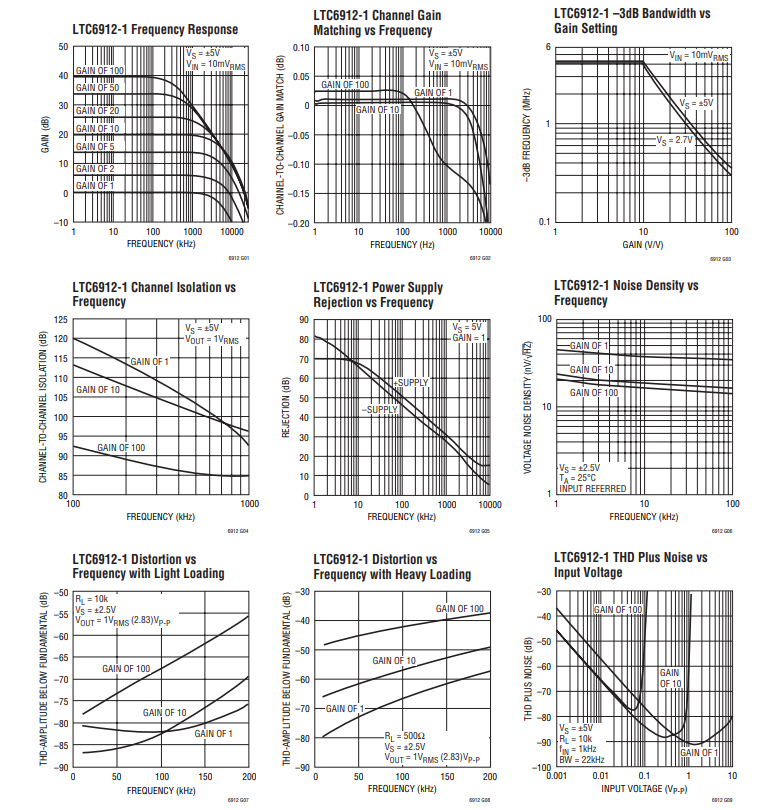

典型性能特征

应用信息

功能描述

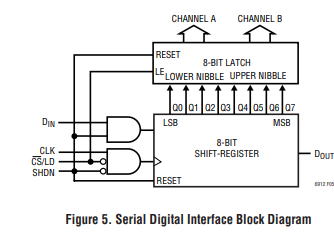

LTC6912 - X是一款小尺寸、宽带、反相双通道放大器,其电压增益可独立编程。每个通道都可通过三线串行数字接口选择八种电压增益,该接口兼容TTL或CMOS逻辑电平(见图5)。表1和表2分别列出了LTC6912 - 1和LTC6912 - 2的标称增益。在放大器内部,通过切换与闭环运算放大器电路匹配阵列中的电阻来实现增益控制(见图1)。各独立放大器的带宽在“典型性能特征”部分的增益设置测量频率响应中显示。

三线SPI接口说明

每个放大器的增益控制可通过三线SPI接口独立编程(见图5)。LTC6912三线串行接口的逻辑电平兼容TTL/CMOS。当**overline{CS/LD}为低电平时,串行数据D_{IN}**在时钟上升沿移入8位移位寄存器,最高有效位(MSB)先传输。**D_{OUT}**上的串行数据在时钟下降沿移位输出。**overline{CS/LD}上升沿会锁存移位寄存器的内容,加载到8位D锁存器中,并在芯片内部禁用时钟。D锁存器的高四位(4个最高有效位)配置B通道放大器的增益,低四位(4个最低有效位)配置A通道放大器的增益。表1和表2详细列出了相应的标称增益。在将overline{CS/LD}**拉低之前,务必确保CLK为低电平,以避免向8位移位寄存器输入额外的时钟脉冲(见图5)。

**D_{OUT}在所有状态下均有效,因此D_{OUT}**不能与其他SPI输出“线或”。

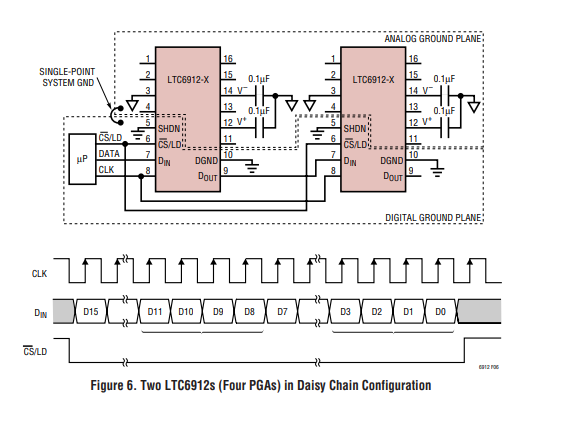

LTC6912可与其他LTC6912或其他具有串行接口的器件进行SPI级联,方法是将D_{OUT}连接到下一个芯片的D_{IN},同时CLK和**overline{CS/LD}对菊花链中的所有芯片保持公共连接。串行数据在overline{CS/LD}**信号拉高时同步时钟到所有芯片,从而同时更新所有芯片。图6展示了两个LTC6912进行SPI菊花链连接的示例。

配置

建议在数据传输间隙,串行接口信号保持空闲状态,以尽量减少数字噪声耦合到模拟路径中。

上电复位

初次通电时,上电复位状态下两个放大器均处于低功耗软件关断状态(状态 = 8)(见表1和表2 )。在此状态下,两个模拟放大器均被禁用,其输入和输出均断开。为便于在使用该器件的应用中进行应用,其具有一个2:1模拟多路复用器,通过它放大器的输出可以进行线或连接,并且LTC6912可以交替选择通道A和通道B。如果输出进行线或连接,必须注意确保软件关断状态(状态 = 8)始终在两个通道中的一个通道上被编程。

时序限制

CMOS增益控制逻辑的建立时间通常为几纳秒,比模拟信号路径的速度更快。当放大器的增益发生变化时,限制时序的因素是模拟部分。与任何可编程增益放大器一样,每次增益变化都会导致放大器输出产生瞬变,因为放大器的输出会以有限速度向不同缩放版本的输入信号移动。LTC6912的模拟路径会以特征时间常数或时间尺度tau 稳定下来,该时间尺度是一阶带限响应的标准值:

[ tau = 0.35/f_{-3dB} ]

详见“典型性能特征”部分的“ - 3dB带宽与增益设置”图表。

-

探索LTC6912:高性能双可编程增益放大器的卓越之选2026-01-15 315

-

使用OPA2683低功耗全差动可编程增益放大器参考设计2022-09-27 8943

-

怎样去编写stm32驱动LTC6912程控放大器的程序呢2021-11-15 1274

-

LTC6911:MSOP数据表中具有数字可编程增益的双匹配放大器2021-05-26 1044

-

LTC6912:带串行数字接口的双可编程增益放大器产品手册2021-04-30 1311

-

CN0363:带可编程增益跨阻放大器和数字同步检波功能的双通道色度计2021-03-21 965

-

应用电路使用AD7799双通道色度计——可编程增益跨阻抗放大器和同步检测器2020-05-26 3269

-

数字可编程增益放大器设计方案2019-07-17 2884

-

可编程增益放大器在模数接口的应用2019-05-21 2534

-

带可编程增益跨阻放大器和数字同步检波功能的双通道色度计2017-03-05 1119

-

可编程增益放大器2008-12-17 1339

全部0条评论

快来发表一下你的评论吧 !