ADMV8913-EP X频段、数字可调谐、高通和低通滤波器技术手册

描述

概述

ADMV8913是一款完整的单片式微波集成电路,具有可选的数字工作频率。该器件集成了一个高通滤波器和一个低通滤波器,可在7至12 GHz频率范围内实现通带响应。

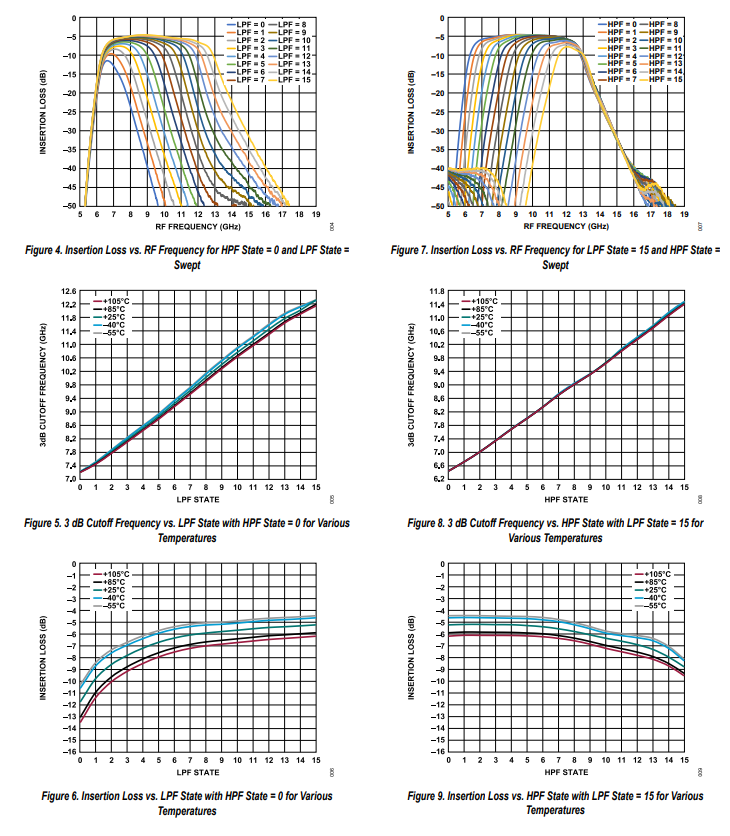

ADMV8913采用灵活的架构,可以独立控制高通和低通滤波器的3 dB截止频率(f 3dB )。每个滤波器的数字逻辑控制的宽度为4位(16种状态),通过控制片内电抗元件来调节f 3dB 。典型插入损耗为5 dB,宽带抑制为35 dB,非常适合用于最大限度地降低系统谐波。

这款可调谐滤波器可用作大型开关滤波器组和腔体调谐滤波器的小型替代方案,可以在先进的通信应用中提供动态可调的解决方案。

数据表:*附件:ADMV8913-EP X频段、数字可调谐、高通和低通滤波器技术手册.pdf

应用

- 测试与测量设备

- 军用雷达和电子战/电子对抗

- 卫星通信

- 工业和医疗设备

特性

- 数字可调谐、3dB上下截止频率

- 优化宽带抑制:35 dB

- 以单芯片替代分立式滤波器组

- 紧凑型6 × 3 × 0.89 mm LGA封装

- 唯一封装/测试厂

- 唯一制造厂

- 军用温度范围(如−55°C至+105°C)

- 受控制造基线

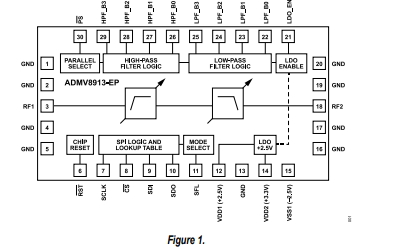

框图

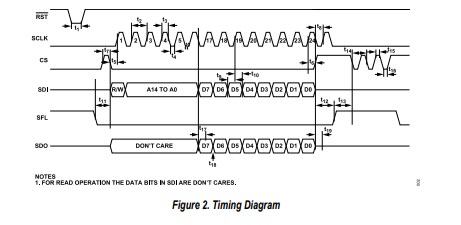

时序图

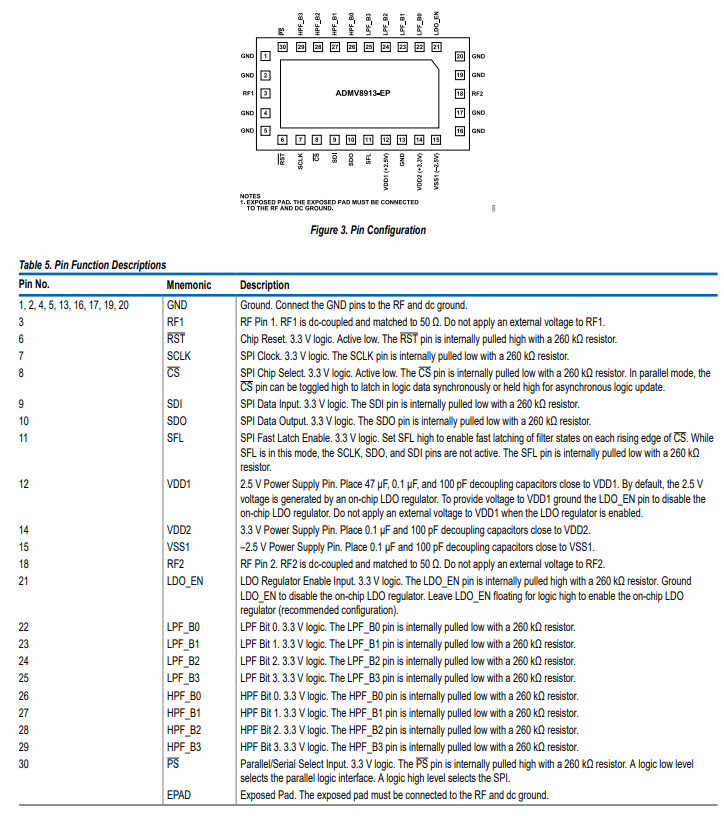

引脚配置描述

典型性能特征

工作原理

芯片架构

ADMV8913 - EP是一款组合式可调高通滤波器(HPF)和可调低通滤波器(LPF),可在X波段频率范围内实现带通响应。图1为ADMV8913 - EP的概念框图。

可调高通滤波器

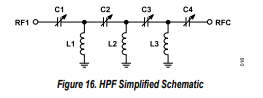

图16展示了HPF的简化原理图,它是一种切比雪夫型滤波器。**f_{3dB}可通过改变电容C1至C4进行调整。这些可调电容由4位数字序列控制,共产生16种不同值。这些可调电容的步长经过调整,使得数字二进制代码的每个增量在f_{3dB}**中产生大致相同的增量。注意,图16中所示的RFC是HPF和LPF的内部连接。

可调低通滤波器

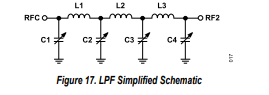

图17展示了LPF的简化原理图,它是一种切比雪夫型滤波器。**f_{3dB}可通过改变电容C1至C4进行调整。这些可调电容由4位数字序列控制,共产生16种不同值。这些可调电容的步长经过调整,使得数字二进制代码的每个增量在f_{3dB}**中产生大致相同的增量。注意,图17中所示的RFC是HPF和LPF的内部连接。

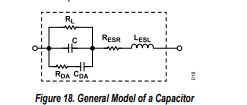

射频连接

ADMV8913 - EP的RF1和RF2引脚与片上ESD保护二极管直流耦合。如果系统中其他组件在RF1和RF2引脚上存在直流电压,建议根据这些引脚串联直流隔直电容。直流隔直电容的值通常应大于100 pF,以在低频时将滤波器的插入损耗降至最低。在较高工作频率下,可能需要考虑所选电容的寄生元件。图18展示了一个带有寄生元件的电容通用模型。寄生串联电感(L_{ESL})通常是最受关注的,因为在高于10 GHz的频率下,其阻抗可能占主导地位。其他寄生元件,包括泄漏电阻(R_{L})、介电吸收电阻(R_{DA})、介电吸收电容(C_{DA})和等效串联电阻(R_{ESR}),虽然不是关键考虑因素,但为完整起见也在此列出。

SPI配置

ADMV8913 - EP的SPI可通过5引脚SPI端口对器件进行特定功能或操作配置。该接口为用户提供了额外的灵活性和定制化功能。SPI由五条控制线组成:SFL、SCLK、SDI、SDO和overline{CS} 。对于普通SPI操作,需将SFL引脚置低。

SPI协议包含一个读写位(R/W),后跟15位寄存器地址和8位数据位。地址字段和数据字段按最高有效位(MSB)在前、最低有效位(LSB)在后的顺序组织。将MSB设置为0表示写操作,将MSB设置为1表示读操作。写周期必须在SCLK的上升沿采样。24位串行写地址和数据在SCLK上升沿时,从SDI控制线以MSB在前、LSB在后的顺序移入。ADMV8913 - EP输入逻辑电平在写周期支持3.3V接口。

在读周期中,R/W位和15位寄存器地址位在SCLK上升沿从SDI控制线移入,然后8位串行读数据从SDO控制线移出。在读周期开始时,SDO的输出逻辑电平为3.3V。SDO的输出驱动器在SCLK上升沿使能,在最后一个上升沿之后保持激活状态,直到读周期结束。在读操作中,当**overline{CS}**无效时,SDO返回高阻抗状态,直到下一次读事务。**overline{CS}**为低电平有效,必须在写或读序列结束时置为无效。

**overline{CS}**上的低电平输入启动并控制通信周期。**overline{CS}引脚允许多个设备使用同一条串行通信线。当overline{CS}**输入为高电平时,SDO引脚处于高阻抗状态。在通信周期内,芯片选择必须保持低电平。SPI通信协议遵循Analog Devices SPI标准。更多信息,请参见《ADI - SPI串行控制接口标准(版本1.0)》。

模式选择

ADMV8913 - EP有三种工作模式:并行模式、SPI写模式和SPI快速锁存模式。并行模式用于绕过SPI,允许直接使用HPF_B3至HPF_B0和LPF_B3至LPF_B0逻辑输入对滤波器进行编程。要选择并行模式 ,需将SFL引脚置低。

-

Analog Devices Inc. ADMV8913-EVALZ评估板数据手册2025-07-02 820

-

Analog Devices Inc. ADMV8913-EP MMIC数据手册2025-07-01 940

-

Analog Devices Inc. ADMV8526数字可调谐滤波器数据手册2025-06-22 1179

-

Analog Devices Inc. ADMV8505数字可调谐带通滤波器数据手册2025-06-10 1184

-

Analog Devices Inc. ADMV8052数字可调谐带通滤波器数据手册2025-06-06 1276

-

Analog Devices Inc. ADMV8502数字可调谐带通滤波器数据手册2025-05-27 1014

-

ADMV8818-EP 2GHz至18GHz的数字可调谐高通和低通滤波器技术手册2025-04-23 1468

-

ADMV8420 10GHz至21.7GHz可调谐带通滤波器技术手册2025-04-22 1120

-

ADI的ADMV8818数字式可调滤波器2021-11-11 4090

-

UG-1661:评估ADMV8416和ADMV8432可调带通滤波器2021-04-19 1238

-

ADMV8913:X波段、数字可调、高通和低通过滤初步数据表2021-03-22 699

-

可调低通滤波器2009-09-17 2454

全部0条评论

快来发表一下你的评论吧 !