ADMV8052 30MHz至520MHz数字可调带通滤波器技术手册

描述

概述

ADMV8052是一款射频滤波器,具有数字可选的工作频率。该器件集成了三个带通滤波器,跨越从30到520 MHz的三个指定频段。

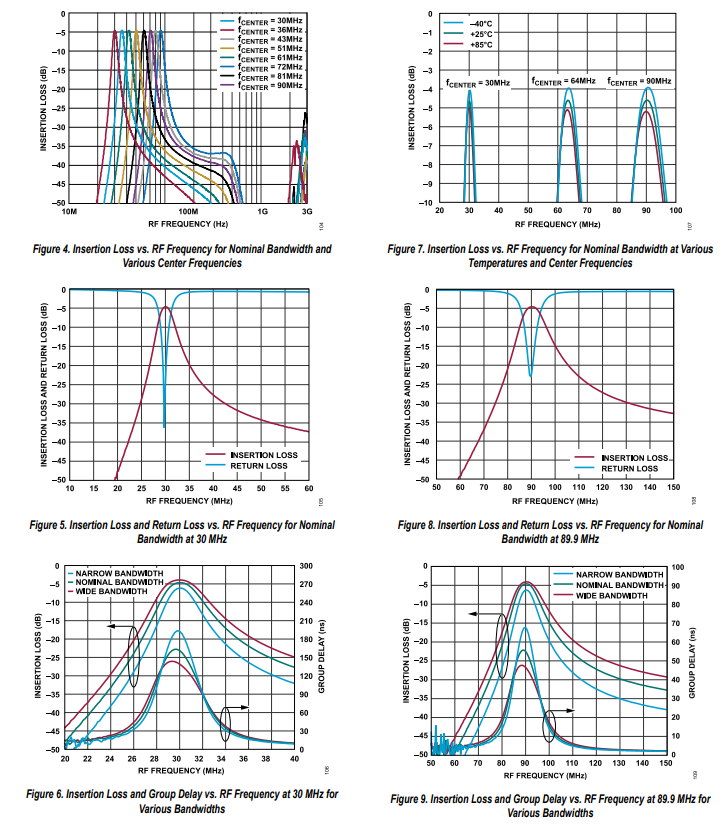

可使用融入了正在申请专利的插值法的8位值(256种状态)调整中心工作频率(f C )。典型3 dB带宽(BW)为9%,可调性为± 2%。插入损耗通常为4 dB,2 x BW时的抑制为20 dB,非常适合用于较大限度地降低系统谐波。此外,灵活的架构采用旁路模式,具有1 dB的低插入损耗。

这款可调谐滤波器可用作大型开关滤波器组和腔体调谐滤波器的小型替代方案,可以在先进的通信应用中提供动态可调的解决方案。

数据表:*附件:ADMV8052 30MHz至520MHz数字可调带通滤波器技术手册.pdf

应用

- 陆地移动无线电

- 测试与测量设备

- 军用雷达和电子战/电子对抗

- 卫星通信

- 工业和医疗设备

特性

- 数字可调谐、多倍频程、带通调谐

- 3dB带宽(BW):7至11%

- 低插入损耗:4dB (9% BW)

- 出色的抑制:20 dB (2 x BW)

- 出色的线性度

- 以单芯片替代分立式解决方案

- 紧凑型22 × 22 x 5.73 mm LGA封装

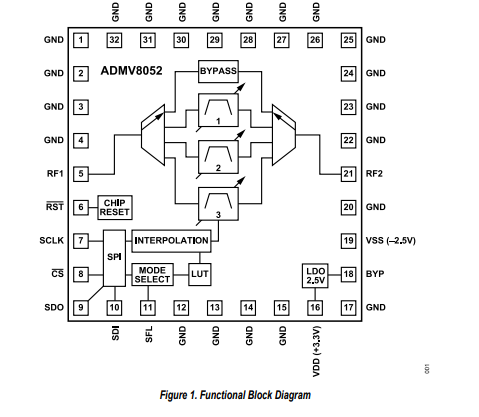

框图

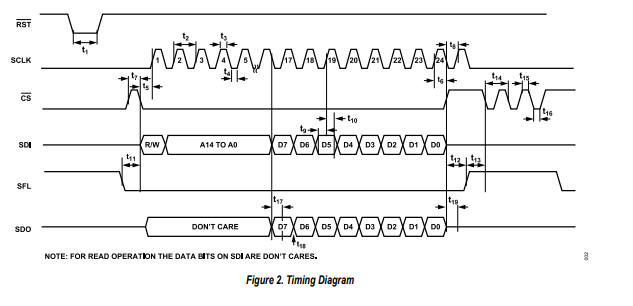

时序图

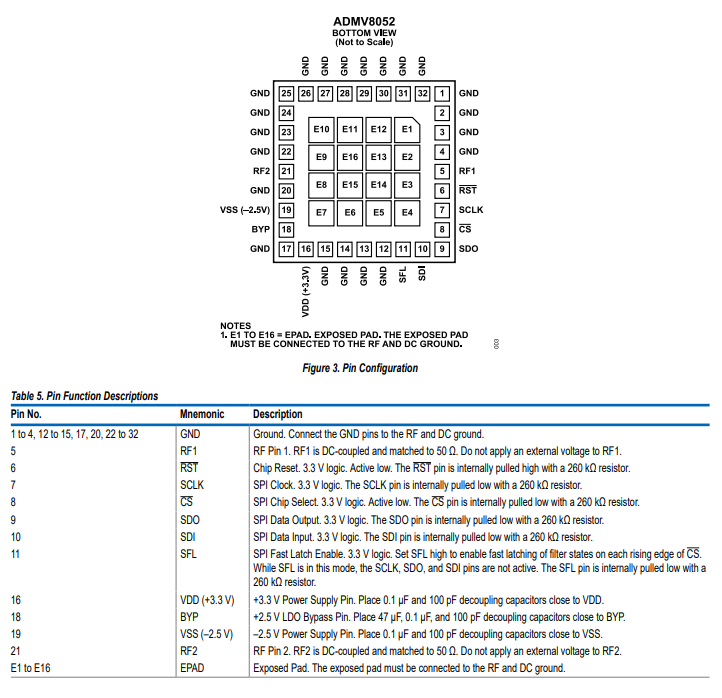

引脚配置描述

典型性能特征

工作原理

芯片架构

ADMV8052包含三个带通滤波器(BPF)以及一个可选的旁路配置,可通过两个四选一(SP4T)开关进行选择。该器件可在30 MHz至620 MHz的频率带宽内实现全覆盖,且无任何死区。图1是ADMV8052的概念框图。

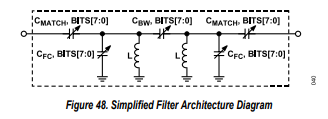

ADMV8052内的每个带宽包含多个开关电容,这些电容可改变射频性能。图48详细展示了滤波器架构的简化示意图。

两个中心频率电容((C_{FC}))由(f_{CENTER})负载值配置,该值可调节滤波器的(f_{CENTER}) 。同样,带宽电容((C_{BW}))由带宽负载值配置,该值可调节滤波器的带宽响应。此外,两个匹配电容((C_{MATCH}))根据滤波器的匹配负载值进行设置,可调节匹配阻抗。

(f_{CENTER})、带宽和匹配负载值各有256种状态(8位)。理论上,ADMV8052内每个频段的(f_{CENTER})、带宽和匹配负载值组合有超过1600万种可能状态。为简化这些值的选择,亚德诺半导体开发了三种正在申请专利的插值功能,以方便实施。

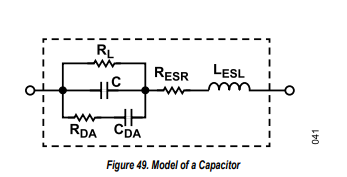

射频连接

ADMV8052的RF1和RF2引脚与片内射频开关直流耦合。如果系统中存在直流电压,则RF1和RF2引脚需与其他组件进行交流耦合,建议在这些引脚串联隔直电容。隔直电容的选择必须基于滤波器的频率。通常,值大于10 nF的电容足以在较低工作频率下将插入损耗降至最低。在较高工作频率下,可能需要考虑所选电容的寄生元件。图49展示了电容的一般模型。电容的寄生串联电感((L_{ESL}))通常在给定的其他寄生元件中占主导地位,其阻抗可能会很显著。其他寄生元件,包括泄漏电阻((R_{L}))、介电吸收电阻((R_{DA}))、介电吸收电容((C_{DA}))和电气串联电阻((R_{ESR}))对整体性能的影响较小。

电容模型

图49展示了电容的模型。

SPI配置

ADMV8052的SPI接口允许通过5引脚SPI端口对器件进行特定功能或操作的配置。该接口为用户提供了更高的灵活性和定制性。ADMV8052的SPI接口由五条控制线组成:SFL、SCLK、SDI、SDO和(overline{CS}) 。对于正常的SPI操作,需将SFL引脚保持为低电平。

SPI协议由一个地址字节和15个寄存器地址位及8个数据位组成。地址字段和数据字段均为大端序(MSB在前,LSB在后)。

将MSB设置为0进行写操作,设置为1进行读操作。写周期中,SDI上的数据必须在SCLK的上升沿采样。24位的串行写地址和数据在SDI控制线上从MSB到LSB逐位移入。ADMV8052的输入逻辑电平支持3.3V接口。

对于读周期,(overline{R/W})位和15个寄存器地址位移入,在SCLK的上升沿对SDI进行采样。然后,8位串行数据在SDO逻辑电平上移出,第一个字节在SCLK的下降沿移出。输出驱动逻辑电平为3.3V。在指令周期的最后一个SCLK上升沿之后,SDO的输出驱动器启用,并在读取周期内保持激活状态。在读操作中,当(overline{CS})无效时,SDO返回高阻态,直到下一次读取事务。(overline{CS})必须在写或读序列的开头和结尾置为有效。

(overline{CS})上的低电平有效输入启动并允许通信周期。(overline{CS})引脚允许多个器件在同一串行通信线上使用。SDO引脚在通信周期内为高阻抗状态。在通信周期内,芯片选择必须保持低电平。SPI通信协议遵循亚德诺半导体的SPI标准。

-

Analog Devices Inc. ADMV8526数字可调谐滤波器数据手册2025-06-22 1181

-

Analog Devices Inc. ADMV8505数字可调谐带通滤波器数据手册2025-06-10 1187

-

Analog Devices Inc. ADMV8052数字可调谐带通滤波器数据手册2025-06-06 1283

-

Analog Devices Inc. ADMV8502数字可调谐带通滤波器数据手册2025-05-27 1018

-

ADMV8416 6.3GHz至18GHz、可调带通滤波器技术手册2025-04-23 1131

-

ADMV8502 90MHz至225 MHz、数字可调谐带通滤波器技术手册2025-04-22 1016

-

ADMV8513:520 MHz至1300 MHz、数字金枪鱼、带-包过滤器数据表 ADI2023-10-08 87

-

UG-1661:评估ADMV8416和ADMV8432可调带通滤波器2021-04-19 1239

-

ADMV8052:30兆赫至520兆赫兹数字可调带通过滤初步数据表2021-03-22 1456

-

ADMV8052: 30 MHz to 520 MHz Digitally Tunable Band-Pass Filter Preliminary Data Sheet2021-01-27 1208

全部0条评论

快来发表一下你的评论吧 !