HMC1119 0.25dB LSB、7位硅数字衰减器,0.1GHz至6.0GHz技术手册

描述

概述

HMC1119是一款宽带、高精度、7位数字衰减器,工作频率范围为0.1 GHz至6.0 GHz,以0.25 dB步长提供31.5 dB的衰减控制范围。

HMC1119采用硅工艺实现,提供超快速建立时间、低功耗和高ESD鲁棒性。该器件具有安全状态转换特性,并针对频率和温度范围内出色的步长精度和高线性度进行了优化。RF输入与输出为匹配元件。该设计为双向;因此,RF输入与输出可以互换。

HMC1119集成了片内稳压器,具有3.3 V至5.0 V宽电源工作范围,而电气特性性能不会发生变化。HMC1119集成一个驱动器,支持对衰减器进行串行(3线式)和并行控制。

该器件采用符合RoHS标准的紧凑型4 mm × 4 mm LFCSP封装。

同时提供完全填充的评估板。

数据表:*附件:HMC1119 0.25dB LSB、7位硅数字衰减器,0.1GHz至6.0GHz技术手册.pdf

应用

- 蜂窝通信基础设施

- 微波无线电和甚小孔径终端(VSAT)

- 测试设备和传感器

- IF和RF设计

特性

- 衰减范围:0.25 dB LSB步进至31.75 dB

- 低插入损耗:

- 1.1 dB(1.0 GHz时)

- 1.3 dB(2.0 GHz时)

- 典型步进误差:小于±0.1 dB

- 出色的衰减精度:小于±0.2 dB

- 低相移误差:6°相移(1.0 GHz)

- 安全状态转换

- 高线性度

- 1 dB压缩(P1dB):31 dBm(典型值)

- 输出三阶交调截点(IP3):54 dBm(典型值)

- RF建立时间(0.05 dB最终RF输出):250 ns

- 单电源供电:3.3 V至5.0 V

- ESD额定值:2级((2 kV人体模型(HBM))

- 24引脚、4mm× 4mm LFCSP封装:16mm2

框图

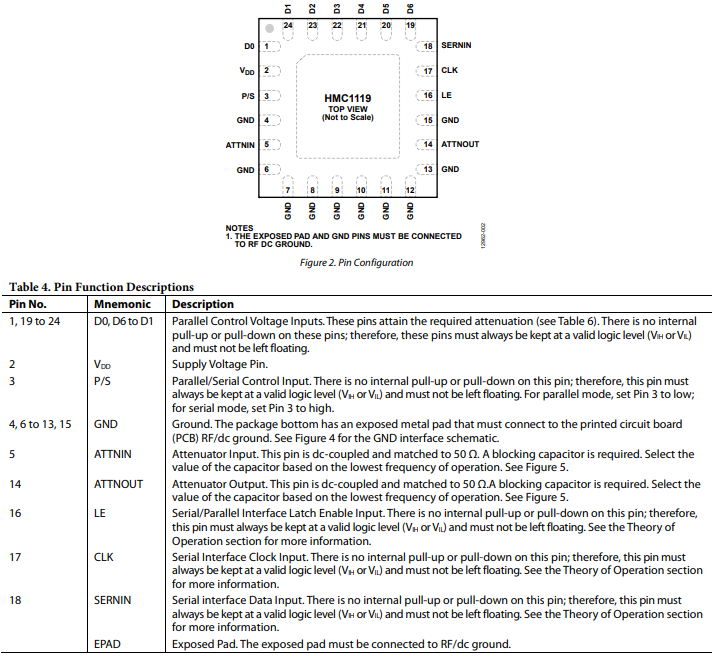

引脚配置描述

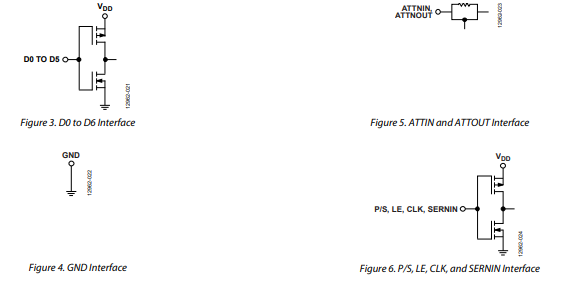

接口示意图

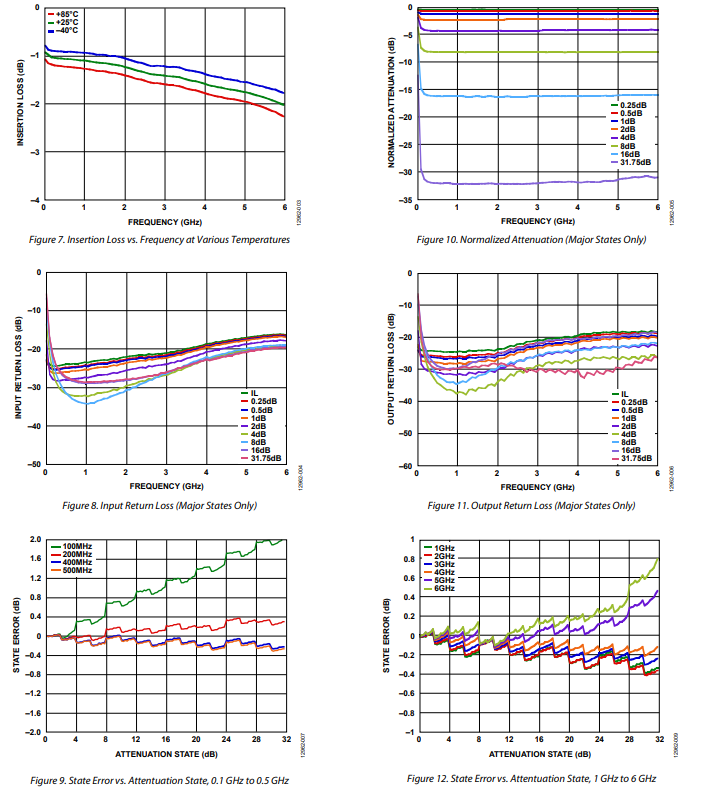

典型性能特征

工作原理

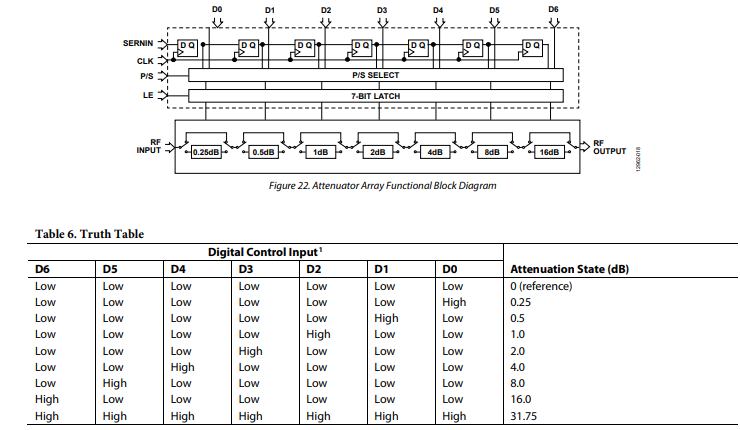

HMC1119集成了一个7位固定衰减器阵列,提供0.25 dB至31.75 dB的衰减范围,步进为0.25 dB。集成驱动器同时提供串行和并行模式控制衰减器阵列(见图22)。

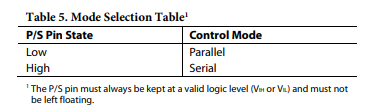

通过设置P/S引脚为高或低,HMC1119可处于串行或并行模式控制(见表5)。7位数据在相应模式下锁存,同时结合控制信号LE来确定衰减器值。

串行控制接口

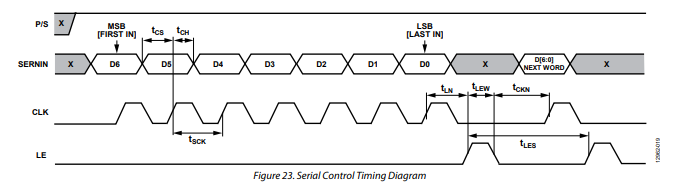

HMC1119采用三线串行转并行(SPI)配置,如串行模式时序图(见图23)所示:串行数据(SERNIN)在时钟(CLK)上升沿输入,使能(LE)设置为高电平时,串行控制接口激活。

在串行模式下,7位SERNIN数据在时钟CLK上升沿以最高有效位(MSB)优先的方式移入移位寄存器;然后,必须切换LE为高电平,将新的衰减器状态数据锁存到器件中。LE必须在时钟的7个状态下保持低电平,因为CLK被屏蔽,以防止在LE保持高电平时衰减器值发生变化。

在串行模式操作中,串行控制输入(LE、CLK、SERNIN)和并行控制输入(D0至D6)都必须保持在有效逻辑电平(VOH 或 VOL ),且不得悬空。建议将并行控制输入接地,并在所有串行控制输入线上使用下拉电阻,如果在休眠期间这些输入线变为高阻态。

射频输出

HMC1119中的衰减器是双向的;ATTNIN和ATTNOUT引脚可与射频输入和输出互换。该衰减器在50Ω输入和输出端均内部匹配,因此不需要外部匹配元件。射频引脚是交流耦合的,因此在射频线路上不需要直流阻断电容。

并行控制接口

并行控制接口有七条数字控制输入线(D6 至 D0)用于设置衰减值。D6 是最高有效位(MSB),用于选择 16 dB 衰减级,D0 是最低有效位(LSB),用于选择 0.25 dB 衰减级(见图 22)。

在并行模式操作中,串行控制输入(LE、CLK、SERNIN)和并行控制输入(D0 至 D6)都必须保持在有效逻辑电平(VOH 或 VOL ),且不得悬空。建议将串行控制输入接地,并在所有并行控制输入线上使用下拉电阻,如果驱动这些输入线的器件在休眠期间变为高阻态。

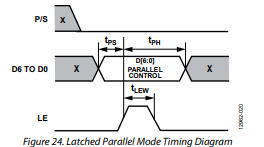

将 P/S 设置为低电平可启用并行模式。并行操作有两种模式:直接并行模式和锁存并行模式。

- 直接并行模式 :对于直接并行模式,锁存使能(LE)引脚必须保持高电平。使用控制电压输入(D0 至 D6)直接更改衰减状态。此模式最适合手动控制衰减器,以及使用硬件、开关或跳线的情况。

- 锁存并行模式 :更改控制电压输入(D0 至 D6)以设置衰减状态时,锁存使能(LE)引脚必须为低电平。当达到所需状态时,必须切换 LE,将 7 位数据传输到旁路开关的衰减器阵列,然后切换为低电平,将更改锁存到器件中(见图 24)。

上电顺序

理想的上电顺序如下:

- 给 GND 上电。

- 给 VDD 上电。

- 给数字控制输入上电(数字控制输入的相对顺序不重要)。

- 给 RF 输入上电。

对于锁存并行模式操作,必须切换 LE。只要在 GND 和 VDD 之后为输入供电,数字输入的相对顺序就不重要。

上电状态

上电时,若 LE 设置为低电平,器件的逻辑状态为最大衰减。上电后约 200 ms,衰减器将锁存所需的上电状态。

-

解析HMC1122:0.1 GHz至6.0 GHz 6位数字衰减器的卓越性能与应用2026-03-02 353

-

0.1-3.0 GHz 四位数字衰减器 (1 dB LSB) skyworksinc2025-05-26 170

-

HMC1122 0.1GHz至6.0 GHz、0.5 dB LSB、6位硅数字衰减器技术手册2025-04-24 1529

-

HMC470A:0.1 GHz至3 GHz,1 dB LSB,5位,GaAs数字衰减器数据表2021-05-18 806

-

HMC624A:0.1 GHz至6.0 GHz,0.5 dB LSB,6位,GaAs数字衰减器数据表2021-05-14 966

-

HMC1019ALP4E:0.5 dB LSB GaAs MMIC 5位数字衰减器,0.1-30 GHz初步数据表2021-04-27 779

-

HMC1018ALP4E:1.0 dB LSB GaAs MMIC 5位数字衰减器,0.1-30 GHz初步数据表2021-04-25 853

-

HMC539ALP3E:0.25 dB LSB GaAs MMIC 5位数字正向控制衰减器,直流至4 GHz数据表2021-04-24 804

-

ADH939S:航空航天0.1 GHz至40 GHz,GaAs,MMIC,5位1.0 dB LSB,数字衰减器数据表2021-04-20 746

-

ADH941S:航空0.1 GHz至30 GHz,GaAs,MMIC,5位0.5 dB LSB,数字衰减器数据表2021-04-18 716

-

HMC1119 0.25dB LSB、7位硅数字衰减器,0.1 GHz至6.0 GHz2019-02-22 604

全部0条评论

快来发表一下你的评论吧 !