ADRF5715硅数字衰减器,1位,1MHz至30GHz技术手册

描述

概述

ADRF5715 是一款 1 位数字硅工艺衰减器,衰减率为 16 dB。

ADRF5715 的工作频率范围为 1 MHz 至 30 GHz,具有优于 1.15 dB 的插入损耗和出色的衰减精度。ADRF5715 的 ATTIN 和 ATTOUT 端口的射频功率处理能力为 30 dBm 稳态平均值和 33 dBm 稳态峰值。

ADRF5715 需要 +3.3 V 和 −3.3 V 的双电源电压。此套件采用互补金属氧化物半导体 (CMOS)-/低电压晶体管至晶体管逻辑 (LVTTL) 兼容控制。

ADRF5715 也可以使用单个正电源电压 (V DD ) 下工作,同时负电源电压 (VSS) 接地。有关更多详细信息,请参见“工作原理”部分。

ADRF5715 射频端口旨在匹配 50 Ω 的特性阻抗。ADRF5715 采用符合 RoHS 标准的 12 端子、2.25 mm × 2.25 mm、LGA 封装, 并可在 −40°C 至 +105°C 的温度范围内工作。

数据表:*附件:ADRF5715硅数字衰减器,1位,1MHz至30GHz技术手册.pdf

应用

- 工业扫描仪

- 测试和仪器仪表

- 蜂窝基础设施:5G 毫米波

- 军用射频、雷达和电子对抗措施 (ECM)

- 微波射频和甚小孔径终端 (VSAT)

特性

- 超宽带频率范围:1 MHz 至 30 GHz

- 衰减范围:16 dB(典型值)

- 低插入损耗

- 0.6 dB (8 GHz)

- 0.8 dB (18 GHz)

- 1.15 dB (30 GHz)

- 衰减精度

- ±0.15 dB 典型值,最高 18 GHz

- 18 GHz 至 30 GHz:±0.20 dB(典型值)

- 高输入线性度

- P0.1dB 插入损耗状态:33 dBm(典型值)

- P0.1dB 16 dB 衰减状态:30 dBm(典型值)

- IP3 插入损耗路径:51 dBm(典型值)

- IP3 16 dB 衰减状态:49 dBm(典型值)

- 高 RF 功率处理能力

- ATTIN 和 ATTOUT 的输入

- 30 dBm(典型值)稳态平均值

- 33 dBm(典型值)稳态峰值

- ATTIN 和 ATTOUT 的输入

- RF 幅度建立时间(0.1 dB 最终 RF

OUT):6.5 μs(典型值) - 支持单电源工作

- 在相对相位中紧密分布

- 无低频杂散信号

- 与 CMOS/LVTTL 兼容

- 12 端子 2.25 mm x 2.25 mm 岸面栅格阵列 (LGA) 封装

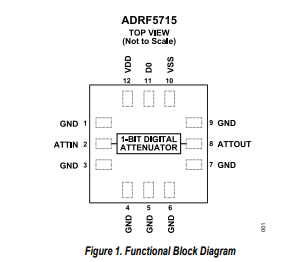

框图

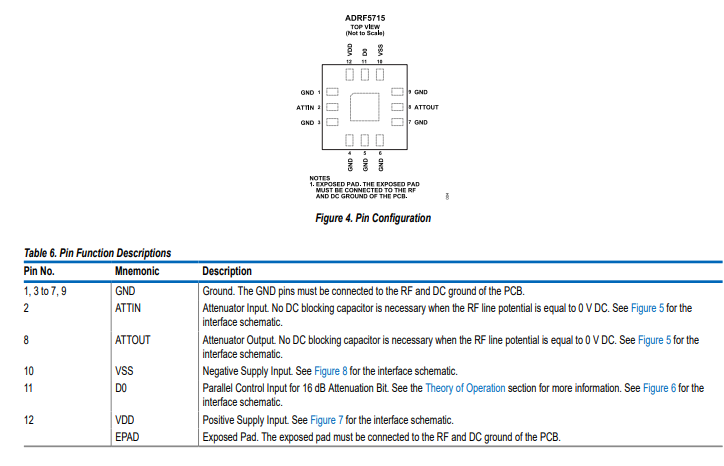

引脚配置描述

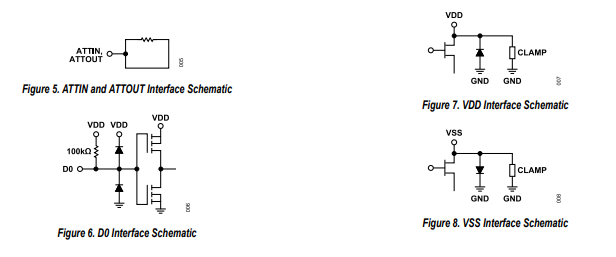

接口示意图

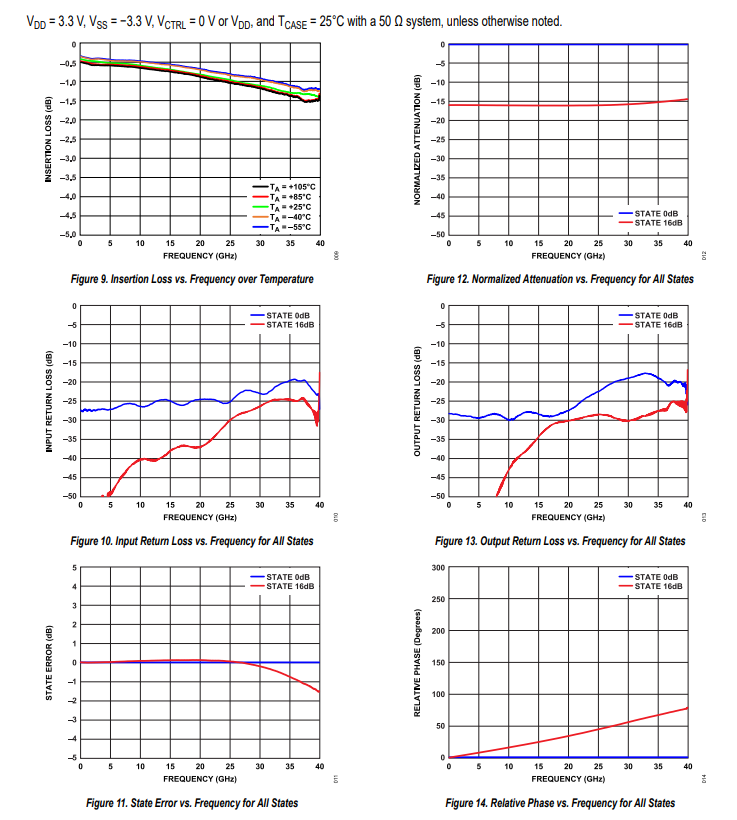

典型性能特征

应用信息

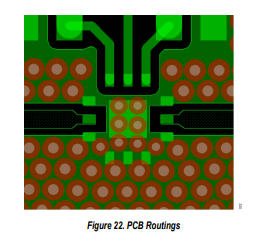

射频传输线采用共面波导(CPWG)模型设计,走线宽度为16密耳,接地间距为6密耳,特性阻抗为50Ω。为实现最佳射频和热接地效果,在传输线周围以及封装裸露焊盘下方尽可能多地布置了过孔。

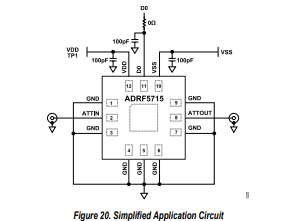

射频输入和输出端口(ATTIN和ATTOUT)通过50Ω传输线连接。在VDD和VSS电源走线上,一个100 pF的旁路电容可滤除高频噪声。图20展示了ADRF5715的简化应用电路。

印刷电路板(PCB)设计建议

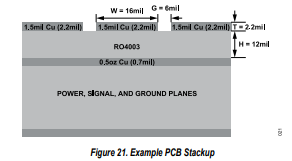

射频端口内部已匹配至50Ω,引脚布局设计用于与印刷电路板上具有50Ω特性阻抗的共面波导相匹配。图21展示了基于12密耳厚Rogers RO4003介电材料的推荐CPWG走线设计。对于2.2盎司成品铜厚,建议采用16密耳宽的射频走线和6密耳的间距。

图22展示了ADRF5715的射频走线、电源和控制信号的布线情况。接地层通过尽可能多的填充过孔连接,以实现最佳射频和热性能。器件的主要散热焊盘与底层相连。

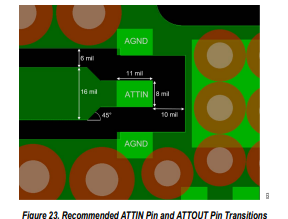

图23展示了从ADRF5715的ATTIN和ATTOUT引脚到参考叠层上50Ω CPWG的推荐布局。PCB焊盘按1:1比例绘制,与器件焊盘对应。接地焊盘采用阻焊层定义,信号焊盘采用焊盘定义。从PCB焊盘引出的射频走线宽度为2密耳,并以90°角逐渐变细。助焊层也经过设计,可与焊盘匹配,且不减小开口尺寸。助焊层被划分为多个开口,以适应焊盘。

对于具有不同介电厚度和CPWG设计的其他PCB叠层,请联系亚德诺半导体技术支持获取进一步建议。

-

Analog Devices Inc. ADRF5714硅数字衰减器数据手册2025-06-10 1164

-

Analog Devices Inc. ADRF5717硅数字衰减器数据手册2025-06-09 1095

-

GaAs 数字衰减器 5 位、1 dB LSB 400 MHz-4 GHz skyworksinc2025-05-26 116

-

ADRF5714硅数字衰减器,1位,100MHz至30GHz技术手册2025-04-23 1490

-

ADRF5715: 硅数字加速器,1-比特,1兆赫至30千兆赫初步数据表 ADI2023-10-09 55

-

UG-1831:评估ADRF5740 2 dB LSB、4位、硅数字衰减器,10 MHz至60 GHz2021-04-14 710

全部0条评论

快来发表一下你的评论吧 !