ADF4382集成VCO的微波宽带频率合成器技术手册

描述

概述

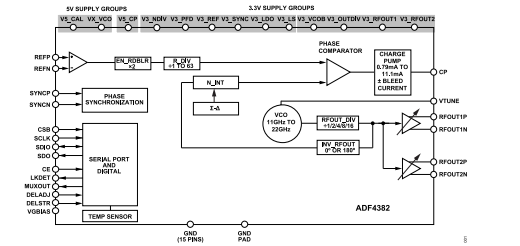

ADF4382 是一款高性能、超低抖动、小数 N 分频锁相环 (PLL),带有集成电压控制振荡器 (VCO),非常适合 5G 应用或数据转换器时钟应用的本地振荡器 (LO) 生成。高性能 PLL 具有 −239 dBc/Hz 的品质因数、低 1/f 噪声和整数模式下 625 MHz 的高 PFD 频率,可实现超低带内噪声和综合抖动。ADF4382 可产生 11 GHz 至 22 GHz 基本倍频范围内的频率,从而无需使用次谐波滤波器。ADF4382 上的输出分频器可产生从 687.5 MHz 至 22 GHz 的完整输出频率范围。

对于多数据转换器时钟应用,ADF4382 通过在 PLL 反馈环路中包含输出分频器,自动将其输出与输入参考边沿对齐。对于需要确定性延迟或延迟调整功能的应用,提供分辨率 <1 ps 的可编程输出延迟参考。保证在多个套件和温度范围内参考输出延迟,从而实现可预测和精确的多芯片对齐。

ADF4382 框图十分简单,通过简化的串行外设接口 (SPI) 寄存器映射、外部 SYNC 输入以及整数和小数模式下可重复的多芯片对齐,可以缩短开发时间。

数据表:*附件:ADF4382集成VCO的微波宽带频率合成器技术手册.pdf

应用

- 高性能数据转换器时钟

- 无线基础设施(MC-GSM、5G、6G)

- 测试和测量

特性

- 输出频率范围:687.5 MHz 至 22 GHz

- 20 GHz 时的积分 RMS 时基误差 = 20 fs(积分带宽:100 Hz 至 100 MHz)

- 20 GHz 时的积分 RMS 时基误差 = 31 fs(ADC SNR 方法)

- VCO 快速校准时间 < 1 μs

- VCO 自动校准时间 < 100μs

- 相位本底噪声:20 GHz 时为 −156 dBc/Hz

- PLL 规格:

- -239 dBc/Hz:归一化带内相位本底噪声

- -287 dBc/Hz:归一化带内 1/f 噪声

- 625 MHz 最大相位/频率检测器输入频率

- 4.5 GHz 参考输入频率

- 典型杂散 f

PFD:−90 dBc - 基准输出延迟规格

- 传播延迟温度系数:0.06 皮秒/℃

- 调整步长:<1 ps

- 多芯片输出相位对齐

- 3.3V 和 5V 电源

- ADIsimPLL™环路滤波器设计工具支持

- 7 mm × 7 mm, 48 端子 LGA

- 工作温度为 −40°C 至 +105°C

框图

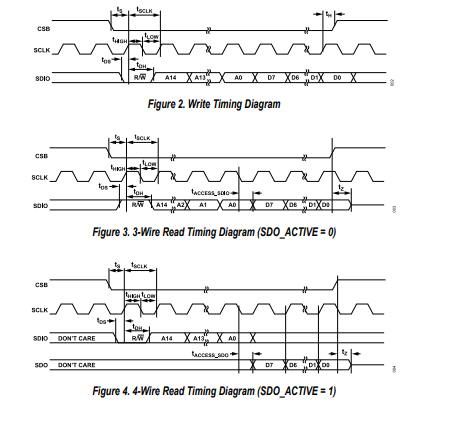

串行接口时序图

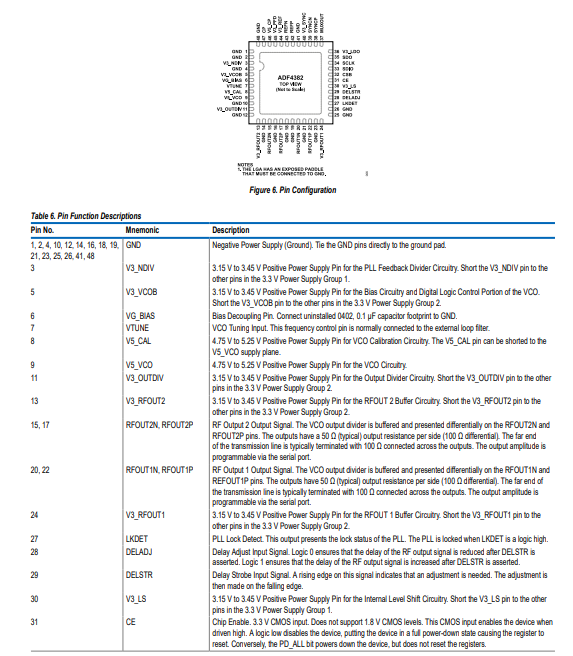

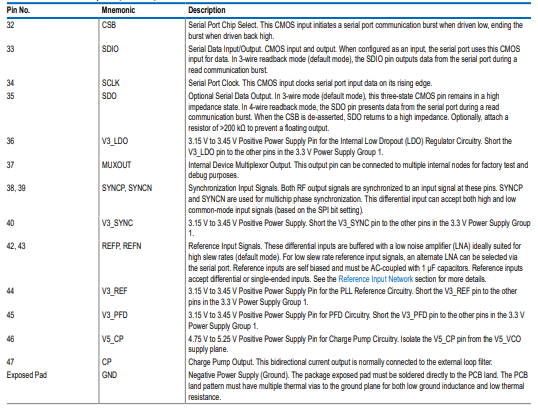

引脚配置描述

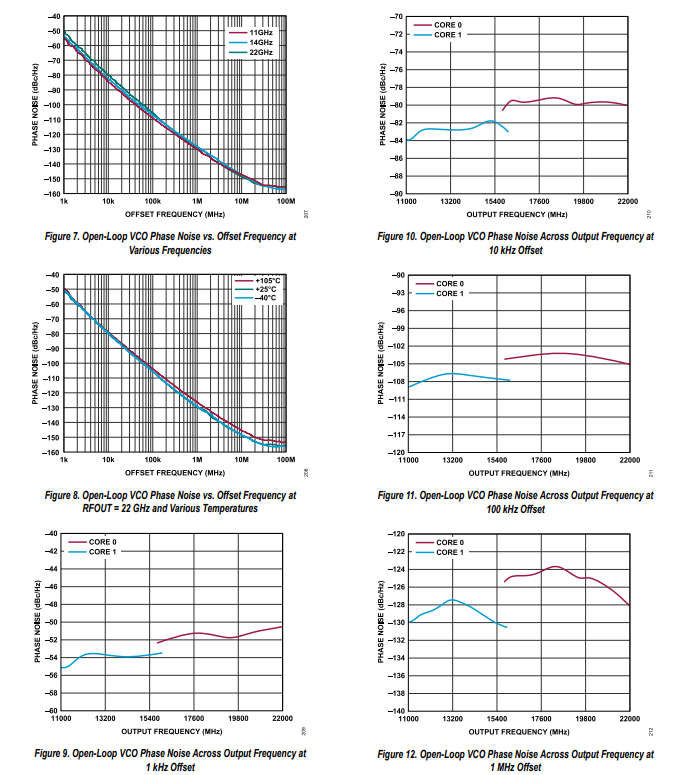

典型性能特征

参考源考量

参考输入网络

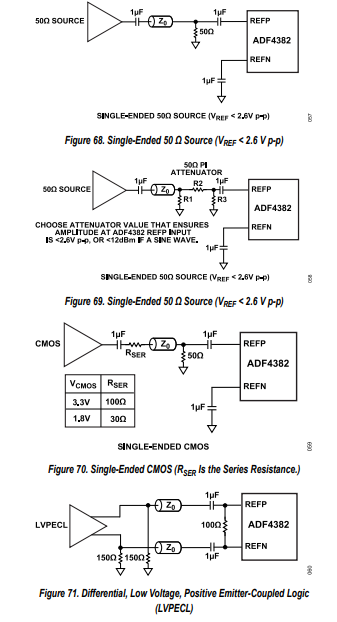

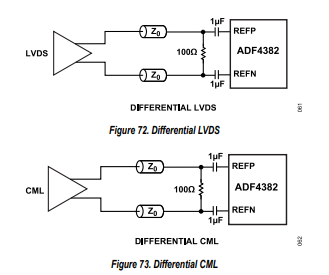

图51所示的ADF4382参考输入缓冲器为差分或单端频率源提供了灵活的接口。图68至图73展示了不同参考信号类型的推荐接口。所有特征阻抗(Z_0)信号迹线均为50Ω传输线。

参考相位噪声

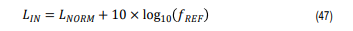

ADF4382在整数模式下实现的带内归一化相位噪声底为L_{NORM} = -239dBc/Hz,在分数模式下为L_{NORM} = -237dBc/Hz 。要计算等效输入相位噪声底(L_{IN}),请使用以下公式:

例如,100MHz的参考输入频率在分数模式下得到的**L_{IN}为 -157dBc/Hz。参考频率源的相位噪声必须比L_{IN}至少低6dB,以避免影响并增加整个系统的相位噪声。

为保持典型的L_{NORM}**性能,表7根据输入参考信号类型和幅度,提供了选择最佳REF_SEL(寄存器0x030,第5位)设置的标准。

-

ADF4371微波宽带合成器:特性、应用与设计要点2026-04-20 53

-

ADF5611集成VCO的微波宽带频率合成器技术手册2025-04-27 1172

-

ADF4372带集成VCO的微波宽带频率合成器技术手册2025-04-25 1480

-

ADF5612集成VCO的微波宽带频率合成器技术手册2025-04-24 1314

-

ADF4377 微波宽带合成器和集成VCO数据表 ADI2023-10-11 313

-

ADF4368:微波宽带合成器和集成VCO数据表 ADI2023-10-10 385

-

ADF435微波宽带频率合成器资料分享2022-07-23 891

全部0条评论

快来发表一下你的评论吧 !