ADF4368集成VCO的微波宽带技术手册

描述

概述

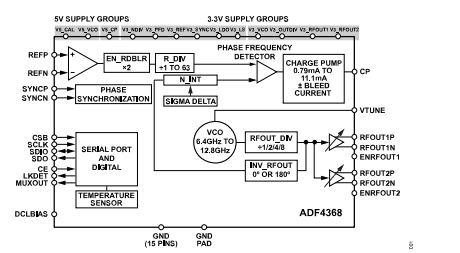

ADF4368 是一款集成 VCO 的高性能、超低抖动、整数 N 分频和小数 N 分频锁相环 (PLL),非常适合频率转换应用。

高性能 PLL 具有 −239dBc/Hz、超低 −287dBc/Hz 归一化 1/f 噪声和高 PFD 频率,可实现超低带内噪声和集成抖动性能。无需内部倍频器,ADF4368 可生成 800MHz 至 12.8GHz 范围内的任意频率,因而无需子谐波滤波器。Σ-Δ 调制器包括支持赫兹频率分辨率的 25 位固定模数和额外的 17 位可变模数,该模数支持更高的分辨率,可实现灵活的频率规划。该套件在单端配置下具有 9dBm (12.8GHz) 输出功率和 16 步进功率调整特性,非常适合各种应用。

对于相控阵雷达或大规模 MIMO 系统等多个频率转换应用,可通过使用 SYNC 输入或 EZSync^™^ 对齐多个 ADF4368 的输出。当难以将 SYNC 信号精确分配给所有套件时,将使用 EZSync 方法。对于需要确定性延迟或延迟调整功能的应用,提供分辨率 <1ps 的可编程输出延迟参考。保证在多个套件和温度范围内参考输出延迟,从而实现可预测和精确的多芯片对齐。

在整数和小数模式下,简单的 ADF4368 结构框图通过简化的串行外围接口 (SPI) 寄存器映射、外部 SYNC 输入和可重复多芯片相位对齐功能,缩短了开发时间。

数据表:*附件:ADF4368集成VCO的微波宽带频率合成器技术手册.pdf

应用

- 无线基础设施(MC-GSM、5G)

- 测试和测量

- 航空航天和防务

特性

- 输出频率范围:800MHz 至 12.8GHz

- 抖动 < 30 fs

RMSfOUT= 9.001GHz、fREF= fPFD= 250MHz,小数模式 - 宽带本底噪声:12.8GHz 时为 −160dBc/Hz

- PLL 规格

- 归一化带内相位本底噪声

- −239dBc/Hz:整数,−237dBc/Hz:小数模数

- 归一化 1/f 相位噪声:

- −287dBc/Hz:归一化为 1Hz

- −147dBc/Hz:10kHz 时归一化为 1GHz

- 625MHz 鉴相器频率整数模式

- 250MHz 鉴相器频率小数模式

- 25 位固定/49 位组合小数模数

- 4GHz 基准输入频率

- 典型 −95dBc PFD 杂散

- 归一化带内相位本底噪声

- 基准输出延迟规格

- 温度系数:0.06 ps/°C

- 调整步长:<1ps

- 多芯片输出相位对齐

- 通过 SYNC 引脚或 EZSync 方法

- 3.3V 和 5V 电源

- 支持 ADIsimPLL^™^ 环路滤波器设计工具

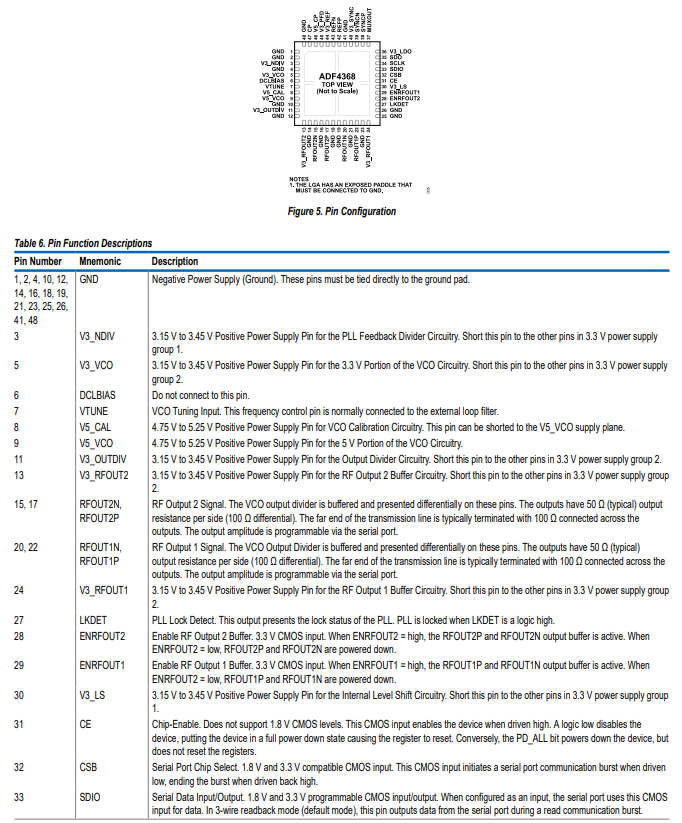

- 采用 48 引脚 7mm × 7mm LGA 封装

- 工作结温范围:−40°C 至 +125°C

框图

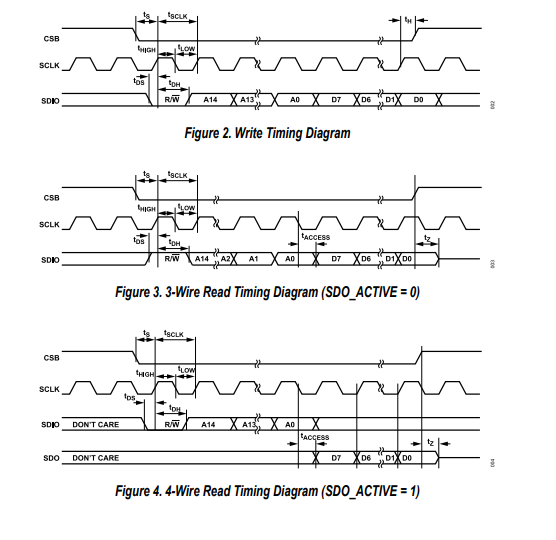

时序图

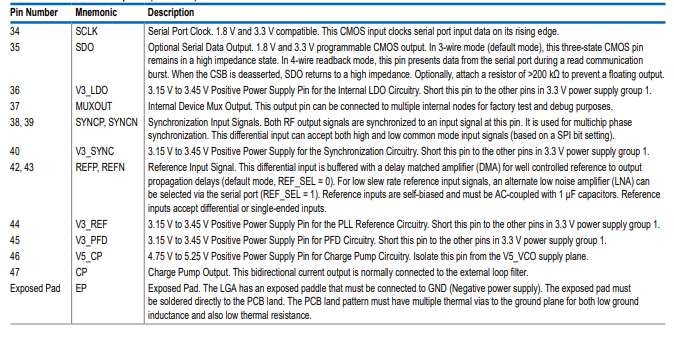

引脚配置描述

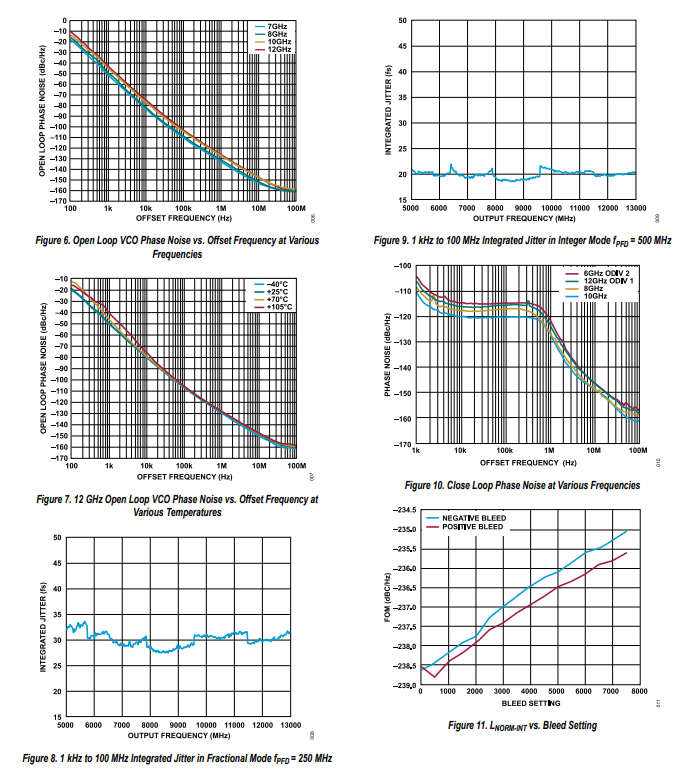

典型性能特征

应用信息

环路滤波器设计

稳定的环路滤波器设计需要精心选择ADF4368的环路滤波器组件。建议下载并安装适用于环路滤波器设计和仿真的ADIsimPLL™ 。它为首次使用者提供了综合教程,还有一个帮助手册,用于更复杂的主题。此外,还有多个ADIsimPLL培训视频可在www.analog.com观看。由于环路滤波器是经过设计和仿真的,建议使用ADF4368评估硬件来验证新的环路滤波器。

完整的环路滤波器设计教程超出了本数据手册的范围。不过,以下列出了一些最佳实践,在仿真这些参数时会显示出来。对这些项目的任何重大更改都需要重新设计环路滤波器。

一个稳定的环路滤波器必须满足以下标准:

- 环路滤波器相位裕度 > 45°

- 环路滤波器带宽 < f_{PFD} / 10

所需的环路滤波器带宽由ADF4368的以下特性决定:

- f_{CP}

- K_{VCO}

- PFD频率

- 参考输入相位噪声(见“参考相位噪声”部分)

- 在最小化抖动或建立时间之间进行权衡(分别见“输出相位噪声特性”部分和公式12)

VTUNE引脚内部有一个30pF的接地电容,在环路滤波器设计中必须考虑这一因素。ADIsimPLL™ 会自动考虑这个内部电容。

参考源考量

参考输入网络

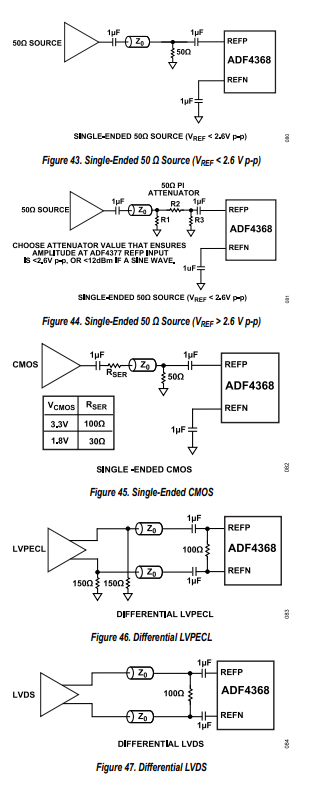

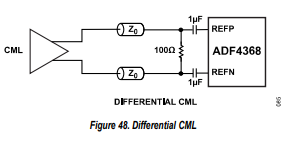

图34所示的ADF4368参考输入缓冲器为差分或单端频率源提供了灵活的接口。图43至图48展示了不同参考信号类型的推荐接口。所有Z_0信号迹线均为50Ω传输线,如图43、图44、图45、图46、图47和图48所示。

-

Analog Devices Inc. EV-ADF4368SD1Z评估板数据手册2025-06-13 888

-

ADF4383集成VCO的微波宽带频率合成器技术手册2025-04-27 925

-

ADF4382集成VCO的微波宽带频率合成器技术手册2025-04-25 1126

-

ADF5612集成VCO的微波宽带频率合成器技术手册2025-04-24 918

-

ADF4377带集成VCO的微波宽带频率合成器技术手册2025-04-09 812

-

ADF4377 微波宽带合成器和集成VCO数据表 ADI2023-10-11 291

-

ADF4368:微波宽带合成器和集成VCO数据表 ADI2023-10-10 300

全部0条评论

快来发表一下你的评论吧 !