ADF4401A转换环路、PLL、VCO模块技术手册

描述

概述

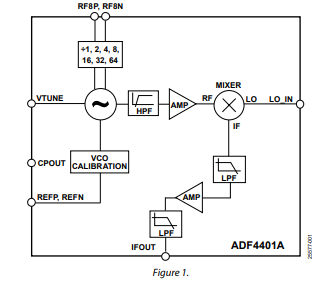

ADF4401A 是完全集成的系统级封装 (SiP) 转换环路(也称为偏移环路)模块,包括压控振荡器 (VCO) 和校准锁相环 (PLL) 电路。专为高度抖动敏感的应用而设计,与设计在印刷电路板 (PCB) 上的传统离散转换环路解决方案相比,该解决方案减少了电路板空间和复杂性。通过利用这种高度集成的解决方案以及封装电路和增强的隔离功能(可减少杂散元件),可以大大缩短产品上市时间。ADF4401A 为工程师提供了频率合成解决方案,可设计出具有高度竞争性的系统。

ADF4401A 需要一个外部鉴相器或相位频率检波器 (PFD) 和一个外部本地振荡器 (LO),以形成频率合成解决方案。

ADF4401A 在反馈环路中集成了下变频混频级,将环路增益设置为 1,并较大程度降低了带内相位噪声。通过将频率下变频级与 ADI 公司的低噪声、集成宽带 VCO 技术相结合,ADF4401A 可在 8 GHz 输出时,提供 9 fs rms 的宽带抖动性能。输出抖动性能在很大程度上取决于外部偏移 LO 的性能。

ADF4401A 模块使用内部 PFD 和 VCO 校准电路,来选择合适的 VCO 频段。用户可以禁用校准电路,并使用外部 PFD 闭合环路。所有片内寄存器均通过串行端口接口 (SPI) 进行控制。

数据表:*附件:ADF4401A转换环路、PLL、VCO模块技术手册.pdf

应用

- 仪器仪表和测量

- 自动测试设备

- 航空航天和防务

特性 - RF 输出频率范围:62.5 MHz 至 8000 MHz

- 8 GHz 输出时,RMS 抖动为 9 fs

- 6 GHz RF 输出时,输出功率为 17 dBm IF

- 90 dBc LO_IN 至 RF 输出

- 90 dBc 无杂散动态范围

- 低相位噪声、压控振荡器

- 可编程的 1、2、4、8、16、32 或 64 分频输出

- 3.3 V 模拟、数字和混频器电源

- 5 V 放大器和 VCO 电源

- RF 输出静音功能

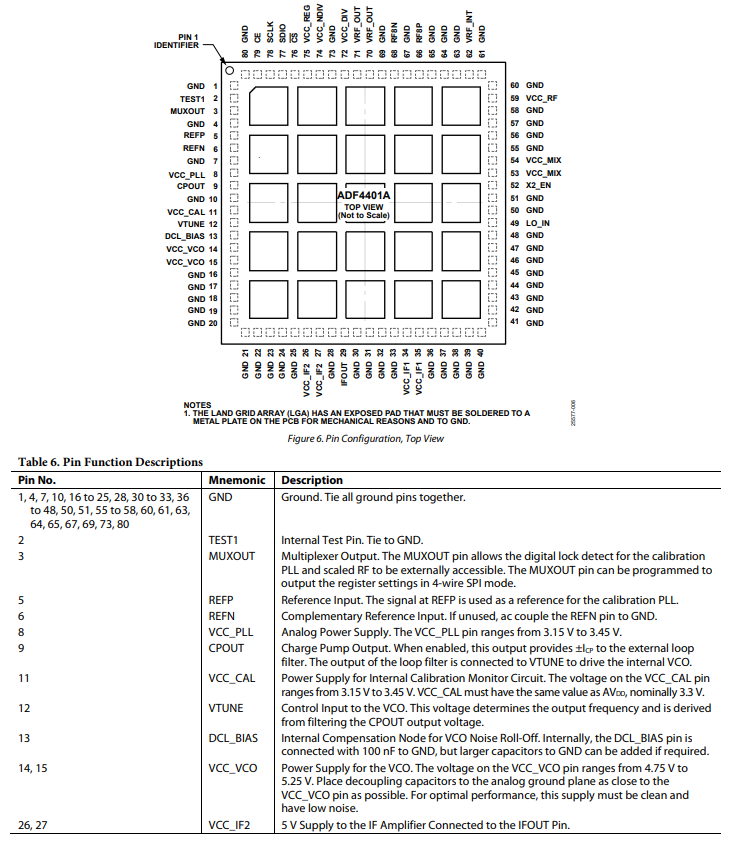

- 18.00 mm × 18.00 mm、80 端子 LGA_CAV

- 在[ADIsimPLL] 设计工具中提供支持

框图

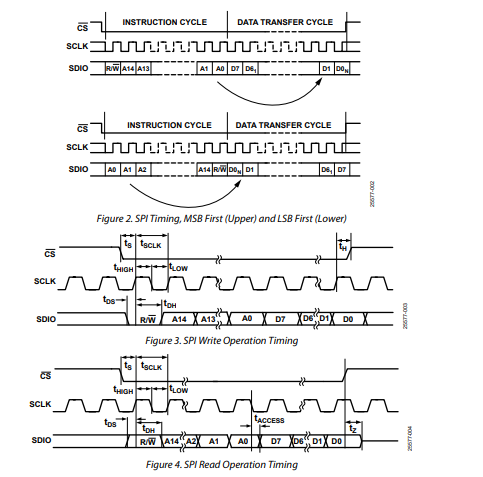

时序图

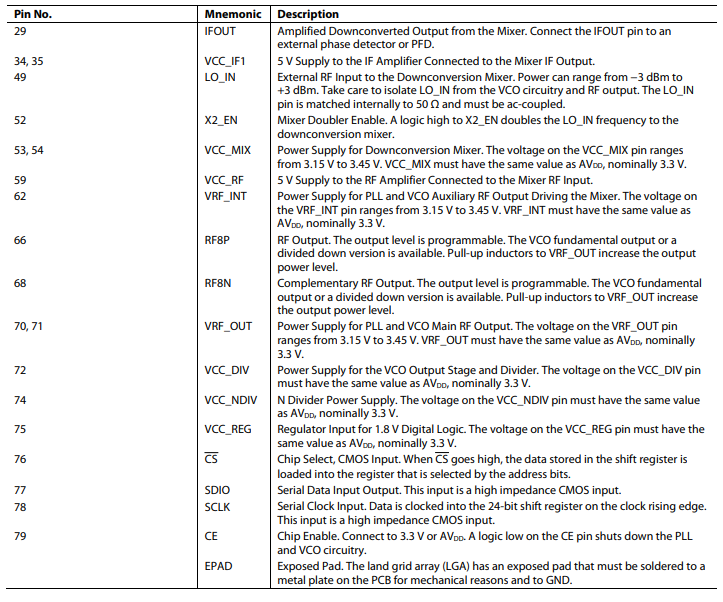

引脚配置描述

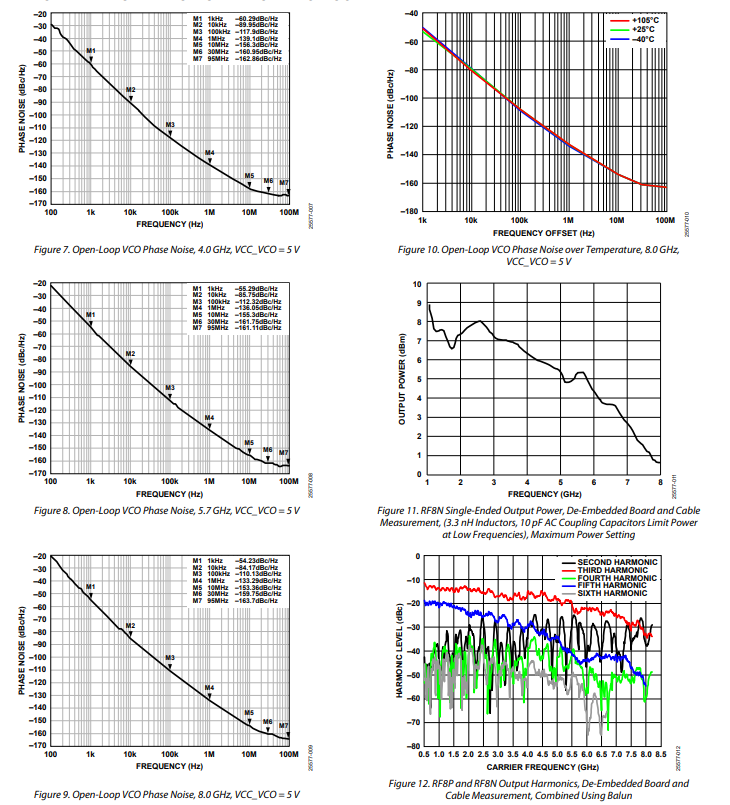

典型性能特征

工作原理

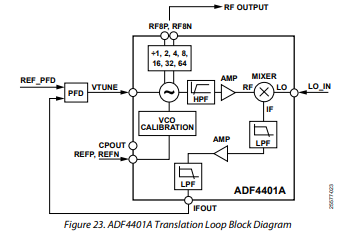

图23. ADF4401A 转换环路框图

ADF4401A是一款系统级封装(SiP)转换环路(偏移环路)模块,内含压控振荡器(VCO)及校准锁相环(PLL)电路、下变频混频器,以及R分频器和N分频器。该SiP将外部鉴频鉴相器(REF_PFD)的较低频率转换为4GHz至8GHz的较高频率范围,具体由LO_IN引脚决定。

锁相环(PLL)电路中的相位噪声可描述为包含两个部分:一个是平坦噪声部分,即PLL的噪声基底;另一个是1/f噪声部分,即PLL的1/f噪声。N分频器值较低的PLL电路能让用户设计出相应低相位噪声性能的频率合成器。更多信息请参见“射频N分频器”部分。

转换环路合成器将所需的信道间隔与N分频器值解耦,以优化PLL的相位噪声。如图23所示,ADF4401A锁定4GHz至8GHz射频输出频率范围中较高的频率,该频率为外部REF_PFD频率的整数倍。集成混频器和LO_IN引脚执行该PLL电路的分频功能。集成射频放大器提供所需的射频隔离,中频(IF)放大器提供所需的外部IFOUT电平。

由于本振(LO)在反馈环路中,外部鉴频鉴相器(PFD)的公式如下(适用于高边注入,即IF = LO - RF):

[ REF_PFD/R=(LO_IN - RF8x)/N ]

其中:

- R 是R分频器。

- N 是N分频器。

对于低边注入(即IF = RF - LO):

[ REF_PFD/R=(RF8x - LO_IN)/N ]

在本电路中,R 和 N 均为1。因此,输出频率为:

[ RF8x = LO_IN pm REF_PFD ]

-

ADF4401A:高性能集成式频率合成解决方案2026-04-20 88

-

ADF4155整数N/小数N分频PLL频率合成器技术手册2025-04-25 1250

-

EVAL-ADF4401A EVAL-ADF4401A评估板2021-07-09 404

-

UG-1922: Evaluating the ADF4401A Translation Loop, PLL, VCO Module2021-01-27 742

-

EV-ADF411xSD1Z用于评估ADF411x整数N和小数N分频PLL频率合成器2019-07-15 1880

-

基于高压VCO的高性能PLL设计2019-06-26 1955

-

用于ADF41020 PLL频率合成器的评估板EV-ADF41020EB1Z2019-02-28 2542

-

集成VCO的PLL常见问题解答2019-01-16 2555

-

PLL的电源管理设计2018-12-21 2094

-

用于无线应用的集成PLL和VCO2018-10-26 2445

-

请问能否给我一个adf4159数据手册上的环路滤波器仿真?2018-08-14 2105

-

请问ADF9010使用内部VCO,PLL无法锁定2018-07-27 1966

-

集成低噪声VCO的ADF4350系列PLL之特性和应用2012-06-08 3389

全部0条评论

快来发表一下你的评论吧 !