ADF4356集成VCO的6.8 GHz宽带频率合成器技术手册

描述

概述

ADF4356结合外部环路滤波器和外部参考频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。其他频率输出的一系列分频器可实现53.125 MHz至6800 MHz的工作频率。

ADF4356具有集成VCO,其基波输出频率范围为3400 MHz至6800 MHz。此外,VCO频率可进行1、2、4、8、16、32或64分频,因此用户可以产生低至53.125 MHz的RF输出频率。对于要求隔离的应用,RF输出级可以实现静音。静音功能既可以通过引脚控制,也可以通过软件控制。

所有片内寄存器均通过简单的三线式接口进行控制。ADF4356采用3.15 V至3.45 V的模拟和数字电源工作,并带有4.75 V至5.25 V的电荷泵和VCO电源。此外,ADF4356还内置硬件和软件掉电模式。

数据表:*附件:ADF4356集成VCO的6.8 GHz宽带频率合成器技术手册.pdf

应用

- 无线基础设施(LTE、W-CDMA、TD-SCDMA、WiMAX、GSM、PCS、DCS)

- 点到点/点到多点微波链路

- 卫星/VSAT

- 测试设备/仪器仪表

- 时钟产生

特性

- RF输出频率范围:53.125 MHz至6800 MHz

- 整数通道:−227 dBc/Hz

- 小数通道:-225 dBc/Hz

- 集成RMS抖动(1 kHz至20 MHz):6 GHz输出为97 fs

- 小数N分频频率合成器和整数N分频频率合成器

- 与[ADF4355]引脚兼容

- 高分辨率、52位模数

- 工作频率高达125 MHz的鉴频鉴相器(PFD)

- 参考输入频率达600 MHz

- 在−40°C至+85°C范围内维持锁频

- 低相位噪声电压控制振荡器(VCO)

- 可编程1、2、4、8、16、32或64分频输出

- 模拟和数字电源:3.3 V

- 电荷泵和VCO电源:5.0 V(典型值)

- 逻辑兼容性:1.8 V

- 可编程输出功率水平

- RF输出静音功能

- [ADIsimPLL]设计工具支持

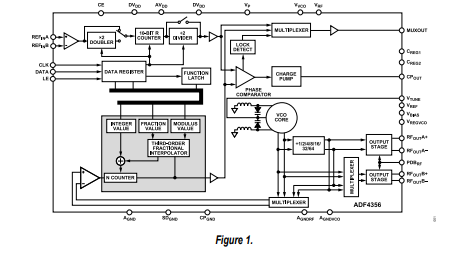

框图

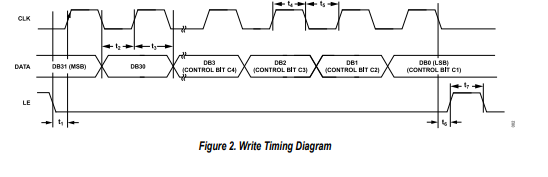

写时序图

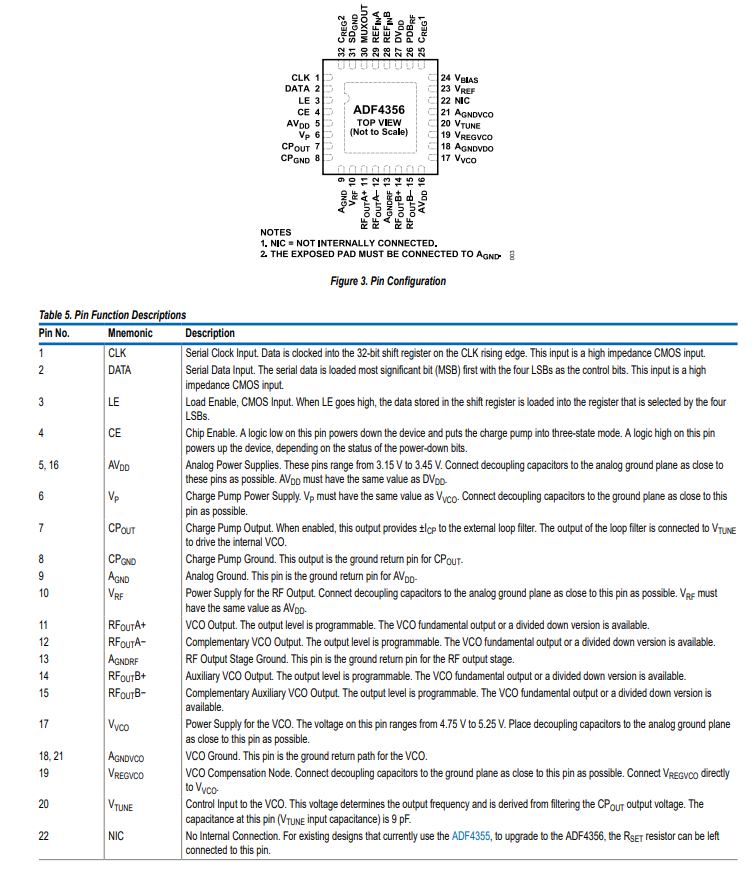

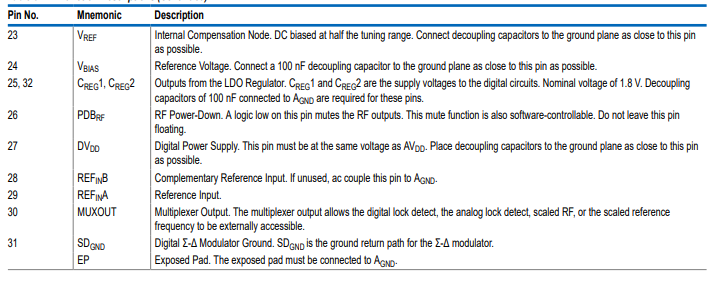

引脚配置描述

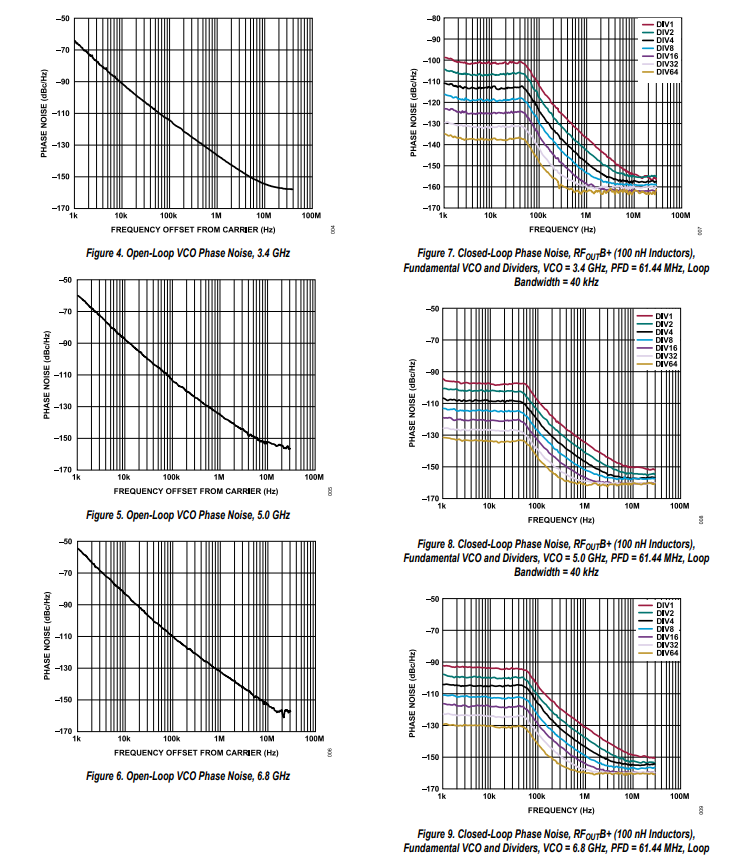

典型性能特征

参考输入部分

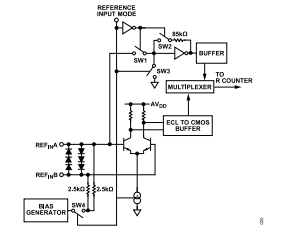

图20展示了参考输入级。该参考输入可接收单端和差分信号。使用参考模式位(寄存器4中的Bit9)来选择信号。若要使用差分信号作为参考输入,需将该位设为高电平。此时,SW1和SW2断开,SW3和SW4闭合,驱动差分对晶体管的电流源开启。差分信号经过缓冲后,以发射极耦合逻辑(ECL)形式提供给CMOS转换器。当使用单端信号作为参考信号时,将寄存器4中的Bit9设为0。将单端参考信号连接到REFIN_A引脚。此时,SW1和SW2闭合,SW3和SW4断开,驱动差分对晶体管的电流源关闭。

图20. 参考输入级,差分模式

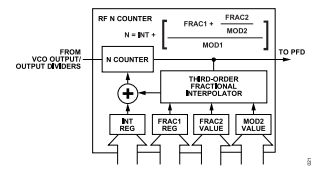

射频N分频器

射频N分频器可在锁相环(PLL)反馈路径中实现分频比。该分频比由INT、FRAC1、FRAC2和MOD2这些值决定。

图21. 射频N分频器

-

探索ADF4356:6.8 GHz宽带合成器的卓越性能与应用潜力2026-04-20 48

-

ADF4360-7集成式频率合成器和VCO技术手册2025-04-27 1310

-

ADF4372带集成VCO的微波宽带频率合成器技术手册2025-04-25 1482

-

ADF5612集成VCO的微波宽带频率合成器技术手册2025-04-24 1314

-

ADF4377 微波宽带合成器和集成VCO数据表 ADI2023-10-11 313

-

ADF4368:微波宽带合成器和集成VCO数据表 ADI2023-10-10 385

-

UG-1062:评估集成压控振荡器的ADF4356微波宽带合成器2021-05-22 716

-

ADF4356:集成压控振荡器数据表的6.8 GHz宽带合成器2021-05-11 946

-

ADF4356 集成VCO的6.8 GHz宽带频率合成器2019-02-22 1021

全部0条评论

快来发表一下你的评论吧 !