LTC6948具集成型VCO的超低噪声0.37GHz至6.39GHz分数N合成器技术手册

描述

概述

LTC6948 是一款具全集成型 VCO 的高性能、低噪声、6.39GHz 锁相环 (PLL),其包括一个基准分频器、相位-频率检测器 (PFD)、超低噪声充电泵、分数反馈分频器和 VCO 输出分频器。

分数分频器采用一个高级 4 阶 ΔΣ调制器,该调制器可提供异常低的杂散电平。这提供了很宽的环路带宽,从而能够产生极低的积分相位噪声值。

可编程 VCO 输出分频器 (分 1~6 级) 扩展了输出频率范围。

数据表:*附件:LTC6948具集成型VCO的超低噪声0.37GHz至6.39GHz分数N合成器技术手册.pdf

应用

- 无线基站 (LTE、WiMAX、W-CDMA、PCS)

- 微波数据链路

- 军用及安全无线电

- 测试和测量

特性

- 具集成型 VCO 的低噪声分数 N PLL

- 无 ΔΣ 调制器杂散

- 18 位分数分母

- –226dBc/Hz 归一化带内相位噪声层

- –274dBc/Hz 归一化带内 1/f 噪声

- –157dBc/Hz 宽带输出相位噪声层

- 卓越的整数边界杂散性能

- 输出分频器 (1 至 6,50% 占空比)

- 输出缓冲器静噪

- 基准输入频率高达 425MHz

- 快速频率开关操作

- FracNWizard^™^ 软件设计工具支持

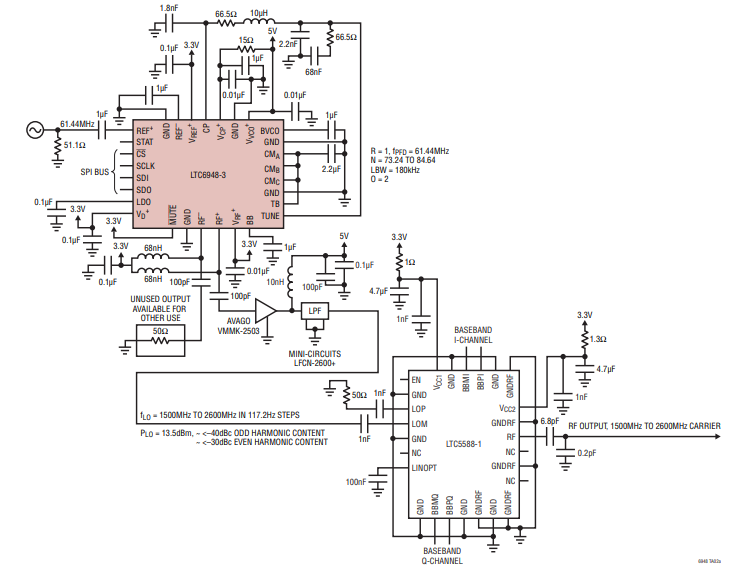

应用电路

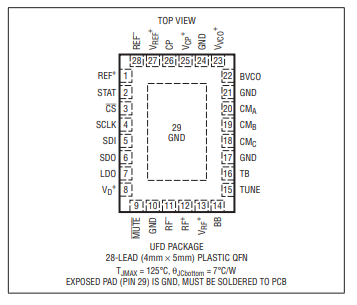

引脚配置描述

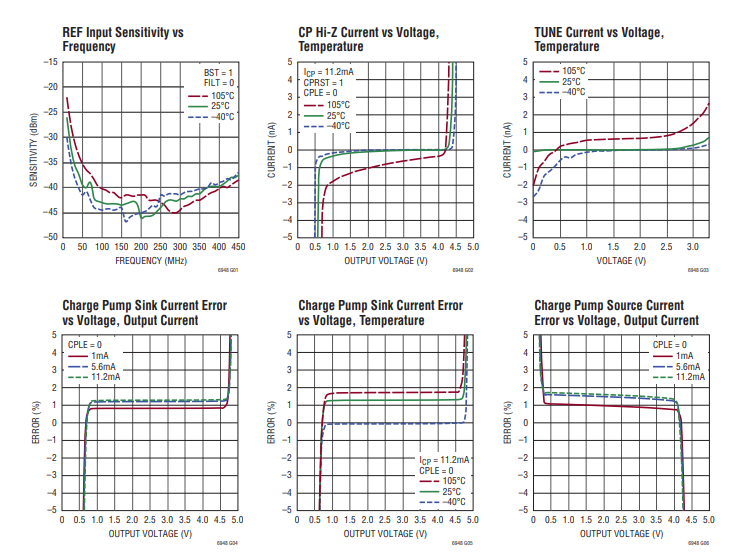

典型性能特征

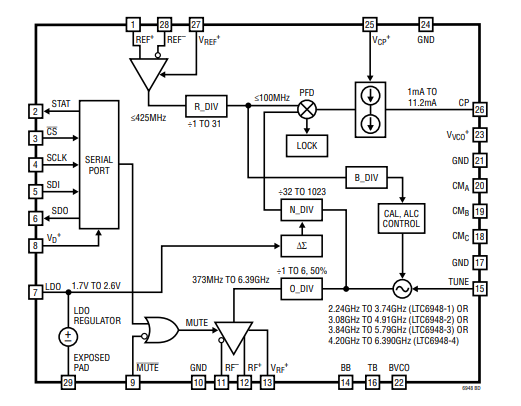

框图

工作原理

LTC6948是一款高性能分数N分频锁相环(PLL),配备低噪声压控振荡器(VCO),有四种不同频率范围可选。输出频率范围可通过使用输出分频器进一步扩展(详见“可用选项”表)。该器件通过其极低的带内相位噪声性能与出色的VCO噪声特性相结合,能够实现卓越的集成相位噪声性能。

分数N分频反馈分频器采用先进的Σ-Δ调制器,几乎不会产生离散调制器杂散音调。如果需要整数N分频反馈,可禁用该调制器。

参考输入缓冲器

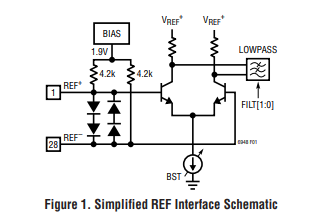

PLL的参考频率以差分方式施加于REF+和REF-引脚。这些高阻抗输入是自偏置的,必须通过1μF电容进行交流耦合(简化原理图见图1)。或者,可使用单端参考频率,方法是将REF-引脚通过1μF电容旁路至地。如果单端信号峰峰值大于2.7V,则使用47pF电容进行接地旁路。

必须向REF±输入施加高质量信号,因为它们为整个PLL提供频率参考。为实现器件的带内相位噪声性能,需向50Ω或500Ω负载施加峰峰值至少为6dBm的连续波(CW)信号,信号功率至少为4μVrms。

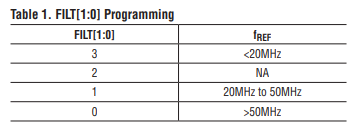

通过串行端口寄存器h0B可提供更多选项,以进一步优化应用。FILT1[1:0]位控制参考输入缓冲器的低通滤波器,并应根据fREF设置,以限制参考信号的宽带噪声。必须正确设置FILT1[1:0]位,以达到LNORM归一化带内相位噪声基底。推荐设置见表1。

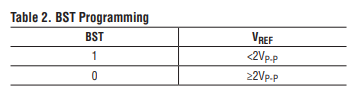

应根据输入信号电平设置BST位,以防止参考输入缓冲器饱和。推荐设置见表2,应用信息部分提供了编程示例。

参考(R)分频器

一个5位分频器R_DIV用于降低鉴频鉴相器(PFD)处的频率。其分频比R可设置为1到31(含)之间的任意整数。通过寄存器h06中的RD[4:0]位进行编程。有关R与fREF、fPFD、fVCO和fRF频率之间的关系,请参见应用信息部分。

鉴频鉴相器(PFD)

鉴频鉴相器(PFD)与电荷泵配合,产生与R和N分频器输出之间相位差成比例的源电流和灌电流脉冲。此操作提供了使反馈环路锁定所需的必要相位校正,从而实现相位对齐。

-

高性能低噪声锁相环LTC6948:设计与应用全解析2026-04-21 304

-

DC1959A-B 停产产品:LTC6948-2 演示板 | 具有集成化 VCO 的超低噪声和杂散 513MHz 至 4.91GHz 分数 N 合成器,(需要 DC590)2021-05-31 734

-

LTC6948:集成压控振荡器数据表的超低噪声0.37 GHz至6.39 GHz小数N合成器2021-05-13 1183

-

LTC6946:集成压控振荡器数据表的超低噪声和杂散0.37 GHz至6.39 GHz整数-N合成器2021-05-12 1075

-

LTC6947:超低噪声0.35 GHz至6 GHz小数N合成器数据表2021-05-10 852

-

DC1959B-D具有集成VCO的超低噪声和杂散小数N分频合成器2019-07-19 1335

-

DC1959A-A,采用LTC6948-1超低噪声和杂散整数N频率合成器2019-07-18 2182

-

DC1959B-C是具有集成VCO的超低噪声和杂散小数N分频合成器2019-07-17 2131

-

用于LTC6948IUFD-4超低噪声和杂散小数N分频合成器的演示板DC1959B-D2019-02-28 3389

-

LTC6948 具集成型 VCO 的超低噪声 0.37GHz 至 6.39GHz 分数 N 合成器2019-02-22 1398

全部0条评论

快来发表一下你的评论吧 !