ADF4153A小数N分频频率合成器技术手册

描述

概述

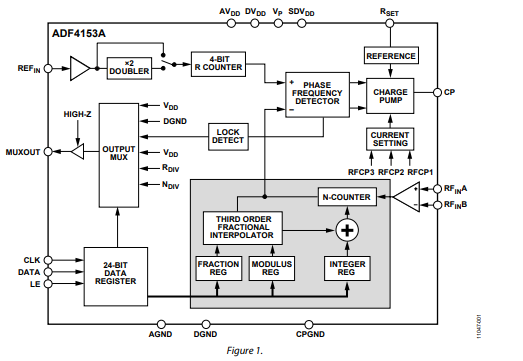

ADF4153A是一款小数N分频频率合成器,用来在无线接收机和发射机的上变频和下变频部分实现本振。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和可编程参考分频器组成。该器件内置一个Σ-Δ型小数插值器,能够实现可编程模数小数N分频。INT、FRAC和MOD寄存器可构成一个总N分频器(N = (INT + (FRAC/MOD)))。此外,4位参考分频器(R分频器)允许PFD输入端的REFIN频率为可选值。如果频率合成器与外部环路滤波器和电压控制振荡器(VCO)一起使用,则可以实现完整的锁相环(PLL)。

简单的三线式接口控制所有片内寄存器。该器件采用2.7 V至3.3 V电源供电,不用时可以关断。

数据表:*附件:ADF4153A小数N分频频率合成器技术手册.pdf

应用

- 有线电视设备

- 移动无线电通讯基站(GSM、PCS、DCS、WiMAX、 SuperCell 3G、CDMA、W-CDMA)

- 无线手机(GSM、PCS、DCS、CDMA、W-CDMA)

- 无线局域网(LAN)、PMR

- 通信测试设备

特性

- RF带宽达4 GHz

- 2.7 V至3.3 V电源供电

- 独立的电荷泵电源V

P可提供扩展的调谐电压 - 可编程小数模数

- 可编程电荷泵电流

- 三线式串行接口

- 模拟和数字锁定检测

- 省电模式

- 与ADF4106/ADF4110/ADF4111/ADF4112/ADF4113和ADF4153引脚兼容

- 稳定的RF输出相位

- 利用ADIsimPLL可实现环路滤波器设计

框图

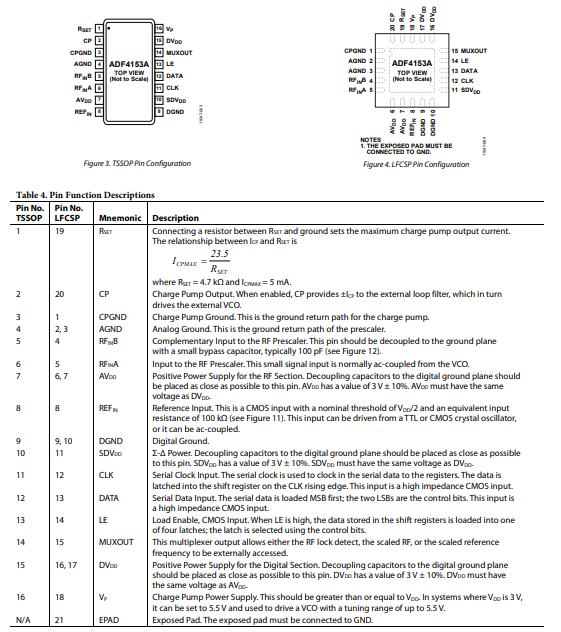

引脚配置描述

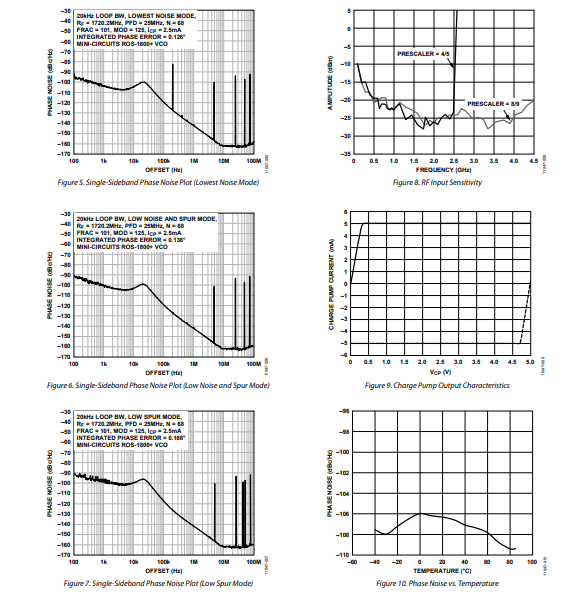

典型性能特征

应用信息

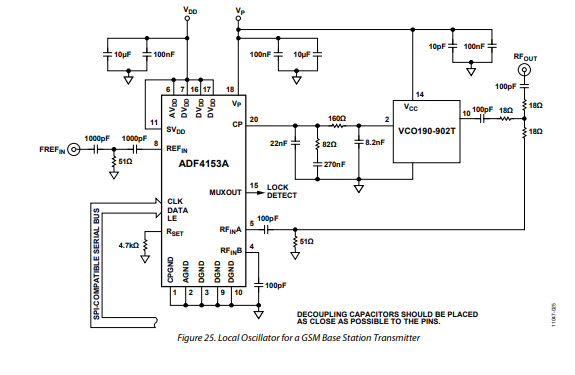

GSM基站发射机的本地振荡器

图25展示了与压控振荡器(VCO)配合使用的ADF4153A,用于产生GSM基站发射机的本地振荡器(LO)信号。

参考输入信号施加到电路的REF_{IN}引脚,在此情况下,端接50Ω负载。使用2.5MHz的参考信号,该信号直接馈入鉴频鉴相器(PFD)。为实现200kHz的信道间隔,MODULUS值必须设为125。选择MODULUS值为2、3或6,可避免杂散,具体见“杂散机制”部分以获取更多信息。

ADF4153A的电荷泵输出驱动环路滤波器。电荷泵电流I_{CP} = 5mA。使用ADIsimPLL工具计算环路滤波器参数,设计的环路带宽为20kHz,相位裕度为45°。

环路滤波器的输出驱动VCO,VCO的输出又反馈到射频输入的锁相环(PLL)合成器中。它还为合成器提供射频输出端接。电路设计在VCO输出、射频输出和**RF_{IN}**端之间实现50Ω匹配。

在PLL系统中,了解环路何时锁定非常重要。这可通过使用合成器的MUXOUT信号来实现。MUXOUT引脚可被编程为监测合成器内的各种内部信号,其中之一就是锁定检测信号。

-

ADF4153A 分数 N 频率合成器的全面解析与应用2026-04-20 243

-

无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器 skyworksinc2025-05-23 94

-

ADF4154小数N分频频率合成器技术手册2025-04-27 1458

-

ADF4169直接调制/快速波形产生13.5 GHz小数N分频频率合成器技术手册2025-04-25 1188

-

AN-1879小数N分频频率合成器2024-09-23 824

-

UG-485:ADF4153A小数N锁相环频率合成器评估板2021-05-16 1110

-

ADF4153A:小数N频率合成器数据表2021-04-29 831

-

ADF4153:小数N分频频率合成器2021-03-21 1640

-

ADF4159:直接调制/快速波形产生13 GHz小数N分频频率合成器2021-03-20 1233

-

UG-167:针对ADF4153小数N分频PLL频率合成器的评估板2021-03-19 1268

-

评估ADF4153A频率合成器的性能的EV-ADF4153ASD1Z评估板2019-02-27 2707

-

ADF4153A 小数N分频频率合成器2019-02-22 444

-

ADI发布相位噪声性能的PLL频率合成器ADF4153A2012-11-01 6177

全部0条评论

快来发表一下你的评论吧 !